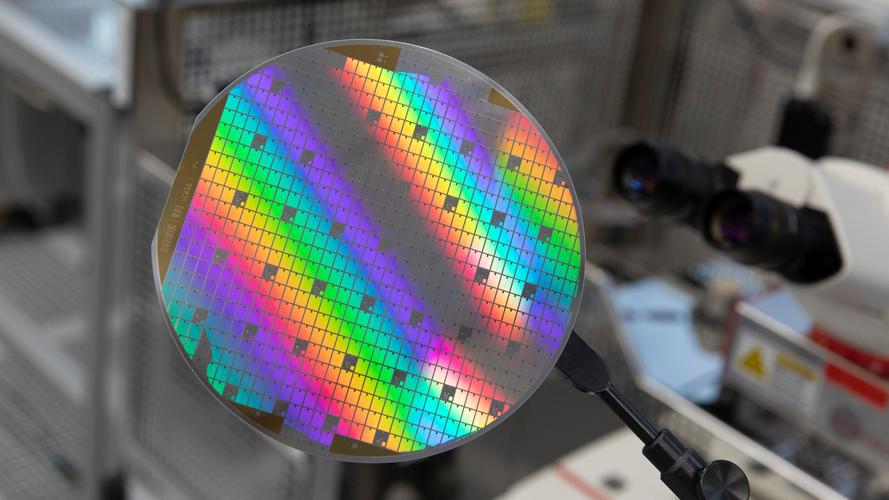

Die Produktlinie von VET Energy ist nicht auf GaN auf SiC-Wafern beschränkt. Wir bieten auch eine breite Palette von Halbleitersubstratmaterialien an, darunter Si-Wafer, SiC-Substrat, SOI-Wafer, SiN-Substrat, Epi-Wafer usw. Darüber hinaus entwickeln wir aktiv neue Halbleitermaterialien mit großer Bandlücke, wie Galliumoxid Ga2O3 und AlN Wafer, um den zukünftigen Bedarf der Leistungselektronikindustrie an leistungsstärkeren Geräten zu decken.

VET Energy bietet flexible Anpassungsdienste und kann GaN-Epitaxieschichten unterschiedlicher Dicke, unterschiedlicher Dotierungsarten und unterschiedlicher Wafergrößen entsprechend den spezifischen Anforderungen der Kunden anpassen. Darüber hinaus bieten wir professionellen technischen Support und Kundendienst, um Kunden bei der schnellen Entwicklung leistungsstarker leistungselektronischer Geräte zu unterstützen.

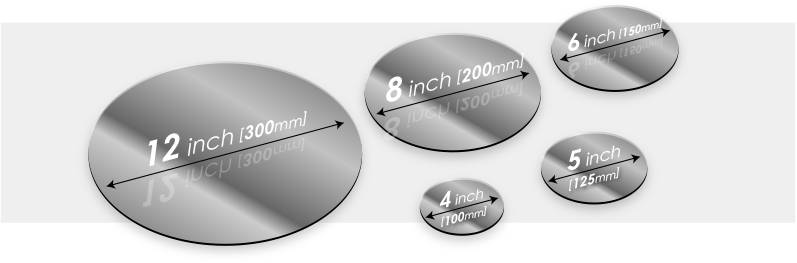

WAFERING-SPEZIFIKATIONEN

*n-Pm=n-Typ Pm-Qualität, n-Ps=n-Typ Ps-Qualität, Sl=halbisolierend

| Artikel | 8 Zoll | 6 Zoll | 4 Zoll | ||

| nP | n-Pm | n-Ps | SI | SI | |

| TTV(GBIR) | ≤6um | ≤6um | |||

| Bow(GF3YFCD) – Absoluter Wert | ≤15μm | ≤15μm | ≤25μm | ≤15μm | |

| Warp(GF3YFER) | ≤25μm | ≤25μm | ≤40μm | ≤25μm | |

| LTV(SBIR)-10mmx10mm | <2μm | ||||

| Waferkante | Abschrägung | ||||

OBERFLÄCHENVERARBEITUNG

*n-Pm=n-Typ Pm-Qualität, n-Ps=n-Typ Ps-Qualität, Sl=halbisolierend

| Artikel | 8 Zoll | 6 Zoll | 4 Zoll | ||

| nP | n-Pm | n-Ps | SI | SI | |

| Oberflächenbeschaffenheit | Doppelseitige optische Politur, Si-Face CMP | ||||

| Oberflächenrauheit | (10 um x 10 um) Si-FaceRa≤0,2 nm | (5 um x 5 um) Si-Oberfläche Ra≤0,2 nm | |||

| Kantensplitter | Nicht zulässig (Länge und Breite ≥ 0,5 mm) | ||||

| Einrückungen | Nichts erlaubt | ||||

| Kratzer (Si-Face) | Menge ≤ 5, kumulativ | Menge ≤ 5, kumulativ | Menge ≤ 5, kumulativ | ||

| Risse | Nichts erlaubt | ||||

| Kantenausschluss | 3mm | ||||

-

Maßgeschneiderte Graphitheizung für Heißzonen/Graphi...

-

Graphit-Magnetpumpen-Gleitlager verschleißfest ...

-

Rekristallisiertes Siliziumkarbid-Wafer-Boot mit ...

-

1 kW Sofc-Hochtemperatur-Wasserstoffbrennstoffzelle

-

Brennstoffzelle 1000 W 24 V Drohne Wasserstoff-Brennstoffzellen-Kit

-

Wasserstoff-Brennstoffzelle und Speicher-Wasserstoff-Brennstoffzelle ...