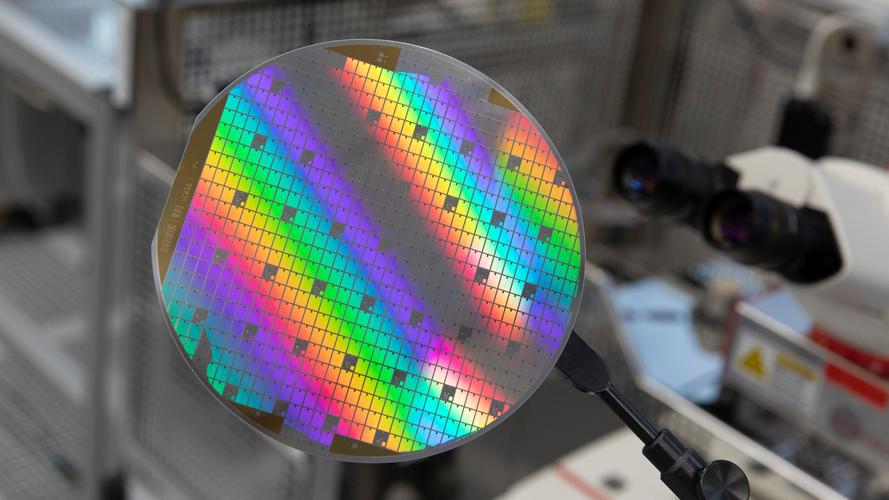

Dieser 6-Zoll-SiC-Wafer vom Typ N wurde für eine verbesserte Leistung unter extremen Bedingungen entwickelt und ist somit die ideale Wahl für Anwendungen, die eine hohe Leistungs- und Temperaturbeständigkeit erfordern. Zu den mit diesem Wafer verbundenen Schlüsselprodukten gehören Si-Wafer, SiC-Substrat, SOI-Wafer und SiN-Substrat. Diese Materialien gewährleisten eine optimale Leistung in einer Vielzahl von Halbleiterherstellungsprozessen und ermöglichen Geräte, die sowohl energieeffizient als auch langlebig sind.

Für Unternehmen, die mit Epi-Wafern, Galliumoxid-Ga2O3-, Kassetten- oder AlN-Wafern arbeiten, bietet der 6-Zoll-N-Typ-SiC-Wafer von VET Energy die notwendige Grundlage für die innovative Produktentwicklung. Ob in der Hochleistungselektronik oder der neuesten HF-Technologie – diese Wafer gewährleisten eine hervorragende Leitfähigkeit und einen minimalen Wärmewiderstand und verschieben damit die Grenzen von Effizienz und Leistung.

WAFERING-SPEZIFIKATIONEN

*n-Pm=n-Typ Pm-Qualität, n-Ps=n-Typ Ps-Qualität, Sl=halbisolierend

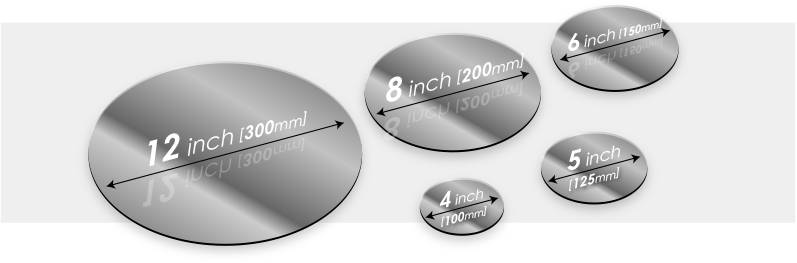

| Artikel | 8 Zoll | 6 Zoll | 4 Zoll | ||

| nP | n-Pm | n-Ps | SI | SI | |

| TTV(GBIR) | ≤6um | ≤6um | |||

| Bow(GF3YFCD) – Absoluter Wert | ≤15μm | ≤15μm | ≤25μm | ≤15μm | |

| Warp(GF3YFER) | ≤25μm | ≤25μm | ≤40μm | ≤25μm | |

| LTV(SBIR)-10mmx10mm | <2μm | ||||

| Waferkante | Abschrägung | ||||

OBERFLÄCHENVERARBEITUNG

*n-Pm=n-Typ Pm-Qualität, n-Ps=n-Typ Ps-Qualität, Sl=halbisolierend

| Artikel | 8 Zoll | 6 Zoll | 4 Zoll | ||

| nP | n-Pm | n-Ps | SI | SI | |

| Oberflächenbeschaffenheit | Doppelseitige optische Politur, Si-Face CMP | ||||

| Oberflächenrauheit | (10 um x 10 um) Si-FaceRa≤0,2 nm | (5 um x 5 um) Si-Oberfläche Ra≤0,2 nm | |||

| Kantensplitter | Nicht zulässig (Länge und Breite ≥ 0,5 mm) | ||||

| Einrückungen | Nichts erlaubt | ||||

| Kratzer (Si-Face) | Menge ≤ 5, kumulativ | Menge ≤ 5, kumulativ | Menge ≤ 5, kumulativ | ||

| Risse | Nichts erlaubt | ||||

| Kantenausschluss | 3mm | ||||

-

RTP/RTA SiC-Beschichtungsträger für MOCVD-Epitaxie...

-

Wasserstoffbatterie PEM-Brennstoffzelle Mea-Elektrode As ...

-

12-Zoll-Siliziumwafer für die Halbleiterfertigung ...

-

Brennstoffzelle, spezielle Vorrichtung zum Testen der Leistung...

-

Kordel, gedrehtes, geflochtenes Kohlefaserseil

-

Metall-Wasserstoff-Brennstoffzellen 1000 W Pemfc-Stapel für ...