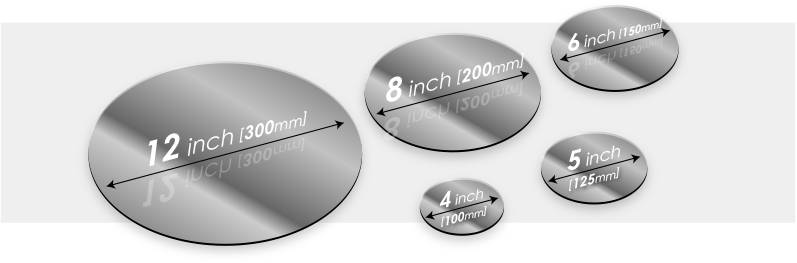

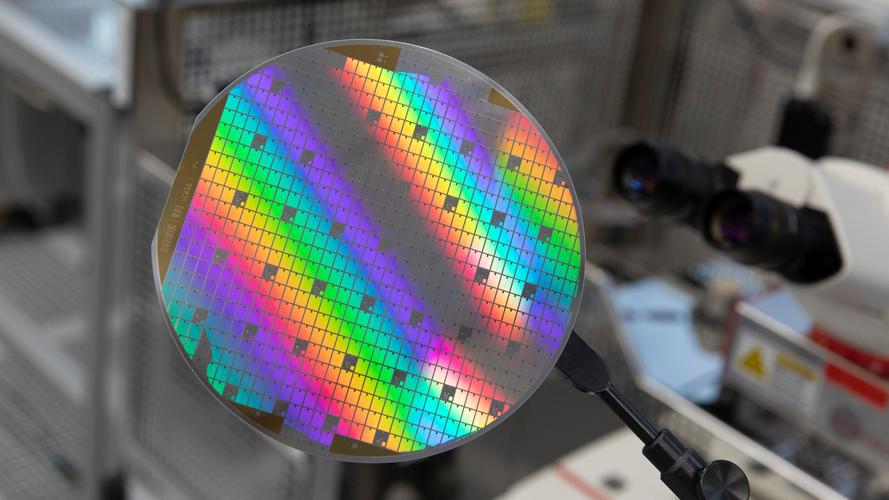

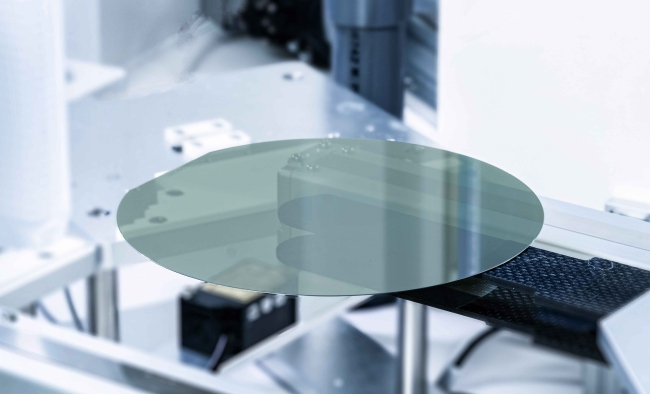

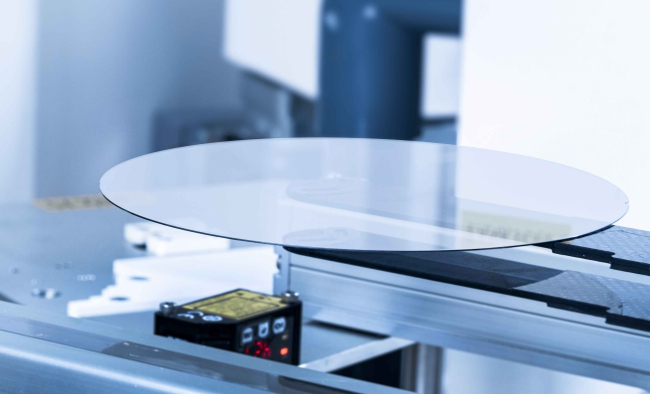

Den 12 tommer siliciumwafer til halvlederfremstilling, der tilbydes af VET Energy, er konstrueret til at opfylde de præcise standarder, der kræves i halvlederindustrien. Som et af de førende produkter i vores sortiment sikrer VET Energy, at disse wafere er produceret med præcis fladhed, renhed og overfladekvalitet, hvilket gør dem ideelle til banebrydende halvlederapplikationer, herunder mikrochips, sensorer og avancerede elektroniske enheder.

Denne wafer er kompatibel med en lang række materialer såsom Si Wafer, SiC Substrate, SOI Wafer, SiN Substrate og Epi Wafer, hvilket giver fremragende alsidighed til forskellige fremstillingsprocesser. Derudover parrer det godt med avancerede teknologier som Gallium Oxide Ga2O3 og AlN Wafer, hvilket sikrer, at det kan integreres i højt specialiserede applikationer. For jævn drift er waferen optimeret til brug med industristandard kassettesystemer, hvilket sikrer effektiv håndtering i halvlederfremstilling.

VET Energy's produktlinje er ikke begrænset til siliciumwafers. Vi leverer også en bred vifte af halvledersubstratmaterialer, herunder SiC Substrate, SOI Wafer, SiN Substrate, Epi Wafer, etc., samt nye wide bandgap halvledermaterialer såsom Gallium Oxide Ga2O3 og AlN Wafer. Disse produkter kan opfylde forskellige kunders applikationsbehov inden for kraftelektronik, radiofrekvens, sensorer og andre områder.

Anvendelsesområder:

•Logiske chips:Fremstilling af højtydende logiske chips såsom CPU og GPU.

•Hukommelseschips:Fremstilling af hukommelseschips såsom DRAM og NAND Flash.

•Analoge chips:Fremstilling af analoge chips såsom ADC og DAC.

•Sensorer:MEMS-sensorer, billedsensorer mv.

VET Energy giver kunderne skræddersyede waferløsninger og kan tilpasse wafers med forskellig modstand, forskelligt iltindhold, forskellig tykkelse og andre specifikationer i henhold til kundernes specifikke behov. Derudover yder vi også professionel teknisk support og eftersalgsservice for at hjælpe kunder med at optimere produktionsprocesser og forbedre produktudbyttet.

WAFERING SPECIFIKATIONER

*n-Pm=n-type Pm-Grade,n-Ps=n-type Ps-Grade,Sl=semi-isolerende

| Punkt | 8-tommer | 6-tommer | 4-tommer | ||

| nP | n-Pm | n-Ps | SI | SI | |

| TTV (GBIR) | ≤6um | ≤6um | |||

| Bow(GF3YFCD)-absolut værdi | ≤15μm | ≤15μm | ≤25μm | ≤15μm | |

| Warp (GF3YFER) | ≤25μm | ≤25μm | ≤40μm | ≤25μm | |

| LTV(SBIR)-10mmx10mm | <2μm | ||||

| Wafer Edge | Affasning | ||||

OVERFLADE AFSLUTNING

*n-Pm=n-type Pm-Grade,n-Ps=n-type Ps-Grade,Sl=semi-isolerende

| Punkt | 8-tommer | 6-tommer | 4-tommer | ||

| nP | n-Pm | n-Ps | SI | SI | |

| Overfladefinish | Dobbeltsidet optisk polsk, Si-Face CMP | ||||

| Overfladeruhed | (10um x 10um) Si-FaceRa≤0,2nm | (5umx5um) Si-Face Ra≤0,2nm | |||

| Edge Chips | Ingen tilladt (længde og bredde≥0,5 mm) | ||||

| Indrykninger | Ingen tilladt | ||||

| Ridser (Si-Face) | Antal.≤5, kumulativ | Antal.≤5, kumulativ | Antal.≤5, kumulativ | ||

| Revner | Ingen tilladt | ||||

| Kantudelukkelse | 3 mm | ||||