Lắng đọng màng mỏng là phủ một lớp màng lên vật liệu nền chính của chất bán dẫn. Lớp màng này có thể được làm từ nhiều loại vật liệu khác nhau, chẳng hạn như hợp chất cách điện silicon dioxide, polysilicon bán dẫn, kim loại đồng, v.v. Thiết bị dùng để phủ được gọi là thiết bị lắng đọng màng mỏng.

Theo quan điểm của quy trình sản xuất chip bán dẫn, nó nằm ở quy trình đầu cuối.

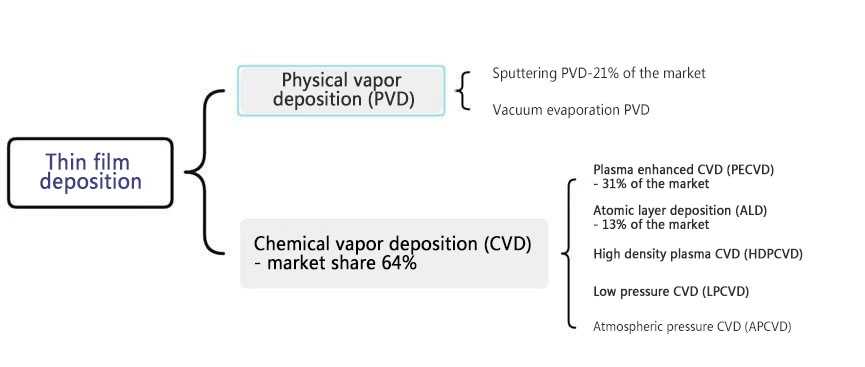

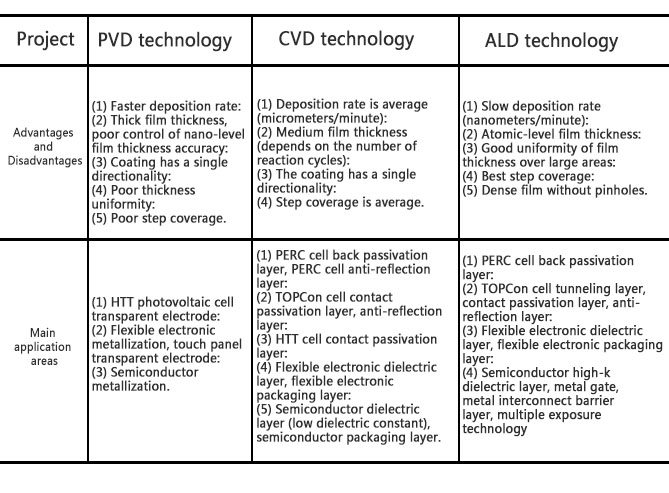

Quá trình chế tạo màng mỏng có thể được chia thành hai loại theo phương pháp tạo màng: lắng đọng hơi vật lý (PVD) và lắng đọng hơi hóa học(CVD), trong đó thiết bị xử lý CVD chiếm tỷ lệ cao hơn.

Lắng đọng hơi vật lý (PVD) là quá trình bốc hơi bề mặt của nguồn vật liệu và lắng đọng trên bề mặt của chất nền thông qua khí/plasma áp suất thấp, bao gồm bốc hơi, phun, chùm ion, v.v.;

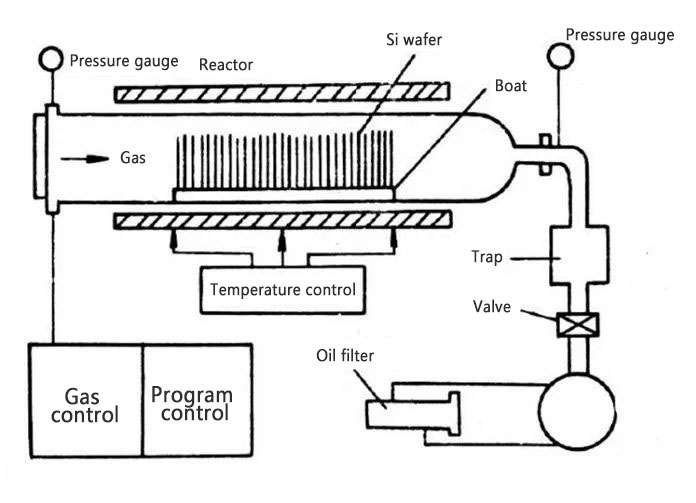

Lắng đọng hơi hóa học (CVD) là quá trình lắng đọng một lớp màng rắn trên bề mặt của tấm silicon thông qua phản ứng hóa học của hỗn hợp khí. Theo điều kiện phản ứng (áp suất, tiền chất), nó được chia thành áp suất khí quyểnCVD(APCVD), áp suất thấpCVD(LPCVD), CVD tăng cường plasma (PECVD), CVD plasma mật độ cao (HDPCVD) và lắng đọng lớp nguyên tử (ALD).

LPCVD: LPCVD có khả năng bao phủ bước tốt hơn, kiểm soát thành phần và cấu trúc tốt, tỷ lệ lắng đọng và sản lượng cao, và giảm đáng kể nguồn ô nhiễm hạt. Dựa vào thiết bị gia nhiệt làm nguồn nhiệt để duy trì phản ứng, kiểm soát nhiệt độ và áp suất khí rất quan trọng. Được sử dụng rộng rãi trong sản xuất lớp Poly của pin TopCon.

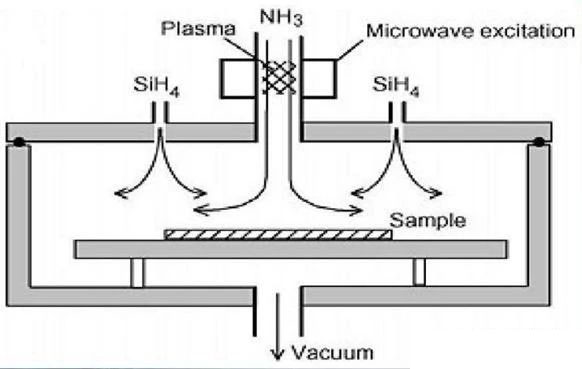

PECVD: PECVD dựa vào plasma được tạo ra bởi cảm ứng tần số vô tuyến để đạt được nhiệt độ thấp (dưới 450 độ) của quá trình lắng đọng màng mỏng. Lắng đọng ở nhiệt độ thấp là ưu điểm chính của nó, do đó tiết kiệm năng lượng, giảm chi phí, tăng năng suất sản xuất và giảm sự suy giảm tuổi thọ của các hạt mang điện thiểu số trong các tấm wafer silicon do nhiệt độ cao gây ra. Nó có thể được áp dụng cho các quy trình của nhiều loại ô khác nhau như PERC, TOPCON và HJT.

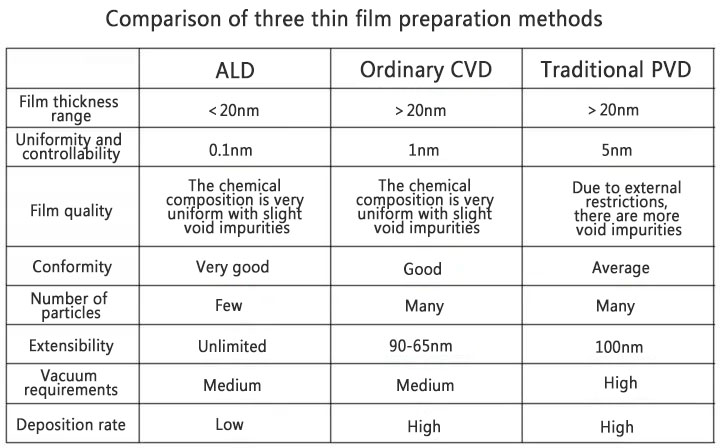

ALD: Độ đồng đều của màng tốt, dày đặc và không có lỗ, đặc tính phủ bước tốt, có thể thực hiện ở nhiệt độ thấp (nhiệt độ phòng - 400℃), có thể kiểm soát độ dày màng một cách đơn giản và chính xác, có thể áp dụng rộng rãi cho các chất nền có hình dạng khác nhau và không cần kiểm soát độ đồng đều của dòng chất phản ứng. Nhưng nhược điểm là tốc độ hình thành màng chậm. Chẳng hạn như lớp phát sáng kẽm sunfua (ZnS) được sử dụng để sản xuất chất cách điện có cấu trúc nano (Al2O3/TiO2) và màn hình phát quang điện màng mỏng (TFEL).

Lắng đọng lớp nguyên tử (ALD) là một quá trình phủ chân không tạo thành một lớp màng mỏng trên bề mặt của chất nền theo từng lớp dưới dạng một lớp nguyên tử đơn. Ngay từ năm 1974, nhà vật lý vật liệu người Phần Lan Tuomo Suntola đã phát triển công nghệ này và giành được Giải thưởng Công nghệ Thiên niên kỷ trị giá 1 triệu euro. Công nghệ ALD ban đầu được sử dụng cho màn hình phát quang điện tử phẳng, nhưng nó không được sử dụng rộng rãi. Phải đến đầu thế kỷ 21, công nghệ ALD mới bắt đầu được ngành công nghiệp bán dẫn áp dụng. Bằng cách sản xuất vật liệu điện môi cao siêu mỏng để thay thế oxit silic truyền thống, nó đã giải quyết thành công vấn đề dòng điện rò rỉ do việc giảm độ rộng đường dây của bóng bán dẫn hiệu ứng trường, thúc đẩy Định luật Moore phát triển hơn nữa theo hướng có độ rộng đường dây nhỏ hơn. Tiến sĩ Tuomo Suntola đã từng nói rằng ALD có thể làm tăng đáng kể mật độ tích hợp của các thành phần.

Dữ liệu công khai cho thấy công nghệ ALD được Tiến sĩ Tuomo Suntola của PICOSUN tại Phần Lan phát minh vào năm 1974 và đã được công nghiệp hóa ở nước ngoài, chẳng hạn như màng điện môi cao trong chip 45/32 nanomet do Intel phát triển. Ở Trung Quốc, đất nước tôi đã giới thiệu công nghệ ALD muộn hơn 30 năm so với các nước ngoài. Vào tháng 10 năm 2010, PICOSUN tại Phần Lan và Đại học Fudan đã tổ chức cuộc họp trao đổi học thuật ALD trong nước đầu tiên, giới thiệu công nghệ ALD lần đầu tiên đến Trung Quốc.

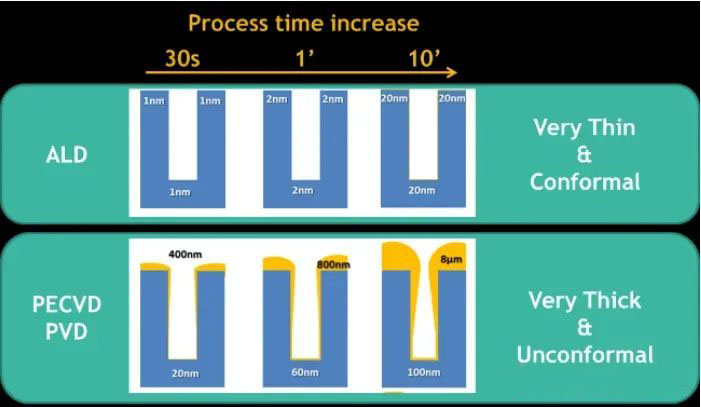

So với phương pháp lắng đọng hơi hóa học truyền thống (CVD) và lắng đọng hơi vật lý (PVD), ưu điểm của ALD là tính phù hợp ba chiều tuyệt vời, tính đồng nhất của màng trên diện tích lớn và kiểm soát độ dày chính xác, phù hợp để phát triển màng siêu mỏng trên các hình dạng bề mặt phức tạp và cấu trúc có tỷ lệ khung hình cao.

—Nguồn dữ liệu: Nền tảng xử lý micro-nano của Đại học Thanh Hoa—

Trong kỷ nguyên hậu Moore, tính phức tạp và khối lượng quy trình sản xuất wafer đã được cải thiện rất nhiều. Lấy chip logic làm ví dụ, với sự gia tăng số lượng dây chuyền sản xuất có quy trình dưới 45nm, đặc biệt là các dây chuyền sản xuất có quy trình 28nm trở xuống, các yêu cầu về độ dày lớp phủ và kiểm soát độ chính xác cao hơn. Sau khi giới thiệu công nghệ phơi sáng nhiều lần, số lượng các bước quy trình ALD và thiết bị cần thiết đã tăng lên đáng kể; trong lĩnh vực chip nhớ, quy trình sản xuất chính thống đã phát triển từ cấu trúc NAND 2D sang cấu trúc NAND 3D, số lượng lớp bên trong tiếp tục tăng và các thành phần đã dần trình bày các cấu trúc mật độ cao, tỷ lệ khung hình cao và vai trò quan trọng của ALD đã bắt đầu xuất hiện. Theo quan điểm phát triển tương lai của chất bán dẫn, công nghệ ALD sẽ đóng vai trò ngày càng quan trọng trong kỷ nguyên hậu Moore.

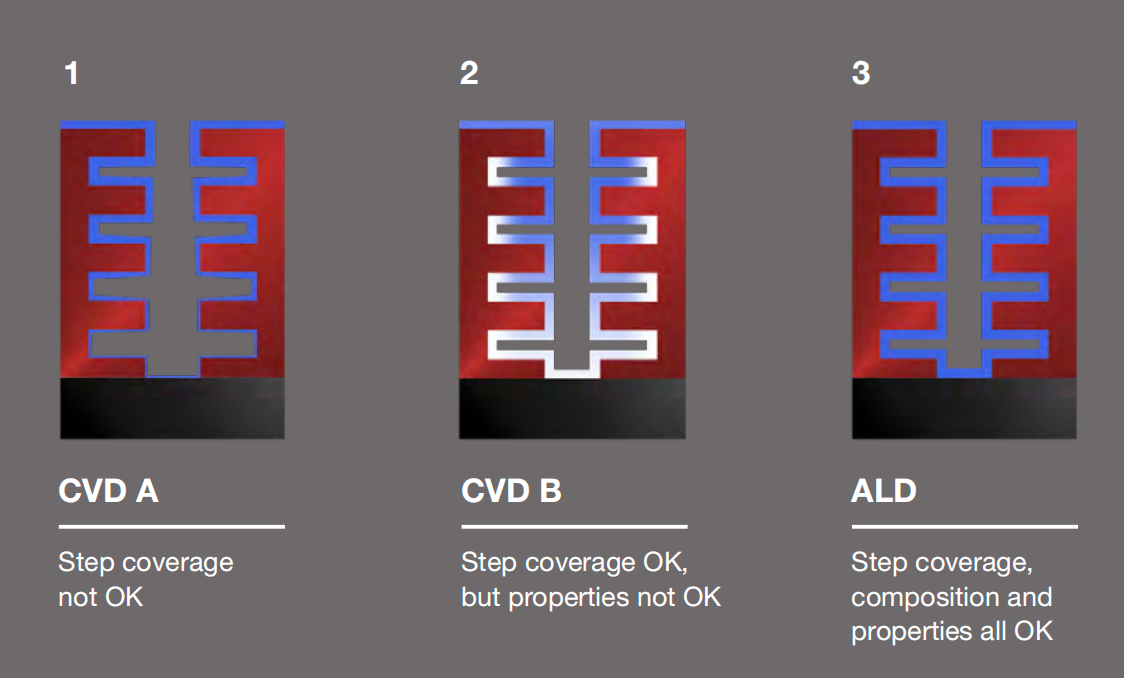

Ví dụ, ALD là công nghệ lắng đọng duy nhất có thể đáp ứng các yêu cầu về độ phủ và hiệu suất màng của các cấu trúc xếp chồng 3D phức tạp (như 3D-NAND). Điều này có thể được thấy rõ trong hình bên dưới. Màng được lắng đọng trong CVD A (màu xanh) không phủ hoàn toàn phần dưới của cấu trúc; ngay cả khi một số điều chỉnh quy trình được thực hiện đối với CVD (CVD B) để đạt được độ phủ, hiệu suất màng và thành phần hóa học của khu vực đáy vẫn rất kém (khu vực màu trắng trong hình); ngược lại, việc sử dụng công nghệ ALD cho thấy độ phủ màng hoàn toàn và đạt được các đặc tính màng chất lượng cao và đồng đều ở mọi khu vực của cấu trúc.

—-Hình ảnh Ưu điểm của công nghệ ALD so với CVD (Nguồn: ASM)—-

Mặc dù CVD vẫn chiếm thị phần lớn nhất trong ngắn hạn, ALD đã trở thành một trong những bộ phận phát triển nhanh nhất của thị trường thiết bị chế tạo wafer. Trong thị trường ALD này với tiềm năng tăng trưởng lớn và vai trò quan trọng trong sản xuất chip, ASM là công ty hàng đầu trong lĩnh vực thiết bị ALD.

Thời gian đăng: 12-06-2024