As dificuldades técnicas na produção em massa estável de wafers de carboneto de silício de alta qualidade com desempenho estável incluem:

1) Como os cristais precisam crescer em um ambiente selado de alta temperatura acima de 2000°C, os requisitos de controle de temperatura são extremamente altos;

2) Como o carboneto de silício possui mais de 200 estruturas cristalinas, mas apenas algumas estruturas de carboneto de silício monocristalino são os materiais semicondutores necessários, a relação silício-carbono, o gradiente de temperatura de crescimento e o crescimento do cristal precisam ser controlados com precisão durante o processo de crescimento do cristal. Parâmetros como velocidade e pressão do fluxo de ar;

3) Sob o método de transmissão de fase de vapor, a tecnologia de expansão de diâmetro do crescimento de cristais de carboneto de silício é extremamente difícil;

4) A dureza do carboneto de silício é próxima à do diamante, e as técnicas de corte, retificação e polimento são difíceis.

Wafers epitaxiais de SiC: geralmente fabricados pelo método de deposição química de vapor (CVD). De acordo com os diferentes tipos de dopagem, são divididos em wafers epitaxiais do tipo n e do tipo p. As empresas nacionais Hantian Tiancheng e Dongguan Tianyu já fornecem wafers epitaxiais de SiC de 4/6 polegadas. A epitaxia de SiC é difícil de controlar no campo de alta tensão, e a qualidade da epitaxia de SiC tem um impacto maior nos dispositivos de SiC. Além disso, os equipamentos epitaxiais são monopolizados pelas quatro principais empresas do setor: Axitron, LPE, TEL e Nuflare.

Carboneto de silício epitaxialWafer refere-se a um wafer de carboneto de silício no qual uma película de cristal único (camada epitaxial) com certos requisitos e os mesmos que o cristal do substrato é cultivada no substrato de carboneto de silício original. O crescimento epitaxial utiliza principalmente equipamentos CVD (Deposição Química de Vapor) ou MBE (Epitaxia por Feixe Molecular). Como os dispositivos de carboneto de silício são fabricados diretamente na camada epitaxial, a qualidade da camada epitaxial afeta diretamente o desempenho e o rendimento do dispositivo. À medida que o desempenho de resistência à tensão do dispositivo continua a aumentar, a espessura da camada epitaxial correspondente torna-se mais espessa e o controle torna-se mais difícil. Geralmente, quando a tensão está em torno de 600 V, a espessura da camada epitaxial necessária é de cerca de 6 mícrons; quando a tensão está entre 1200-1700 V, a espessura da camada epitaxial necessária atinge 10-15 mícrons. Se a tensão atingir mais de 10.000 volts, pode ser necessária uma espessura de camada epitaxial superior a 100 mícrons. À medida que a espessura da camada epitaxial aumenta, torna-se cada vez mais difícil controlar a uniformidade da espessura e da resistividade, bem como a densidade de defeitos.

Dispositivos de SiC: Internacionalmente, SBDs e MOSFETs de SiC de 600 a 1700 V foram industrializados. Os produtos convencionais operam em tensões abaixo de 1200 V e adotam principalmente encapsulamento TO. Em termos de preço, os produtos de SiC no mercado internacional têm preços cerca de 5 a 6 vezes maiores que os de Si equivalentes. No entanto, os preços estão caindo a uma taxa anual de 10%. Com a expansão dos materiais upstream e da produção de dispositivos nos próximos 2 a 3 anos, a oferta no mercado aumentará, levando a novas reduções de preço. Espera-se que, quando o preço atingir 2 a 3 vezes o dos produtos de Si, as vantagens proporcionadas pela redução dos custos do sistema e pelo desempenho aprimorado levarão gradualmente o SiC a ocupar o espaço de mercado dos dispositivos de Si.

O encapsulamento tradicional é baseado em substratos à base de silício, enquanto os materiais semicondutores de terceira geração exigem um design completamente novo. O uso de estruturas de encapsulamento tradicionais à base de silício para dispositivos de energia com banda larga pode introduzir novos problemas e desafios relacionados à frequência, gerenciamento térmico e confiabilidade. Dispositivos de energia de SiC são mais sensíveis à capacitância e indutância parasitas. Comparados aos dispositivos de SiC, os chips de energia de SiC têm velocidades de comutação mais rápidas, o que pode levar a overshoot, oscilação, maiores perdas de comutação e até mesmo mau funcionamento do dispositivo. Além disso, dispositivos de energia de SiC operam em temperaturas mais altas, exigindo técnicas de gerenciamento térmico mais avançadas.

Diversas estruturas diferentes foram desenvolvidas no campo de encapsulamento de semicondutores de banda larga. O encapsulamento tradicional de módulos de potência à base de Si não é mais adequado. Para solucionar os problemas de altos parâmetros parasitários e baixa eficiência de dissipação de calor do encapsulamento tradicional de módulos de potência à base de Si, o encapsulamento de módulos de potência de SiC adota interconexão sem fio e tecnologia de resfriamento de dupla face em sua estrutura, além de materiais de substrato com melhor condutividade térmica, buscando integrar capacitores de desacoplamento, sensores de temperatura/corrente e circuitos de acionamento à estrutura do módulo, desenvolvendo uma variedade de diferentes tecnologias de encapsulamento de módulos. Além disso, existem altas barreiras técnicas para a fabricação de dispositivos de SiC e os custos de produção são elevados.

Dispositivos de carboneto de silício são produzidos pela deposição de camadas epitaxiais sobre um substrato de carboneto de silício por CVD. O processo envolve limpeza, oxidação, fotolitografia, corrosão, remoção da fotorresistência, implantação iônica, deposição química de vapor de nitreto de silício, polimento, pulverização catódica e etapas subsequentes de processamento para formar a estrutura do dispositivo no substrato de cristal único de SiC. Os principais tipos de dispositivos de potência de SiC incluem diodos de SiC, transistores de SiC e módulos de potência de SiC. Devido a fatores como baixa velocidade de produção do material a montante e baixas taxas de rendimento, os dispositivos de carboneto de silício apresentam custos de fabricação relativamente altos.

Além disso, a fabricação de dispositivos de carboneto de silício apresenta certas dificuldades técnicas:

1) É necessário desenvolver um processo específico que seja consistente com as características dos materiais de carboneto de silício. Por exemplo: o SiC possui um alto ponto de fusão, o que torna a difusão térmica tradicional ineficaz. É necessário utilizar o método de dopagem por implantação iônica e controlar com precisão parâmetros como temperatura, taxa de aquecimento, duração e fluxo de gás; o SiC é inerte a solventes químicos. Métodos como corrosão a seco devem ser utilizados, e materiais de máscara, misturas de gases, controle da inclinação da parede lateral, taxa de corrosão, rugosidade da parede lateral, etc., devem ser otimizados e desenvolvidos.

2) A fabricação de eletrodos metálicos em wafers de carboneto de silício requer uma resistência de contato inferior a 10-5Ω². Os materiais de eletrodo que atendem a esses requisitos, Ni e Al, apresentam baixa estabilidade térmica acima de 100°C, mas o Al/Ni apresenta melhor estabilidade térmica. A resistência de contato específica do material de eletrodo composto de /W/Au é 10-3Ω² maior;

3) O SiC apresenta alto desgaste de corte e sua dureza só fica atrás do diamante, o que impõe requisitos mais elevados para corte, retificação, polimento e outras tecnologias.

Além disso, os dispositivos de potência de carboneto de silício de trincheira são mais difíceis de fabricar. De acordo com diferentes estruturas de dispositivo, os dispositivos de potência de carboneto de silício podem ser divididos principalmente em dispositivos planares e dispositivos de trincheira. Os dispositivos de potência de carboneto de silício planares têm boa consistência de unidade e processo de fabricação simples, mas são propensos ao efeito JFET e têm alta capacitância parasita e resistência no estado ligado. Comparados com dispositivos planares, os dispositivos de potência de carboneto de silício de trincheira têm menor consistência de unidade e têm um processo de fabricação mais complexo. No entanto, a estrutura de trincheira é propícia ao aumento da densidade de unidades do dispositivo e é menos provável que produza o efeito JFET, o que é benéfico para resolver o problema da mobilidade do canal. Possui excelentes propriedades, como pequena resistência ligada, pequena capacitância parasita e baixo consumo de energia de comutação. Tem vantagens significativas de custo e desempenho e se tornou a direção principal do desenvolvimento de dispositivos de potência de carboneto de silício. De acordo com o site oficial da Rohm, a estrutura ROHM Gen3 (estrutura Gen1 Trench) representa apenas 75% da área do chip Gen2 (Plannar2), e a resistência da estrutura ROHM Gen3 é reduzida em 50% no mesmo tamanho de chip.

Substrato de carboneto de silício, epitaxia, front-end, despesas de P&D e outros são responsáveis por 47%, 23%, 19%, 6% e 5% do custo de fabricação de dispositivos de carboneto de silício, respectivamente.

Por fim, vamos nos concentrar em quebrar as barreiras técnicas dos substratos na cadeia da indústria de carboneto de silício.

O processo de produção de substratos de carboneto de silício é semelhante ao de substratos à base de silício, mas mais difícil.

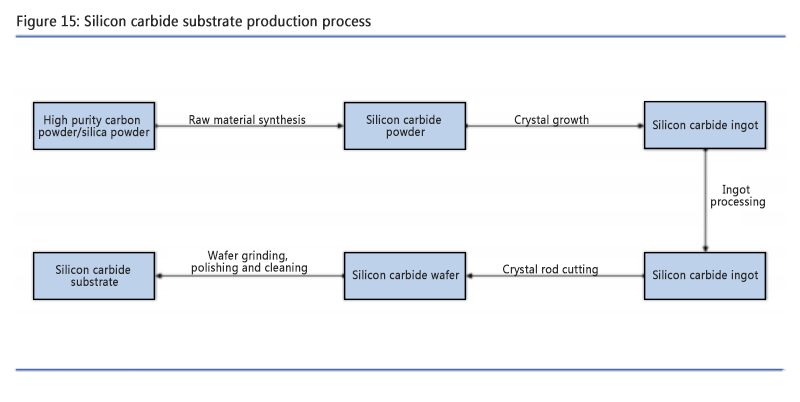

O processo de fabricação do substrato de carboneto de silício geralmente inclui síntese de matéria-prima, crescimento de cristal, processamento de lingotes, corte de lingotes, moagem de wafers, polimento, limpeza e outros elos.

O estágio de crescimento do cristal é o núcleo de todo o processo, e esta etapa determina as propriedades elétricas do substrato de carboneto de silício.

Materiais de carboneto de silício são difíceis de crescer na fase líquida em condições normais. O método de crescimento em fase de vapor, popular no mercado hoje, tem uma temperatura de crescimento acima de 2300 °C e requer um controle preciso da temperatura de crescimento. Todo o processo operacional é quase difícil de observar. Um pequeno erro levará ao descarte do produto. Em comparação, os materiais de silício requerem apenas 1600 °C, o que é muito menor. A preparação de substratos de carboneto de silício também enfrenta dificuldades, como crescimento lento do cristal e altos requisitos de forma do cristal. O crescimento da pastilha de carboneto de silício leva cerca de 7 a 10 dias, enquanto a extração da haste de silício leva apenas 2 dias e meio. Além disso, o carboneto de silício é um material cuja dureza fica atrás apenas do diamante. Ele perderá muito durante o corte, retificação e polimento, e a taxa de produção é de apenas 60%.

Sabemos que a tendência é aumentar o tamanho dos substratos de carboneto de silício. À medida que o tamanho aumenta, os requisitos para a tecnologia de expansão de diâmetro tornam-se cada vez maiores. É necessária uma combinação de vários elementos de controle técnico para alcançar o crescimento iterativo dos cristais.

Horário de publicação: 22 de maio de 2024