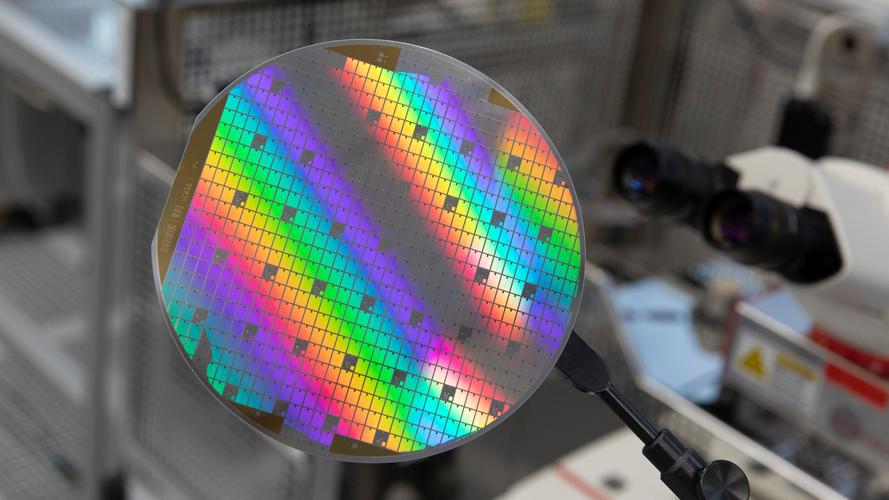

De 6 Zoll Hallefisoléierende SiC-Wafer vu VET Energy ass eng fortgeschratt Léisung fir Héichleistungs- an Héichfrequenzapplikatiounen, déi eng iwwerleeën Wärmeleitfäegkeet an elektresch Isolatioun bitt. Dës Hallefisoléierend Wafere si wesentlech fir d'Entwécklung vun Apparater wéi HF-Verstärker, Stroumschalter an aner Héichspannungskomponenten. VET Energy garantéiert eng konsequent Qualitéit a Leeschtung, wouduerch dës Wafere ideal fir eng breet Palette vu Hallefleederfabrikatiounsprozesser sinn.

Nieft hiren aussergewéinleche Isolatiounseigenschaften sinn dës SiC-Wafers kompatibel mat enger Villfalt vu Materialien, dorënner Si-Wafer, SiC-Substrat, SOI-Wafer, SiN-Substrat an Epi-Wafer, wat se villfälteg fir verschidden Aarte vu Produktiounsprozesser mécht. Ausserdeem kënnen fortgeschratt Materialien wéi Galliumoxid Ga2O3 an AlN-Wafer a Kombinatioun mat dëse SiC-Wafers benotzt ginn, wat nach méi Flexibilitéit an elektroneschen Apparater mat héijer Leeschtung bitt. D'Wafers sinn fir eng nahtlos Integratioun mat Industriestandard-Handhabungssystemer wéi Kassettesystemer entwéckelt, wat eng einfach Benotzung a Masseproduktioun garantéiert.

VET Energy bitt e komplette Portfolio vu Hallefleedersubstrater, dorënner Si Wafer, SiC Substrat, SOI Wafer, SiN Substrat, Epi Wafer, Galliumoxid Ga2O3 an AlN Wafer. Eis divers Produktpalette entsprécht de Bedierfnesser vu verschiddenen elektroneschen Uwendungen, vun der Leeschtungselektronik bis hin zu HF an Optoelektronik.

6 Zoll Hallefisolatiouns-SiC-Wafer bitt verschidde Virdeeler:

Héich Duerchbrochspannung: Déi grouss Bandlück vum SiC erméiglecht méi héich Duerchbrochspannungen, wat méi kompakt an effizient Energieversuergungsapparater erméiglecht.

Betrib bei héijen Temperaturen: Déi exzellent thermesch Leetfäegkeet vu SiC erméiglecht de Betrib bei méi héijen Temperaturen, wat d'Zouverlässegkeet vum Apparat verbessert.

Niddrege Schaltwidderstand: SiC-Apparater weisen e méi niddrege Schaltwidderstand op, wat d'Energieverloschter reduzéiert an d'Energieeffizienz verbessert.

VET Energy bitt personaliséierbar SiC-Waferen un, déi Äre spezifesche Bedierfnesser gerecht ginn, dorënner verschidden Dicken, Dotierungsgraden an Uewerflächenofschloss. Eis Expertenéquipe bitt techneschen Support a Service no Verkaf, fir Ären Erfolleg ze garantéieren.

WAFEREN-SPECIFIKATIOUNEN

*n-Pm=n-Typ Pm-Grad, n-Ps=n-Typ Ps-Grad, Sl=Hallefisoléierend

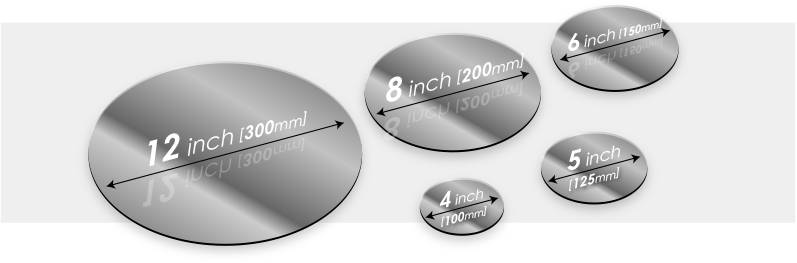

| Artikel | 8-Zoll | 6-Zoll | 4-Zoll | ||

| nP | n-Pm | n-Ps | SI | SI | |

| TTV(GBIR) | ≤6µm | ≤6µm | |||

| Béi(GF3YFCD) - Absolutwäert | ≤15μm | ≤15μm | ≤25μm | ≤15μm | |

| Verdreiwung (GF3YFER) | ≤25μm | ≤25μm | ≤40μm | ≤25μm | |

| LTV(SBIR) - 10mmx10mm | <2μm | ||||

| Waferrand | Ofschrägung | ||||

Uewerflächenofschloss

*n-Pm=n-Typ Pm-Grad, n-Ps=n-Typ Ps-Grad, Sl=Hallefisoléierend

| Artikel | 8-Zoll | 6-Zoll | 4-Zoll | ||

| nP | n-Pm | n-Ps | SI | SI | |

| Uewerflächenfinish | Duebelsäiteg Optesch Politur, Si-Face CMP | ||||

| Uewerflächenrauheet | (10µm x 10µm) Si-FaceRa≤0,2nm | (5µmx5µm) Si-Face Ra≤0,2nm | |||

| Kantchips | Keen erlaabt (Längt a Breet ≥0,5 mm) | ||||

| Aréckungen | Keen erlaabt | ||||

| Kratzer (Si-Face) | Quantitéit ≤5, Kumulativ | Quantitéit ≤5, Kumulativ | Quantitéit ≤5, Kumulativ | ||

| Rëss | Keen erlaabt | ||||

| Randausgrenzung | 3mm | ||||

-

Hiersteller vu Vanadium-Batteriepacken ...

-

PEM-Zell-Gasdiffusiounsschicht platinbeschichtete Ti...

-

Siliziumkarbidbeschichtete Grafitsubstrat fir S...

-

Waasserstoff Brennstoffzellen Stack Power Héichpräzisioun H...

-

Waassergekillte Waasserstoff-Brennstoffzellenmotor ouni ...

-

Grouss Gréisst rekristalliséiert Siliziumcarbid Wafer ...