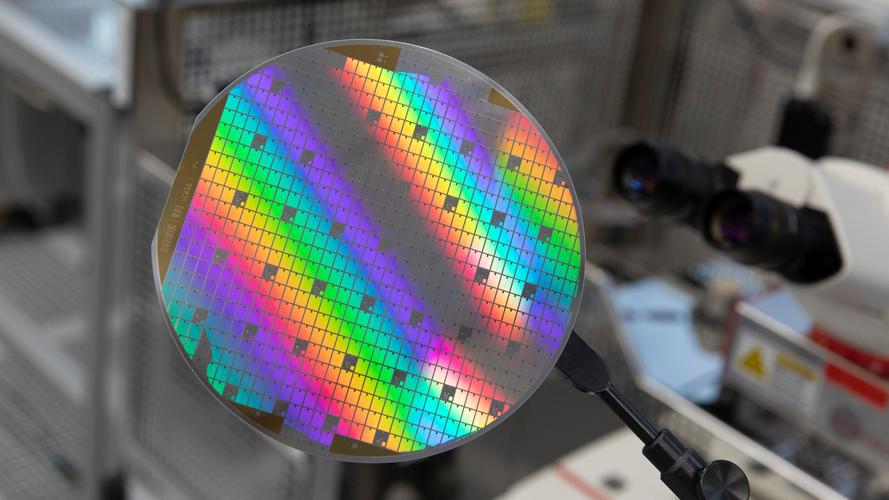

A cialda epitassiale di carburo di siliciu (SiC) di VET Energy hè un materiale semiconduttore à banda larga d'alte prestazioni cù eccellenti caratteristiche di resistenza à alta temperatura, alta frequenza è alta putenza. Hè un substratu ideale per a nova generazione di dispositivi elettronichi di putenza. VET Energy utilizza a tecnulugia epitassiale MOCVD avanzata per cultivà strati epitassiali di SiC d'alta qualità nantu à substrati di SiC, assicurendu l'eccellenti prestazioni è a consistenza di a cialda.

U nostru Wafer Epitassiale di Carburu di Siliciu (SiC) offre una eccellente compatibilità cù una varietà di materiali semiconduttori, cumpresi Si Wafer, SiC Substrate, SOI Wafer è SiN Substrate. Cù u so robustu stratu epitassiale, supporta prucessi avanzati cum'è a crescita di Epi Wafer è l'integrazione cù materiali cum'è l'Ossidu di Galliu Ga2O3 è AlN Wafer, assicurendu un usu versatile in diverse tecnulugie. Cuncipitu per esse compatibile cù i sistemi di gestione di cassette standard di l'industria, assicura operazioni efficienti è simplificate in ambienti di fabricazione di semiconduttori.

A linea di prudutti di VET Energy ùn hè micca limitata à i wafer epitaxiali di SiC. Offremu ancu una vasta gamma di materiali di substratu semiconduttori, cumpresi Si Wafer, SiC Substrate, SOI Wafer, SiN Substrate, Epi Wafer, ecc. Inoltre, stemu ancu sviluppendu attivamente novi materiali semiconduttori à banda larga, cum'è l'ossidu di galliu Ga2O3 è AlN Wafer, per risponde à a futura dumanda di l'industria elettronica di putenza per dispositivi di prestazioni più elevate.

SPECIFICHE DI WAFERING

*n-Pm=tipu n-gradu Pm,n-Ps=tipu n-gradu Ps,Sl=Semi-insulante

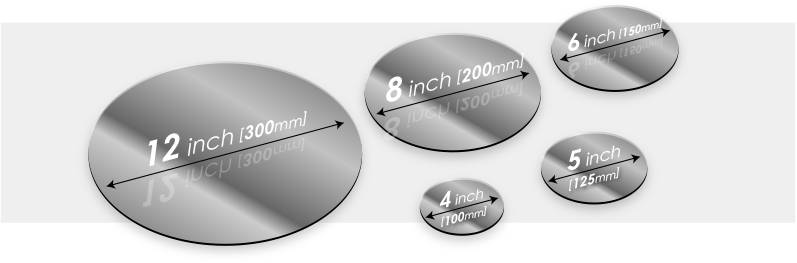

| Articulu | 8 pollici | 6 pollici | 4 pollici | ||

| nP | n-Pm | n-P | SI | SI | |

| TTV (GBIR) | ≤6um | ≤6um | |||

| Arcu (GF3YFCD) - Valore Assolutu | ≤15μm | ≤15μm | ≤25μm | ≤15μm | |

| Deformazione (GF3YFER) | ≤25μm | ≤25μm | ≤40μm | ≤25μm | |

| LTV(SBIR)-10mmx10mm | <2 μm | ||||

| Bordu di a cialda | Bisellatura | ||||

FINITURA DI A SUPERFICIE

*n-Pm=tipu n-gradu Pm,n-Ps=tipu n-gradu Ps,Sl=Semi-insulante

| Articulu | 8 pollici | 6 pollici | 4 pollici | ||

| nP | n-Pm | n-P | SI | SI | |

| Finitura di a superficia | Lucidatura Ottica à Doppiu Latu, Si-Face CMP | ||||

| Rugosità di a superficia | (10um x 10um) Si-FaceRa≤0.2nm | (5umx5um) Si-Face Ra≤0.2nm | |||

| Chips di bordu | Nisunu permessu (lunghezza è larghezza ≥0.5mm) | ||||

| Rientri | Nisunu permessu | ||||

| Graffii (Si-Face) | Qtà.≤5, Cumulativu | Qtà.≤5, Cumulativu | Qtà.≤5, Cumulativu | ||

| Crepe | Nisunu permessu | ||||

| Esclusione di u bordu | 3mm | ||||

-

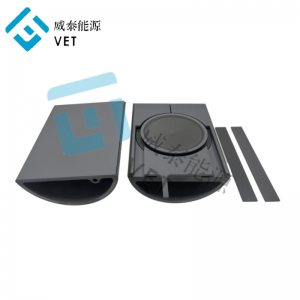

Kit di celle à combustibile per drone à idrogenu 1000w 24v

-

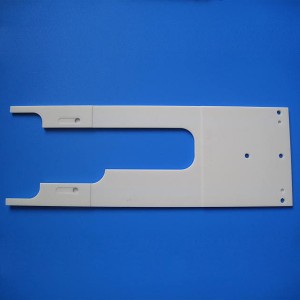

Consumabili per apparecchiature à semiconduttori, cer d'alumina...

-

Cuscinetti reggispinta impregnati di resina cù tappu di grafite...

-

Corda in grafite/fibra di carbone d'alta resistenza per Se...

-

Pila di celle à carburante Pemfc 1000w per Uav Pemfc...

-

Parte superiore è inferiore di mezza luna in grafite per Si...