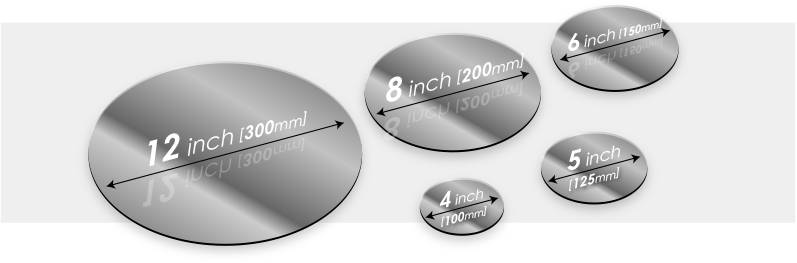

U 8 Inch P Type Silicon Wafer da VET Energy hè un wafer di siliciu d'altu rendimentu cuncepitu per una larga gamma di applicazioni di semiconduttori, cumprese celle solari, dispositivi MEMS è circuiti integrati. Cunnisciuta per a so eccellente conduttività elettrica è u so rendimentu consistente, questa wafer hè a scelta preferita per i pruduttori chì cercanu di pruduce cumpunenti elettronichi affidabili è efficienti. VET Energy assicura livelli di doping precisi è una finitura di superficia di alta qualità per a fabricazione ottimali di u dispositivu.

Questi 8 Inch P Type Silicon Wafers sò cumpletamente cumpatibili cù diversi materiali cum'è SiC Substrate, SOI Wafer, SiN Substrate, è sò adattati per a crescita Epi Wafer, assicurendu a versatilità per i prucessi avanzati di fabricazione di semiconduttori. I wafers ponu ancu esse aduprati in cunjunzione cù altri materiali d'alta tecnulugia cum'è Gallium Oxide Ga2O3 è AlN Wafer, facenu ideali per l'applicazioni elettroniche di a prossima generazione. U so design robustu si adatta ancu perfettamente à i sistemi basati in Cassette, assicurendu una gestione di produzzione efficiente è di grande volume.

VET Energy offre à i clienti soluzioni di wafer persunalizati. Pudemu persunalizà wafers cù diverse resistività, cuntenutu di ossigenu, spessore, etc., secondu i bisogni specifichi di i clienti. Inoltre, furnimu ancu un supportu tecnicu prufessiunale è un serviziu post-vendita per aiutà i clienti à risolve diversi prublemi incontrati durante u prucessu di produzzione.

SPECIFICAZIONI WAFERING

*n-Pm=n-type Pm-Grade, n-Ps=n-tipu Ps-Grade, Sl=Semi-isolante

| Articulu | 8-inch | 6-inch | 4-inch | ||

| nP | n-Pm | n-Ps | SI | SI | |

| TTV (GBIR) | ≤ 6um | ≤ 6um | |||

| Arcu (GF3YFCD) - Valore assolutu | ≤15μm | ≤15μm | ≤25μm | ≤15μm | |

| Warp (GF3YFER) | ≤25μm | ≤25μm | ≤40μm | ≤25μm | |

| LTV (SBIR) - 10 mm x 10 mm | <2μm | ||||

| Wafer Edge | Bisellu | ||||

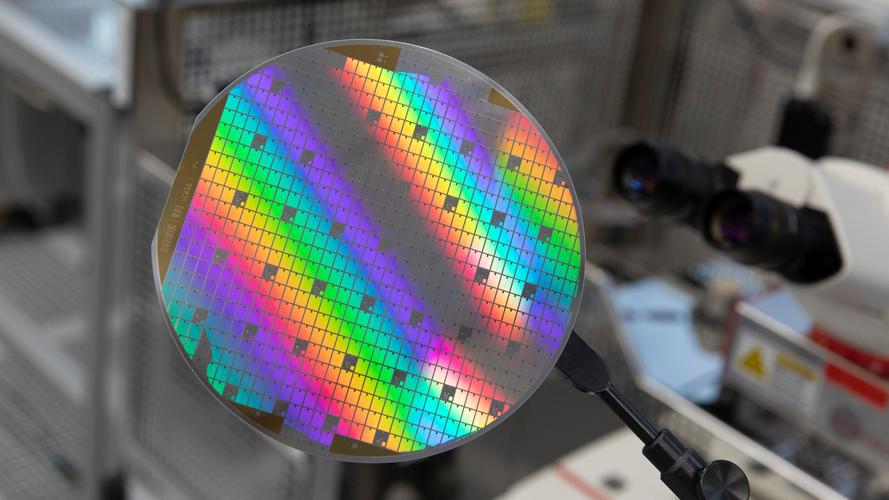

FINITURA DI SUPERFICIE

*n-Pm=n-type Pm-Grade, n-Ps=n-tipu Ps-Grade, Sl=Semi-isolante

| Articulu | 8-inch | 6-inch | 4-inch | ||

| nP | n-Pm | n-Ps | SI | SI | |

| Finitura di a superficia | Lucido ottico doppia faccia, Si-Face CMP | ||||

| Rugosità di a superficia | (10um x 10um) Si-FaceRa≤0.2nm | (5umx5um) Si-Face Ra≤0.2nm | |||

| Chips Edge | Nisunu permessu (lunghezza è larghezza ≥ 0,5 mm) | ||||

| Indentati | Nisunu permessu | ||||

| Scratchs (Si-Face) | Qty.≤5, Cumulative | Qty.≤5, Cumulative | Qty.≤5, Cumulative | ||

| Cracks | Nisunu permessu | ||||

| Exclusion di Edge | 3 mm | ||||

-

Uav 1000w Power Cella à Combustibile Idrogenu Alta Efficienza ...

-

Riscaldatore di Grafite Elettricu Personalizatu per Vacuum ...

-

Fatti di pacchettu di batterie di flussu di elettroliti di vanadiu 5kw ...

-

Pila à combustibile à l'idrogenu raffreddata à l'aria 60w Pemfc Stack F...

-

Lingottiere SIC per fusione di metalli persunalizati, silicone...

-

Palette di grafite per pale di pompa di vacuum Becker / ca...