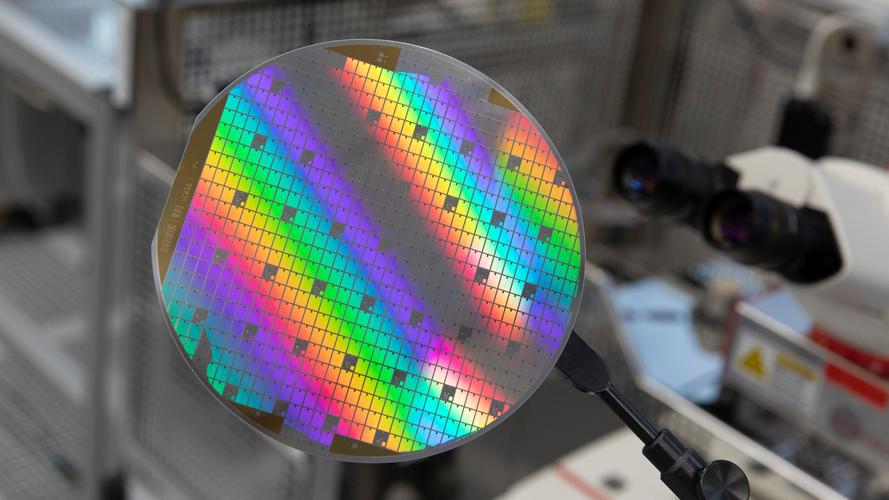

VET Energy silicon carbide (SiC) epitaxial wafer ke sesebelisoa sa semiconductor se sebetsang hantle haholo se nang le semiconductor se nang le mocheso o phahameng o matla, maqhubu a phahameng le litšobotsi tse matla tsa matla. Ke substrate e loketseng bakeng sa moloko o mocha oa lisebelisoa tsa elektroniki tsa matla. VET Energy e sebelisa theknoloji e tsoetseng pele ea MOCVD epitaxial ho holisa likarolo tsa boleng bo holimo tsa SiC epitaxial holim'a li-substrates tsa SiC, ho netefatsa ts'ebetso e ntle haholo le botsitso ba sephaphatha.

Silicon Carbide (SiC) Epitaxial Wafer ea rona e fana ka tšebelisano e ntle haholo le lisebelisoa tse fapaneng tsa semiconductor tse kenyelletsang Si Wafer, SiC Substrate, SOI Wafer, le SiN Substrate. Ka sekhahla sa eona se matla sa epitaxial, e ts'ehetsa lits'ebetso tse tsoetseng pele joalo ka kholo ea Epi Wafer le kopanyo le lisebelisoa tse kang Gallium Oxide Ga2O3 le AlN Wafer, e netefatsang ts'ebeliso e fapaneng ho mahlale a fapaneng. E etselitsoe hore e lumellane le mekhoa ea ho sebetsana le lik'hasete tse tloaelehileng tsa indasteri, e tiisa ts'ebetso e sebetsang hantle le e bonolo libakeng tsa tlhahiso ea semiconductor.

Mohala oa sehlahisoa oa VET Energy ha o felle feela ho li-wafers tsa SiC epitaxial. Re boetse re fana ka mefuta e mengata e fapaneng ea lisebelisoa tsa semiconductor substrate, ho kenyeletsoa Si Wafer, SiC Substrate, SOI Wafer, SiN Substrate, Epi Wafer, joalo-joalo Ho feta moo, re ntse re tsoela pele ho nts'etsapele lisebelisoa tse ncha tse pharalletseng tsa semiconductor, joalo ka Gallium Oxide Ga2O3 le AlN Wafer, ho fihlela tlhoko ea nakong e tlang ea lisebelisoa tsa motlakase tse phahameng tsa indasteri.

LIEKETSENG TSIETSO

*n-Pm=n-mofuta oa Pm-Grade,n-Ps=n-type Ps-Grade,Sl=Semi-lnsulation

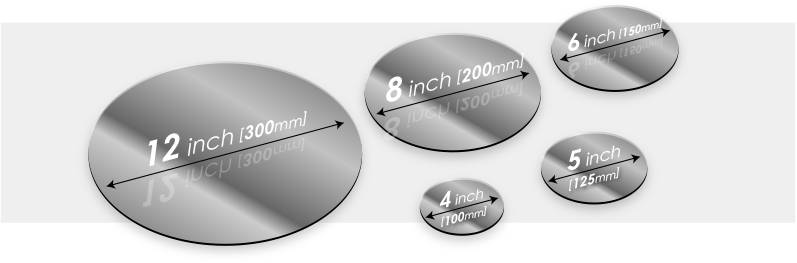

| Ntho | 8-Intshi | 6-Intshi | 4-Intshi | ||

| nP | n-Pm | n-Pes | SI | SI | |

| TTV(GBIR) | ≤6um | ≤6um | |||

| Bow(GF3YFCD)-Boleng bo Felletseng | ≤15μm | ≤15μm | ≤25μm | ≤15μm | |

| Warp(GF3YFER) | ≤25μm | ≤25μm | ≤40μm | ≤25μm | |

| LTV(SBIR) -10mmx10mm | <2μm | ||||

| Wafer Edge | Beveling | ||||

SEBAKA PHETHA

*n-Pm=n-mofuta oa Pm-Grade,n-Ps=n-type Ps-Grade,Sl=Semi-lnsulation

| Ntho | 8-Intshi | 6-Intshi | 4-Intshi | ||

| nP | n-Pm | n-Pes | SI | SI | |

| Surface Finish | Mahlakore a mabeli a Optical Polish, Si- Face CMP | ||||

| SurfaceRoughness | (10um x 10um) Si-FaceRa≤0.2nm | (5umx5um) Si-Face Ra≤0.2nm | |||

| Li-Chips tsa Edge | Ha ho e dumellwe (bolelele le bophara≥0.5mm) | ||||

| Li-indent | Ha ho le e 'ngoe e Lumelloang | ||||

| Scratches(Si-Face) | Kty.≤5, Kakaretso | Kty.≤5, Kakaretso | Kty.≤5, Kakaretso | ||

| Mapetso | Ha ho le e 'ngoe e Lumelloang | ||||

| Kenyelletso ea Edge | 3mm | ||||

-

Fuel Cell 1000w 24v Drone Hydrogen Fuel Cell Kit

-

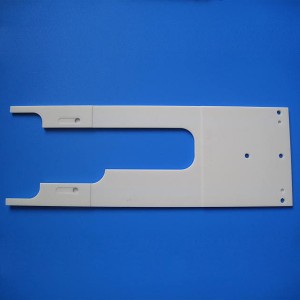

Semiconductor thepa consumables alumina cer...

-

Graphite Plug Resin Impregnated Thrust Bearings...

-

High Strength Graphite/Carbon Fiber Rope bakeng sa Se...

-

1000w Pemfc Stack Fuel Cell Stack Bakeng sa Uav Pemfc...

-

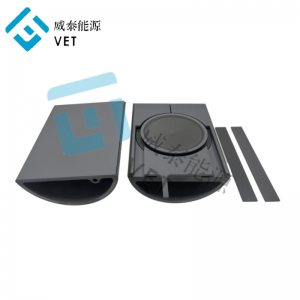

Karolo e ka holimo le e ka tlaase ea Graphite Half-moon ea Si...