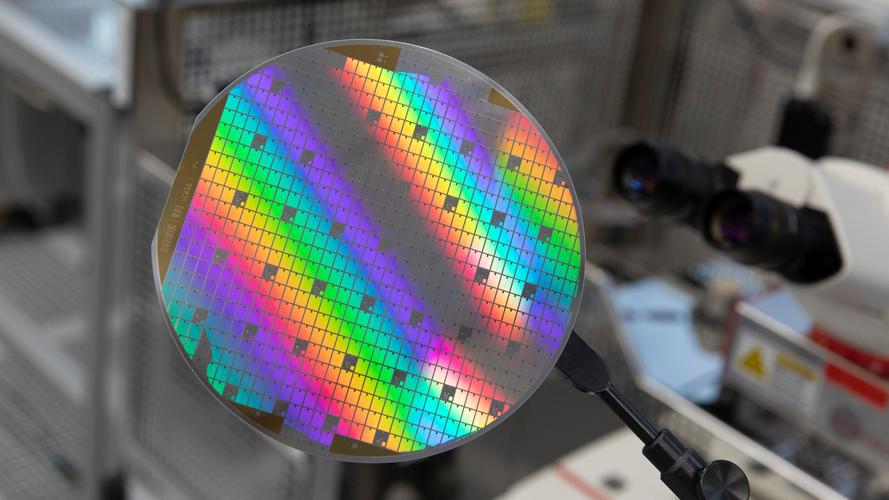

यो 6 इन्च N Type SiC Wafer चरम अवस्थाहरूमा परिष्कृत कार्यसम्पादनको लागि ईन्जिनियर गरिएको छ, यसले उच्च शक्ति र तापमान प्रतिरोध आवश्यक पर्ने अनुप्रयोगहरूको लागि एक आदर्श विकल्प बनाउँछ। यस वेफरसँग सम्बन्धित प्रमुख उत्पादनहरूमा Si Wafer, SiC सब्सट्रेट, SOI वेफर, र SiN सब्सट्रेट समावेश छन्। यी सामग्रीहरूले विभिन्न अर्धचालक निर्माण प्रक्रियाहरूमा इष्टतम प्रदर्शन सुनिश्चित गर्दछ, ऊर्जा-कुशल र टिकाऊ दुवै उपकरणहरू सक्षम पार्दै।

Epi Wafer, Gallium Oxide Ga2O3, क्यासेट वा AlN Wafer सँग काम गर्ने कम्पनीहरूका लागि VET Energy को 6 Inch N Type SiC Wafer ले नवीन उत्पादन विकासको लागि आवश्यक आधार प्रदान गर्दछ। चाहे यो उच्च-शक्ति इलेक्ट्रोनिक्समा होस् वा RF टेक्नोलोजीमा नवीनतम, यी वेफरहरूले उत्कृष्ट चालकता र न्यूनतम थर्मल प्रतिरोध सुनिश्चित गर्दछ, दक्षता र कार्यसम्पादनको सीमाहरू धकेल्दै।

Wafering निर्दिष्टीकरणहरू

*n-Pm=n-प्रकार Pm-ग्रेड,n-Ps=n-प्रकार Ps-ग्रेड, Sl=सेमी-इन्सुलेटिंग

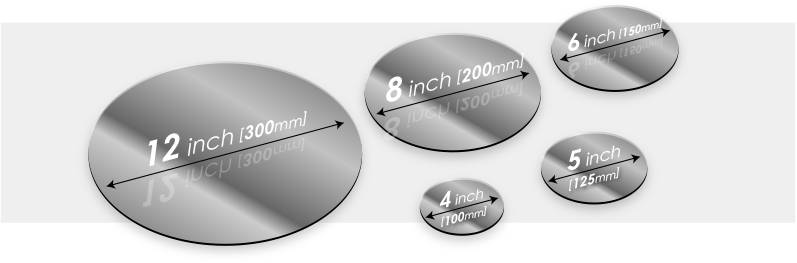

| वस्तु | ८ इन्च | ६ इन्च | ४ इन्च | ||

| nP | n-Pm | n-Ps | SI | SI | |

| TTV(GBIR) | ≤6um | ≤6um | |||

| बो(GF3YFCD)-निरपेक्ष मान | ≤15μm | ≤15μm | ≤25μm | ≤15μm | |

| ताना (GF3YFER) | ≤25μm | ≤25μm | ≤40μm | ≤25μm | |

| LTV(SBIR)-10mmx10mm | <2μm | ||||

| वेफर किनारा | बेभलिंग | ||||

सतह समाप्त

*n-Pm=n-प्रकार Pm-ग्रेड,n-Ps=n-प्रकार Ps-ग्रेड, Sl=सेमी-इन्सुलेटिंग

| वस्तु | ८ इन्च | ६ इन्च | ४ इन्च | ||

| nP | n-Pm | n-Ps | SI | SI | |

| सतह समाप्त | डबल साइड अप्टिकल पोलिश, Si- फेस CMP | ||||

| सतह रफपन | (10um x 10um) Si-FaceRa≤0.2nm | (5umx5um) Si-Face Ra≤0.2nm | |||

| किनारा चिप्स | कुनै पनि अनुमति छैन (लम्बाइ र चौडाइ≥०.५ मिमी) | ||||

| इन्डेन्टहरू | कुनै पनि अनुमति छैन | ||||

| खरोंच (सि-फेस) | मात्रा.≤5, संचयी | मात्रा.≤5, संचयी | मात्रा.≤5, संचयी | ||

| दरार | कुनै पनि अनुमति छैन | ||||

| किनारा बहिष्कार | ३ मिमी | ||||

-

MOCVD Epitaxial को लागि RTP/RTA SiC कोटिंग क्यारियर...

-

हाइड्रोजन ब्याट्री Pem इन्धन सेल Mea इलेक्ट्रोड को रूपमा ...

-

सेमीकन्डक्टर फेब्रिकाका लागि १२ इन्च सिलिकन वेफर...

-

इन्धन सेल, perf परीक्षणको लागि विशेष स्थिरता ...

-

कर्ड ट्विस्टेड ब्रेडेड कार्बन फाइबर डोरी

-

धातु हाइड्रोजन इन्धन कक्षहरू 1000w Pemfc स्ट्याकका लागि...