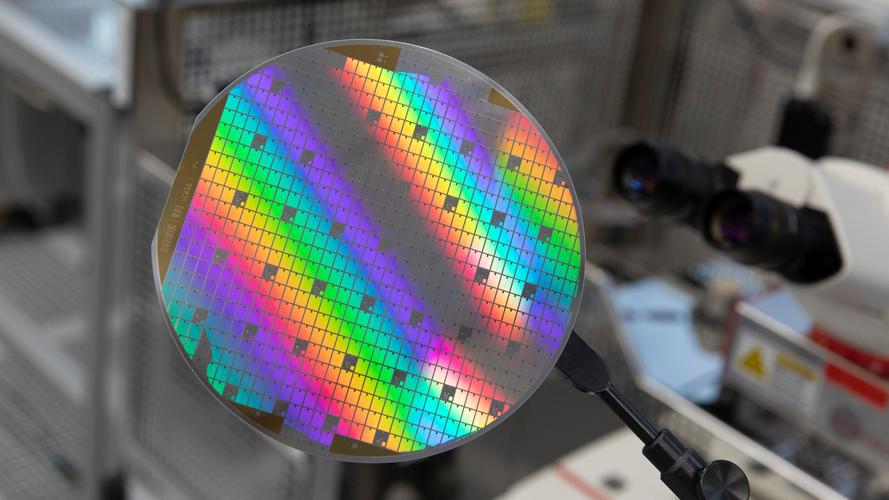

De VET Energy Siliziumkarbid (SiC) epitaxialen Wafer ass en héichperformant Hallefleedermaterial mat breeder Bandlück a exzellenter Héichtemperaturbeständegkeet, héijer Frequenz an héijer Leeschtungseigenschaften. Et ass en ideale Substrat fir déi nei Generatioun vun elektronesche Geräter mat héijer Leeschtung. VET Energy benotzt fortgeschratt MOCVD Epitaxialtechnologie fir héichqualitativ SiC Epitaxialschichten op SiC-Substrater ze wuessen, wat déi exzellent Leeschtung a Konsistenz vum Wafer garantéiert.

Eis Siliziumkarbid (SiC) epitaxial Wafer bitt exzellent Kompatibilitéit mat enger Villfalt vu Hallefleedermaterialien, dorënner Si Wafer, SiC Substrat, SOI Wafer a SiN Substrat. Mat senger robuster epitaxialer Schicht ënnerstëtzt se fortgeschratt Prozesser wéi Epi Wafer Wuesstem an Integratioun mat Materialien wéi Galliumoxid Ga2O3 an AlN Wafer, wat eng villfälteg Notzung iwwer verschidden Technologien garantéiert. Entworf fir kompatibel mat Industriestandard Kassettenbehandlungssystemer ze sinn, garantéiert se effizient an optiméiert Operatiounen an Hallefleederfabrikatiounsëmfeld.

D'Produktlinn vu VET Energy beschränkt sech net op epitaxial SiC-Waferen. Mir bidden och eng breet Palette vu Hallefleeder-Substratmaterialien, dorënner Si-Wafer, SiC-Substrat, SOI-Wafer, SiN-Substrat, Epi-Wafer, etc. Zousätzlech entwéckele mir och aktiv nei Hallefleedermaterialien mat enger breeder Bandlück, wéi Galliumoxid Ga2O3 an AlN-Wafer, fir der zukünfteger Nofro vun der Leeschtungselektronikindustrie no méi performante Komponenten gerecht ze ginn.

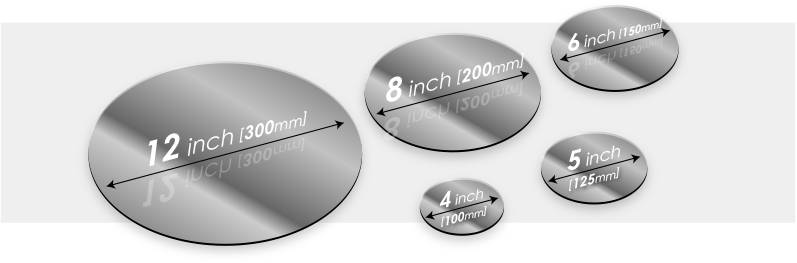

WAFEREN-SPECIFIKATIOUNEN

*n-Pm=n-Typ Pm-Grad, n-Ps=n-Typ Ps-Grad, Sl=Hallefisoléierend

| Artikel | 8-Zoll | 6-Zoll | 4-Zoll | ||

| nP | n-Pm | n-Ps | SI | SI | |

| TTV(GBIR) | ≤6µm | ≤6µm | |||

| Béi(GF3YFCD) - Absolutwäert | ≤15μm | ≤15μm | ≤25μm | ≤15μm | |

| Verdreiwung (GF3YFER) | ≤25μm | ≤25μm | ≤40μm | ≤25μm | |

| LTV(SBIR) - 10mmx10mm | <2μm | ||||

| Waferrand | Ofschrägung | ||||

Uewerflächenofschloss

*n-Pm=n-Typ Pm-Grad, n-Ps=n-Typ Ps-Grad, Sl=Hallefisoléierend

| Artikel | 8-Zoll | 6-Zoll | 4-Zoll | ||

| nP | n-Pm | n-Ps | SI | SI | |

| Uewerflächenfinish | Duebelsäiteg Optesch Politur, Si-Face CMP | ||||

| Uewerflächenrauheet | (10µm x 10µm) Si-FaceRa≤0,2nm | (5µmx5µm) Si-Face Ra≤0,2nm | |||

| Kantchips | Keen erlaabt (Längt a Breet ≥0,5 mm) | ||||

| Aréckungen | Keen erlaabt | ||||

| Kratzer (Si-Face) | Quantitéit ≤5, Kumulativ | Quantitéit ≤5, Kumulativ | Quantitéit ≤5, Kumulativ | ||

| Rëss | Keen erlaabt | ||||

| Randausgrenzung | 3mm | ||||

-

Brennstoffzell 1000w 24v Drohnen Waasserstoff Brennstoffzell Kit

-

Verbrauchsgidder fir Hallefleiterausrüstung, Aluminiumoxid...

-

Mat Grafit-Harz imprägnéierten Axiallager...

-

Héichfestigkeit Grafit/Kuelefaserseel fir Se...

-

1000w Pemfc Stack Brennstoffzellenstack fir UAV Pemfc...

-

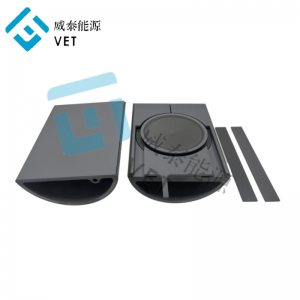

Iewescht an ënnescht Grafit Hallefmounddeel fir Si...