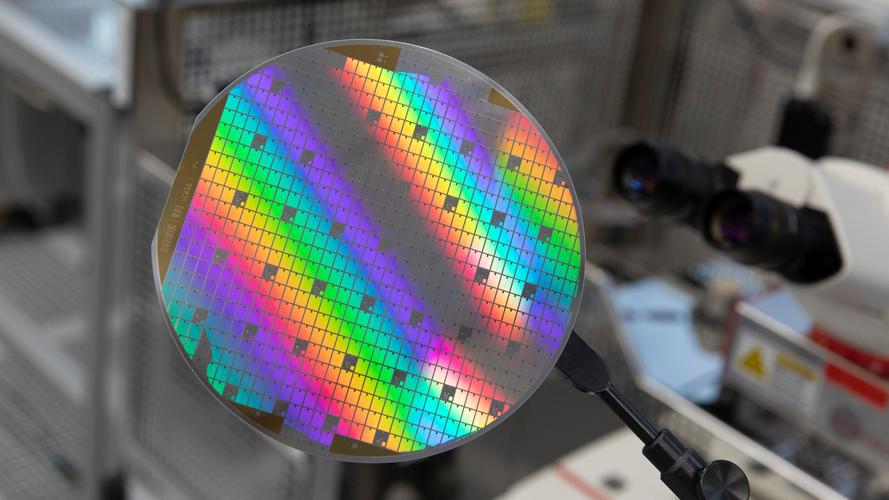

D'Produktlinn vu VET Energy beschränkt sech net op Siliziumwaferen. Mir bidden och eng breet Palette vu Hallefleeder-Substratmaterialien, dorënner SiC-Substrat, SOI-Wafer, SiN-Substrat, Epi-Wafer, etc., souwéi nei Hallefleedermaterialien mat enger breeder Bandlück wéi Galliumoxid Ga2O3 an AlN-Wafer. Dës Produkter kënnen den Uwendungsbedürfnisser vu verschiddene Clienten an der Leeschtungselektronik, der Radiofrequenz, de Sensoren an anere Beräicher erfëllen.

Applikatiounsfelder:

•Integréiert Schaltungen:Als Basismaterial fir d'Fabrikatioun vun integréierte Schaltkreesser gi P-Typ Siliziumwafere wäit verbreet a verschiddene Logikschaltkreesser, Späicherkreesser, asw. benotzt.

•Stroumgeräter:P-Typ Siliziumwafere kënne benotzt ginn fir Energieversuergungsapparater wéi Energietransistoren an Dioden ze maachen.

•Sensoren:P-Typ Siliziumwafere kënne benotzt gi fir verschidden Zorte vu Sensoren ze maachen, wéi Drocksensoren, Temperatursensoren, asw.

•Solarzellen:P-Typ Siliziumwafere sinn e wichtege Bestanddeel vu Solarzellen.

VET Energy bitt senge Clienten personaliséiert Waferléisungen a kann Wafere mat ënnerschiddlechem Widderstand, ënnerschiddlechem Sauerstoffgehalt, ënnerschiddlecher Déckt an aner Spezifikatioune personaliséieren, jee no de spezifesche Bedierfnesser vun de Clienten. Zousätzlech bidden mir och professionellen techneschen Support an After-Sales-Service, fir de Clienten ze hëllefen, verschidde Problemer ze léisen, déi am Produktiounsprozess optrieden.

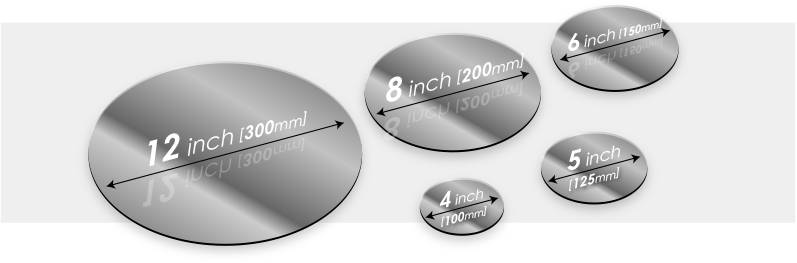

WAFEREN-SPECIFIKATIOUNEN

*n-Pm=n-Typ Pm-Grad, n-Ps=n-Typ Ps-Grad, Sl=Hallefisoléierend

| Artikel | 8-Zoll | 6-Zoll | 4-Zoll | ||

| nP | n-Pm | n-Ps | SI | SI | |

| TTV(GBIR) | ≤6µm | ≤6µm | |||

| Béi(GF3YFCD) - Absolutwäert | ≤15μm | ≤15μm | ≤25μm | ≤15μm | |

| Verdreiwung (GF3YFER) | ≤25μm | ≤25μm | ≤40μm | ≤25μm | |

| LTV(SBIR) - 10mmx10mm | <2μm | ||||

| Waferrand | Ofschrägung | ||||

Uewerflächenofschloss

*n-Pm=n-Typ Pm-Grad, n-Ps=n-Typ Ps-Grad, Sl=Hallefisoléierend

| Artikel | 8-Zoll | 6-Zoll | 4-Zoll | ||

| nP | n-Pm | n-Ps | SI | SI | |

| Uewerflächenfinish | Duebelsäiteg Optesch Politur, Si-Face CMP | ||||

| Uewerflächenrauheet | (10µm x 10µm) Si-FaceRa≤0,2nm | (5µmx5µm) Si-Face Ra≤0,2nm | |||

| Kantchips | Keen erlaabt (Längt a Breet ≥0,5 mm) | ||||

| Aréckungen | Keen erlaabt | ||||

| Kratzer (Si-Face) | Quantitéit ≤5, Kumulativ | Quantitéit ≤5, Kumulativ | Quantitéit ≤5, Kumulativ | ||

| Rëss | Keen erlaabt | ||||

| Randausgrenzung | 3mm | ||||

-

Solar Graphit Boot fir Pecvd

-

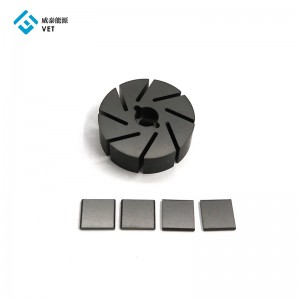

Grafitrotor fir Vakuumpompel

-

Waassergekillte 100KW Waasserstoff Brennstoffzellen Stack fir...

-

Waasserstoff Brennstoffzell Pem Drone Generator Waasserstoff...

-

Bëlleg Waasserstoff Brennstoff Dron Sofc Waasserstoff Gen ...

-

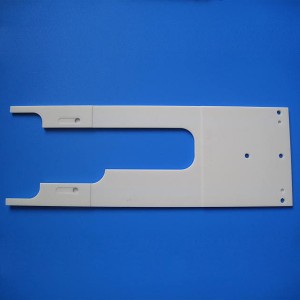

Verbrauchsgidder fir Hallefleiterausrüstung, Aluminiumoxid...