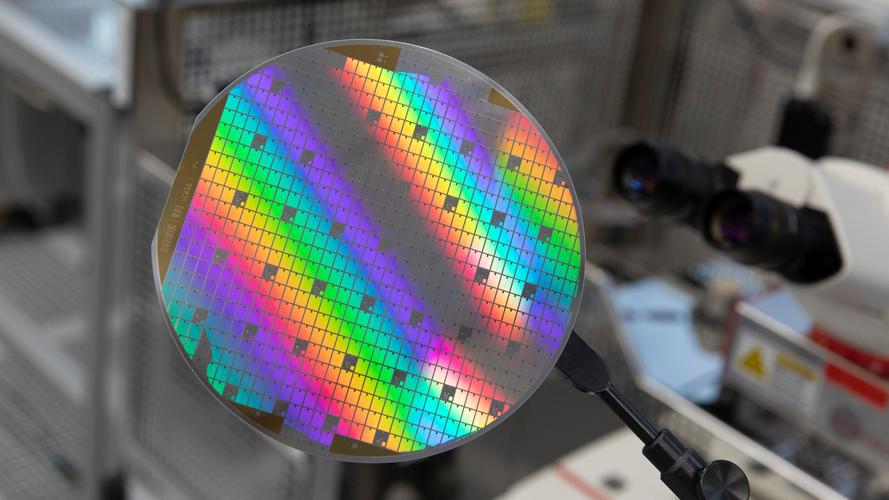

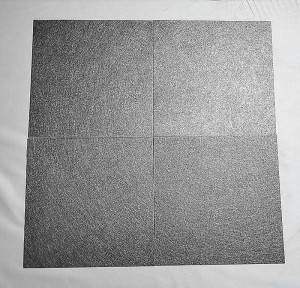

Lamella SiC semi-insulans sex unciarum a VET Energy fabricata est solutio provecta ad applicationes magnae potentiae et altae frequentiae, praebens conductivitatem thermalem et insulationem electricam superiorem. Hae lamellae semi-insulantes essentiales sunt in evolutione instrumentorum qualia sunt amplificatores RF, interruptores potentiae, et alia elementa altae tensionis. VET Energy qualitatem et efficaciam constantem curat, has lamellas ideales reddens ad amplam varietatem processuum fabricationis semiconductorum.

Praeter egregias proprietates insulationis, hae laminae SiC cum variis materiis, inter quas lamina Si, substratum SiC, lamina SOI, substratum SiN, et lamina Epi, congruunt, quod eas versatiles reddit ad varios modos fabricationis. Praeterea, materiae provectae, ut oxidum Gallii Ga₂O₃ et lamina AlN, una cum his laminis SiC adhiberi possunt, flexibilitatem etiam maiorem in instrumentis electronicis magnae potentiae praebentes. Laminae ad integrationem sine interruptione cum systematibus tractationis secundum normas industriales, ut systemata Cassettarum, designatae sunt, facilitatem usus in condicionibus productionis massalis praestantes.

VET Energy offert amplum catalogum substratorum semiconductorum, inter quae sunt Si Wafer, SiC Substratum, SOI Wafer, SiN Substratum, Epi Wafer, Gallium Oxidum Ga₂O₃, et AlN Wafer. Nostra varia linea productorum necessitatibus variarum applicationum electronicarum satisfacit, ab electronica potentiae ad RF et optoelectronicam.

Lamella SiC semi-insulans sex unciarum plura commoda offert:

Alta tensio disruptiva: Lata lacuna frequentiae SiC maiores tensiones disruptivas permittit, ita machinas potentiae compactiores et efficaciores efficiens.

Operatio ad altas temperaturas: Excellens conductivitas thermalis SiC operationem ad altiores temperaturas permittit, firmitatem instrumenti augens.

Resistentia acta humilis: Instrumenta SiC resistentiam actae inferiorem exhibent, iacturas potentiae minuentes et efficientiam energiae augentes.

VET Energy offert crustas SiC adaptabiles ad requisita tua specifica implenda, inter quas sunt crassitudines variae, gradus dopationis, et superficies poliendae. Turma nostra peritorum auxilium technicum et servitium post-venditionem praebet ut successum tuum confirmet.

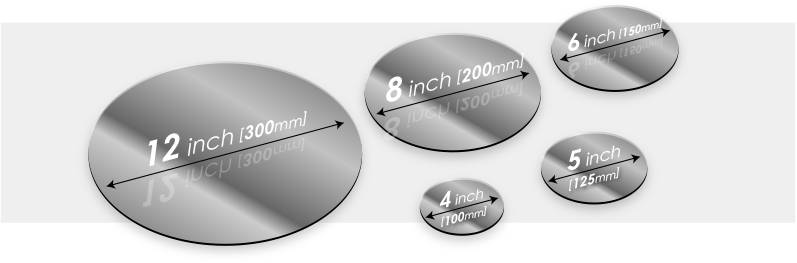

SPECIFICATIONES WAFERING

*n-Pm = n-typus Pm-Gradus, n-Ps = n-typus Ps-Gradus, Sl = Semi-insulans

| Res | Octo-unciae | Sex unciarum | Quattuor unciarum | ||

| nP | n-Pm | n-P | SI | SI | |

| TTV (GBIR) | ≤6um | ≤6um | |||

| Arcus (GF3YFCD) - Valor Absolutus | ≤15μm | ≤15μm | ≤25μm | ≤15μm | |

| Deformatio (GF3YFER) | ≤25μm | ≤25μm | ≤40μm | ≤25μm | |

| LTV(SBIR)-10mm x 10mm | <2μm | ||||

| Margo Lamellae | Beveling | ||||

SUPERFICIES SUPERFICIIS

*n-Pm = n-typus Pm-Gradus, n-Ps = n-typus Ps-Gradus, Sl = Semi-insulans

| Res | Octo-unciae | Sex unciarum | Quattuor unciarum | ||

| nP | n-Pm | n-P | SI | SI | |

| Superficies Finis | Politura optica utrinque, Si-Face CMP | ||||

| Asperitas Superficialis | (10um × 10um) Si-FaciesRa≤0.2nm | (5um x 5um) Facies Silicis Ra ≤ 0.2nm | |||

| Fragmenta Marginis | Nullum Permissum (longitudo et latitudo ≥0.5mm) | ||||

| Indentationes | Nullum Permissum | ||||

| Scalpturae (Si-Facie) | Quantitas ≤5, Cumulativa | Quantitas ≤5, Cumulativa | Quantitas ≤5, Cumulativa | ||

| Fissurae | Nullum Permissum | ||||

| Exclusio Marginis | 3mm | ||||

-

Fabricator fasciculorum accumulatorum vanadium fluminis...

-

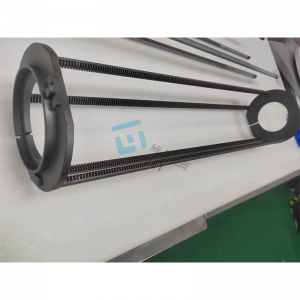

Stratum diffusionis gasis cellulae PEM platino obductum ti...

-

Substratum Graphiticum Carbido Silicio Obductum pro S...

-

Acervus Cellarum Combustibilis Hydrogenii Potentia Altae Praecisionis H...

-

Machina cellae combustibilis hydrogenii aqua refrigerata sine...

-

Magnae Magnitudinis Recrystallizatae Silicii Carbidi Wafer...