Mikä on BCD-prosessi?

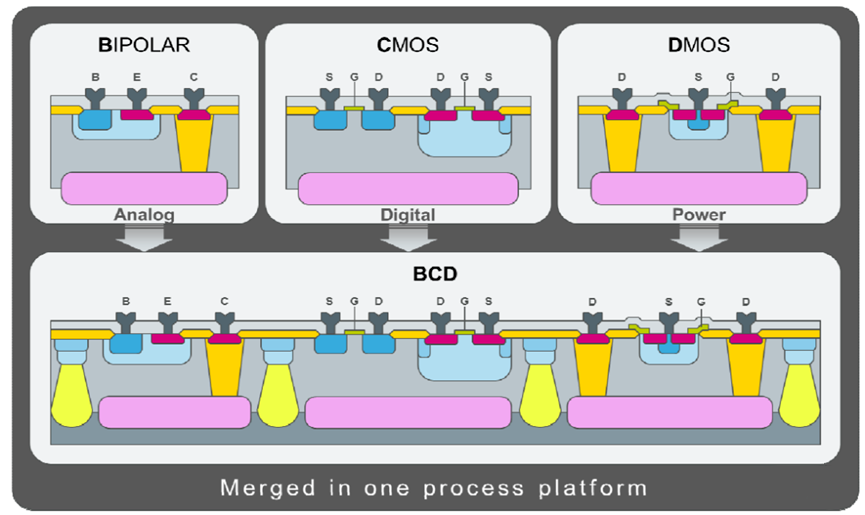

BCD-prosessi on yhden sirun integroitu prosessitekniikka, jonka ST esitteli ensimmäisen kerran vuonna 1986. Tämä tekniikka voi valmistaa bipolaarisia, CMOS- ja DMOS-laitteita samalle sirulle. Sen ulkonäkö pienentää huomattavasti sirun pinta-alaa.

Voidaan sanoa, että BCD-prosessi hyödyntää täysimääräisesti bipolaarisen ohjauskyvyn, CMOS-teknologian korkean integroinnin ja alhaisen virrankulutuksen sekä DMOS-teknologian korkean jännitteen ja suuren virrankulutuskapasiteetin etuja. Näistä DMOS on avainasemassa tehon ja integroinnin parantamisessa. Integroitujen piirien teknologian kehittyessä BCD-prosessista on tullut PMIC-teknologian valtavirtavalmistustekniikka.

BCD-prosessin poikkileikkauskaavio, lähdeverkko, kiitos

BCD-prosessin edut

BCD-prosessi yhdistää bipolaaripiirit, CMOS-piirit ja DMOS-tehopiirit samalle sirulle samanaikaisesti. Tämä yhdistää bipolaaripiirien korkean transkonduktanssin ja voimakkaan kuormituksen ajokyvyn sekä CMOS-piirien korkean integrointikyvyn ja alhaisen virrankulutuksen, jolloin ne täydentävät toisiaan ja hyödyntävät täysin omia etujaan. Samalla DMOS voi toimia hakkuritilassa erittäin alhaisella virrankulutuksella. Lyhyesti sanottuna alhainen virrankulutus, korkea energiatehokkuus ja korkea integrointikyky ovat BCD:n tärkeimpiä etuja. BCD-prosessi voi merkittävästi vähentää virrankulutusta, parantaa järjestelmän suorituskykyä ja parantaa luotettavuutta. Elektronisten tuotteiden toiminnot lisääntyvät päivä päivältä, ja jännitemuutosten, kondensaattorisuojauksen ja akun käyttöiän pidentämisen vaatimukset ovat yhä tärkeämpiä. BCD:n nopeat ja energiansäästöominaisuudet täyttävät korkean suorituskyvyn analogisten/virranhallintapiirien prosessivaatimukset.

BCD-prosessin keskeiset teknologiat

Tyypillisiä BCD-prosessissa käytettäviä laitteita ovat pienjännite-CMOS-mikroskooppit, suurjännite-MOS-putket, erilaisilla läpilyöntijännitteillä varustetut LDMOS-mikroskooppit, pystysuuntaiset NPN/PNP-diodit ja Schottky-diodit jne. Joissakin prosesseissa integroidaan myös laitteita, kuten JFET ja EEPROM, mikä johtaa laajaan valikoimaan BCD-prosessissa käytettäviä laitteita. Siksi suurjännitelaitteiden ja pienjännitelaitteiden, kaksoisnapsautusprosessien ja CMOS-prosessien jne. yhteensopivuuden huomioon ottamisen lisäksi suunnittelussa on otettava huomioon myös sopiva eristystekniikka.

BCD-eristystekniikassa on syntynyt useita tekniikoita, kuten liitosten eristäminen, itseeristäminen ja dielektrinen eristäminen. Liitosten eristystekniikassa laite valmistetaan P-tyypin substraatin N-tyypin epitaksiaalikerrokselle ja PN-liitoksen käänteisjänniteominaisuuksia käytetään eristämisen saavuttamiseksi, koska PN-liitoksella on erittäin korkea resistanssi käänteisjännitettä vastaan.

Itseeristystekniikka on pohjimmiltaan PN-liitoksen eristystä, joka perustuu laitteen lähteen ja drainin sekä substraatin välisten luonnollisten PN-liitoksen ominaisuuksiin eristyksen saavuttamiseksi. Kun MOS-putki kytketään päälle, lähdealue, drain-alue ja kanava ympäröivät tyhjennysalue, muodostaen eristyksen substraatista. Kun se kytketään pois päältä, drain-alueen ja substraatin välinen PN-liitos on estojännitetty, ja lähdealueen korkea jännite eristetään tyhjennysalueella.

Dielektrisessä eristyksessä käytetään eristysmateriaalia, kuten piioksidia, eristyksen saavuttamiseksi. Dielektriseen eristykseen ja liitoskohtien eristykseen perustuen on kehitetty lähes dielektrinen eristys yhdistämällä molempien edut. Käyttämällä valikoivasti edellä mainittua eristystekniikkaa voidaan saavuttaa suurjännitteen ja pienjännitteen yhteensopivuus.

BCD-prosessin kehityssuunta

BCD-prosessitekniikan kehitys ei ole samanlaista kuin tavallinen CMOS-prosessi, joka on aina noudattanut Mooren lakia ja kehittynyt kohti pienempää viivanleveyttä ja nopeampaa nopeutta. BCD-prosessi on karkeasti eriytetty ja sitä on kehitetty kolmeen suuntaan: korkea jännite, suuri teho ja suuri tiheys.

1. Korkeajännitteinen BCD-suunta

Korkeajännitteinen BCD voi valmistaa samanaikaisesti samalla sirulla luotettavia matalajännitteisiä ohjauspiirejä ja erittäin korkeajännitteisiä DMOS-tason piirejä, ja sillä voidaan tuottaa 500–700 V:n korkeajännitteisiä laitteita. Yleisesti ottaen BCD soveltuu kuitenkin edelleen tuotteisiin, joilla on suhteellisen korkeat vaatimukset teholaitteille, erityisesti BJT- tai suurvirtaisille DMOS-laitteille, ja sitä voidaan käyttää tehonsäätöön elektronisessa valaistuksessa ja teollisuussovelluksissa.

Nykyinen korkeajännitteisen BCD:n valmistustekniikka on Appel et al.:n vuonna 1979 ehdottama RESURF-tekniikka. Laite valmistetaan käyttämällä kevyesti seostettua epitaksiaalikerrosta, joka tekee pinnan sähkökentän jakaumasta tasaisemman, mikä parantaa pinnan läpilyöntiominaisuuksia niin, että läpilyönti tapahtuu rungossa pinnan sijaan, mikä lisää laitteen läpilyöntijännitettä. Kevytdoping on toinen menetelmä BCD:n läpilyöntijännitteen lisäämiseksi. Siinä käytetään pääasiassa kaksoisdiffuusiodrainia DDD (double doping drain) ja kevyesti seostettua drainia LDD (lightly doping drain). DMOS-drain-alueelle lisätään N-tyypin ajautumisalue, joka muuttaa alkuperäisen kontaktin N+-drainin ja P-tyypin substraatin välillä N-drainin ja P-tyypin substraatin väliseksi kontaktiksi, mikä lisää läpilyöntijännitettä.

2. Suuritehoinen BCD-suunta

Suuritehoisen BCD:n jännitealue on 40–90 V, ja sitä käytetään pääasiassa autoelektroniikassa, joka vaatii suurta virrankäyttökykyä, keskijännitettä ja yksinkertaisia ohjauspiirejä. Sen kysyntäominaisuuksia ovat suuri virrankäyttökyky, keskijännite ja usein suhteellisen yksinkertainen ohjauspiiri.

3. Suuritiheyksinen BCD-suunta

Suuritiheyksisen BCD:n jännitealue on 5–50 V, ja jotkut autoelektroniikkalaitteet saavuttavat 70 V:n jännitteen. Yhä monimutkaisempia ja monipuolisempia toimintoja voidaan integroida samalle sirulle. Suuritiheyksisessä BCD:ssä käytetään modulaarisia suunnitteluideoita tuotteiden monipuolistamiseksi, ja sitä käytetään pääasiassa autoelektroniikan sovelluksissa.

BCD-prosessin tärkeimmät sovellukset

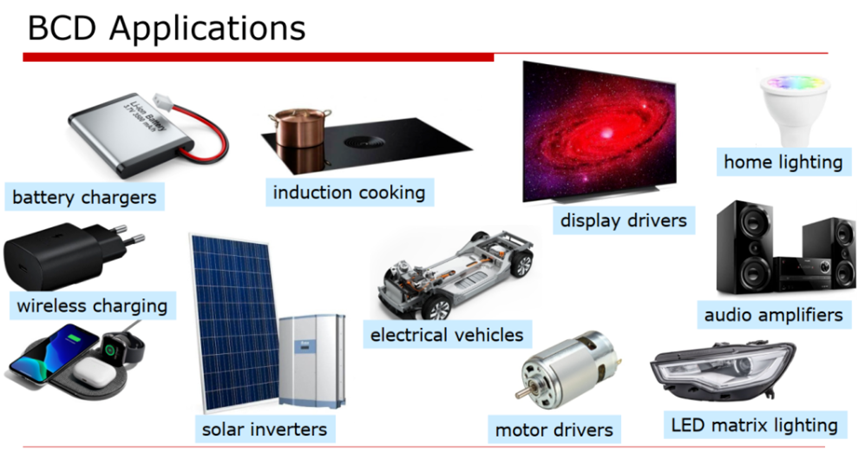

BCD-prosessia käytetään laajalti virranhallintaan (virran- ja akun hallinta), näyttöjen ohjaukseen, autoelektroniikkaan, teollisuuden ohjaukseen jne. Virranhallintapiiri (PMIC) on yksi tärkeimmistä analogisten sirujen tyypeistä. BCD-prosessin ja SOI-teknologian yhdistelmä on myös tärkeä osa BCD-prosessin kehitystä.

VET-China voi toimittaa grafiittiosia, pehmeää huopaa, piikarbidiosia, CVD-piikarbidiosia ja sic/Tac-päällystettyjä osia 30 päivässä.

Jos olet kiinnostunut edellä mainituista puolijohdetuotteista, älä epäröi ottaa meihin yhteyttä ensimmäistä kertaa.

Puh: +86-1891 1596 392

WhatsApp: 86-18069021720

Sähköposti:yeah@china-vet.com

Julkaisun aika: 18.9.2024