Kaj je postopek BCD?

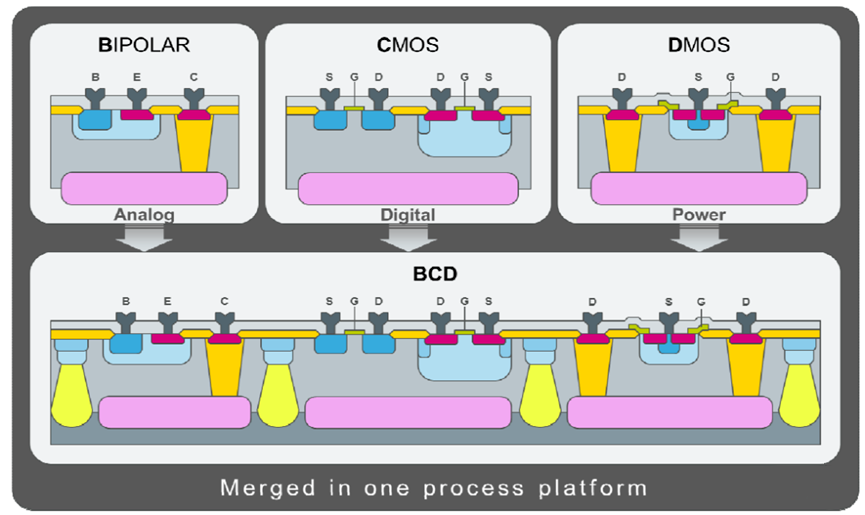

BCD postopek je integrirana procesna tehnologija z enim čipom, ki jo je ST prvič predstavil leta 1986. Ta tehnologija omogoča izdelavo bipolarnih, CMOS in DMOS naprav na istem čipu. Zaradi svojega videza močno zmanjša površino čipa.

Lahko rečemo, da postopek BCD v celoti izkorišča prednosti bipolarne krmiljenosti, visoke integracije in nizke porabe energije CMOS-a ter visoke napetosti in visoke tokovne zmogljivosti DMOS-a. Med njimi je DMOS ključ do izboljšanja moči in integracije. Z nadaljnjim razvojem tehnologije integriranih vezij je postopek BCD postal glavna proizvodna tehnologija PMIC-a.

Prečni diagram procesa BCD, izvorno omrežje, hvala

Prednosti postopka BCD

Postopek BCD omogoča sočasno izdelavo bipolarnih, CMOS in DMOS napajalnih naprav na istem čipu, pri čemer se združuje visoka transkonduktanca in močna zmogljivost krmiljenja obremenitve bipolarnih naprav ter visoka integracija in nizka poraba energije CMOS, tako da se lahko medsebojno dopolnjujejo in v celoti izkoristijo svoje prednosti; hkrati lahko DMOS deluje v preklopnem načinu z izjemno nizko porabo energije. Skratka, nizka poraba energije, visoka energetska učinkovitost in visoka integracija so ene glavnih prednosti BCD. Postopek BCD lahko znatno zmanjša porabo energije, izboljša delovanje sistema in ima boljšo zanesljivost. Funkcije elektronskih izdelkov se iz dneva v dan povečujejo, zahteve glede sprememb napetosti, zaščite kondenzatorjev in podaljšanja življenjske dobe baterije pa postajajo vse pomembnejše. Hitre in energijsko varčne lastnosti BCD izpolnjujejo procesne zahteve za visokozmogljive analogne/power-upravljalne čipe.

Ključne tehnologije procesa BCD

Tipične naprave postopka BCD vključujejo nizkonapetostne CMOS tranzistorje, visokonapetostne MOS cevi, LDMOS tranzistorje z različnimi prebojnimi napetostmi, vertikalne NPN/PNP in Schottky diode itd. Nekateri postopki vključujejo tudi naprave, kot sta JFET in EEPROM, kar ima za posledico veliko raznolikost naprav v postopku BCD. Zato je treba poleg upoštevanja združljivosti visokonapetostnih in nizkonapetostnih naprav, postopkov dvojnega klika in CMOS postopkov itd. pri načrtovanju upoštevati tudi ustrezno izolacijsko tehnologijo.

V tehnologiji izolacije BCD se je zaporedoma pojavilo veliko tehnologij, kot so izolacija spojev, samoizolacija in dielektrična izolacija. Tehnologija izolacije spojev pomeni izdelavo naprave na epitaksialni plasti tipa N substrata tipa P in uporabo lastnosti povratne prednapetosti PN spoja za doseganje izolacije, saj ima PN spoj zelo visoko upornost pri povratni prednapetosti.

Tehnologija samoizolacije je v bistvu izolacija PN spoja, ki se za doseganje izolacije opira na naravne značilnosti PN spoja med izvornim in odtočnim območjem naprave ter substratom. Ko je MOS cev vklopljena, so izvorno območje, odtočno območje in kanal obdani z izčrpanim območjem, kar tvori izolacijo od substrata. Ko je izklopljena, je PN spoj med odtočnim območjem in substratom obrnjen, visoka napetost izvornega območja pa je izolirana z izčrpanim območjem.

Dielektrična izolacija uporablja izolacijske medije, kot je silicijev oksid, za doseganje izolacije. Na podlagi dielektrične izolacije in izolacije spojev je bila razvita kvazidielektrična izolacija, ki združuje prednosti obeh. Z selektivno uporabo zgoraj omenjene tehnologije izolacije je mogoče doseči združljivost pri visoki in nizki napetosti.

Smer razvoja procesa BCD

Razvoj procesne tehnologije BCD ni podoben standardnemu CMOS procesu, ki je vedno sledil Mooreovemu zakonu in se razvijal v smeri manjše širine linij in večje hitrosti. Proces BCD se v grobem razlikuje in razvija v treh smereh: visoka napetost, visoka moč in visoka gostota.

1. Smer visokonapetostnega BCD-ja

Visokonapetostni BCD lahko hkrati na istem čipu izdeluje visoko zanesljiva nizkonapetostna krmilna vezja in ultra visokonapetostna vezja na ravni DMOS ter omogoča izdelavo visokonapetostnih naprav 500–700 V. Vendar pa je BCD na splošno še vedno primeren za izdelke z relativno visokimi zahtevami glede napajalnih naprav, zlasti BJT ali visokotokovne DMOS naprave, in se lahko uporablja za nadzor moči v elektronski razsvetljavi in industrijskih aplikacijah.

Trenutna tehnologija za izdelavo visokonapetostnih BCD-jev je tehnologija RESURF, ki so jo leta 1979 predlagali Appel in sodelavci. Naprava je izdelana z uporabo rahlo dopirane epitaksialne plasti, ki omogoča bolj ravno porazdelitev električnega polja na površini in s tem izboljša prebojne karakteristike na površini, tako da do preboja pride v telesu namesto na površini, s čimer se poveča prebojna napetost naprave. Lahko dopiranje je druga metoda za povečanje prebojne napetosti BCD-ja. V glavnem se uporablja dvojno difuzni odtok DDD (dvojni doping odtok) in rahlo dopiran odtok LDD (rahlo doping odtok). V območju odtoka DMOS se doda območje drifta tipa N, ki spremeni prvotni stik med odtokom N+ in substratom tipa P v stik med odtokom N- in substratom tipa P, s čimer se poveča prebojna napetost.

2. Smer BCD z veliko močjo

Napetostno območje visokozmogljivega BCD-ja je 40–90 V in se uporablja predvsem v avtomobilski elektroniki, ki zahteva visokotokovno pogonsko zmogljivost, srednjo napetost in preprosta krmilna vezja. Njegove zahteve so visokotokovna pogonska zmogljivost, srednja napetost in krmilno vezje je pogosto relativno preprosto.

3. Smer BCD z visoko gostoto

BCD z visoko gostoto, napetostno območje je 5-50 V, nekatere avtomobilske elektronike pa lahko dosežejo 70 V. Na istem čipu je mogoče integrirati vedno več kompleksnih in raznolikih funkcij. BCD z visoko gostoto uporablja nekatere modularne zasnove za doseganje diverzifikacije izdelkov, ki se uporabljajo predvsem v avtomobilski elektroniki.

Glavne uporabe procesa BCD

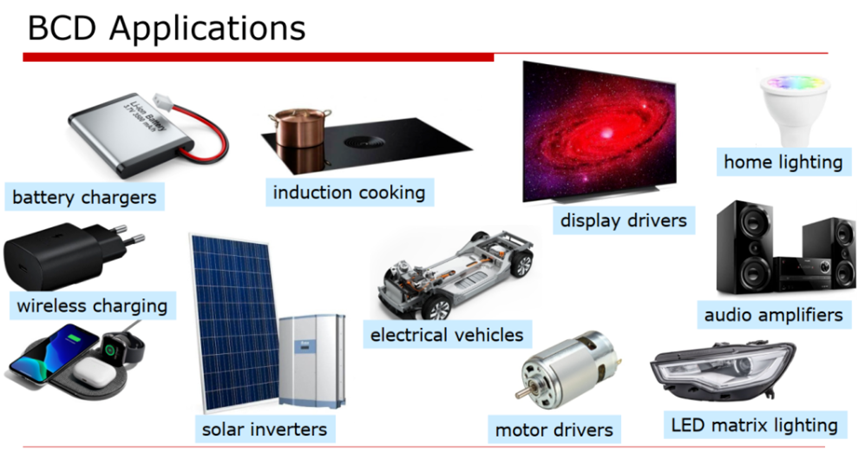

Postopek BCD se pogosto uporablja pri upravljanju porabe energije (krmiljenje moči in baterij), prikazovalnikih, avtomobilski elektroniki, industrijskem krmiljenju itd. Čip za upravljanje porabe energije (PMIC) je ena pomembnih vrst analognih čipov. Kombinacija postopka BCD in tehnologije SOI je prav tako pomembna značilnost razvoja postopka BCD.

VET-China lahko v 30 dneh dobavi grafitne dele, mehkotrdni filc, dele iz silicijevega karbida, dele iz silicijevega karbida s CVD prevleko in dele s prevleko sic/Tac.

Če vas zanimajo zgoraj navedeni polprevodniški izdelki, nas prosimo kontaktirajte že prvič.

Tel.: +86-1891 1596 392

WhatsApp: 86-18069021720

E-pošta:yeah@china-vet.com

Čas objave: 18. september 2024