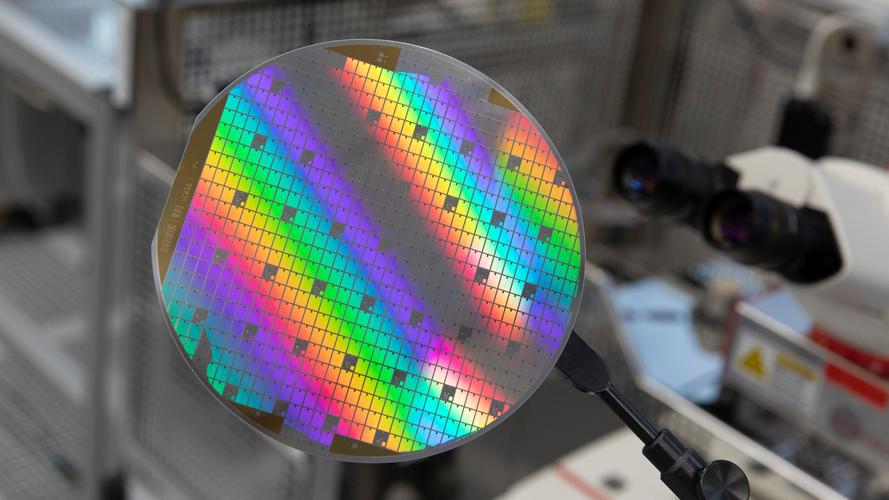

O wafer epitaxial de carboneto de silício (SiC) da VET Energy é um material semicondutor de alto desempenho com ampla banda proibida, com excelentes características de resistência a altas temperaturas, alta frequência e alta potência. É um substrato ideal para a nova geração de dispositivos eletrônicos de potência. A VET Energy utiliza a avançada tecnologia epitaxial MOCVD para cultivar camadas epitaxiais de SiC de alta qualidade em substratos de SiC, garantindo excelente desempenho e consistência do wafer.

Nosso wafer epitaxial de carboneto de silício (SiC) oferece excelente compatibilidade com uma variedade de materiais semicondutores, incluindo wafer de Si, substrato de SiC, wafer SOI e substrato de SiN. Com sua robusta camada epitaxial, ele suporta processos avançados, como o crescimento de wafers Epi e a integração com materiais como óxido de gálio Ga2O3 e wafer de AlN, garantindo versatilidade em diferentes tecnologias. Projetado para ser compatível com os sistemas de manuseio de cassetes padrão da indústria, ele garante operações eficientes e otimizadas em ambientes de fabricação de semicondutores.

A linha de produtos da VET Energy não se limita a wafers epitaxiais de SiC. Também fornecemos uma ampla gama de materiais de substrato semicondutor, incluindo wafer de Si, substrato de SiC, wafer SOI, substrato de SiN, wafer Epi, etc. Além disso, estamos desenvolvendo ativamente novos materiais semicondutores de banda larga, como óxido de gálio Ga2O3 e wafer de AlN, para atender à futura demanda da indústria de eletrônica de potência por dispositivos de alto desempenho.

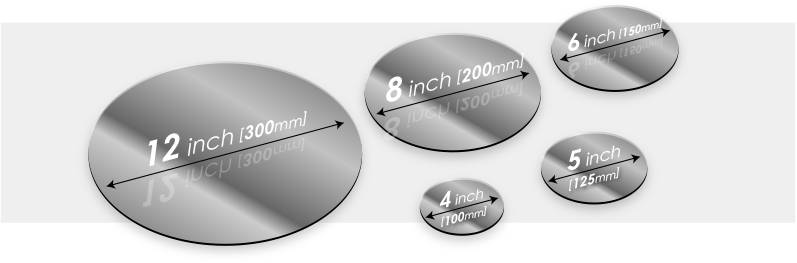

ESPECIFICAÇÕES DE WAFERING

*n-Pm=n-tipo Pm-Grau,n-Ps=n-tipo Ps-Grau,Sl=Semi-isolante

| Item | 8 polegadas | 6 polegadas | 4 polegadas | ||

| nP | n-Pm | n-Ps | SI | SI | |

| TTV(GBIR) | ≤6um | ≤6um | |||

| Bow(GF3YFCD)-Valor Absoluto | ≤15μm | ≤15μm | ≤25μm | ≤15μm | |

| Deformação(GF3YFER) | ≤25μm | ≤25μm | ≤40μm | ≤25μm | |

| LTV(SBIR)-10mmx10mm | <2μm | ||||

| Borda de Wafer | Chanfradura | ||||

ACABAMENTO DE SUPERFÍCIE

*n-Pm=n-tipo Pm-Grau,n-Ps=n-tipo Ps-Grau,Sl=Semi-isolante

| Item | 8 polegadas | 6 polegadas | 4 polegadas | ||

| nP | n-Pm | n-Ps | SI | SI | |

| Acabamento de superfície | Polimento óptico de dupla face, Si-Face CMP | ||||

| Rugosidade da superfície | (10um x 10um) Si-FaceRa≤0,2nm | (5umx5um) Si-Face Ra≤0,2nm | |||

| Chips de Borda | Nenhum permitido (comprimento e largura ≥ 0,5 mm) | ||||

| Recuos | Nenhum permitido | ||||

| Arranhões (Si-Face) | Qtd.≤5,Acumulativo | Qtd.≤5,Acumulativo | Qtd.≤5,Acumulativo | ||

| Rachaduras | Nenhum permitido | ||||

| Exclusão de Borda | 3 mm | ||||

-

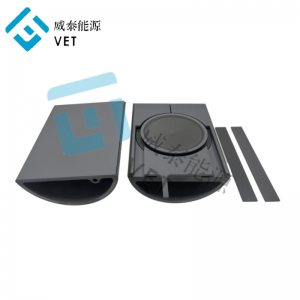

Kit de célula de combustível de hidrogênio para drone de 1000 W e 24 V

-

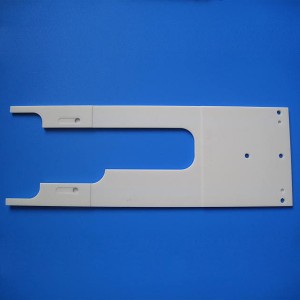

Consumíveis para equipamentos semicondutores alumina cer...

-

Rolamentos axiais impregnados com resina de grafite...

-

Corda de grafite/fibra de carbono de alta resistência para Se...

-

Pilha de célula de combustível Pemfc de 1000 W para Uav Pemfc...

-

Parte superior e inferior em meia-lua de grafite para Si...