Selamat datang ke laman web kami untuk maklumat produk dan perundingan.

laman web kami:https://www.vet-china.com/

Apabila proses pembuatan semikonduktor terus membuat penemuan, kenyataan terkenal yang dipanggil "Undang-undang Moore" telah beredar dalam industri. Ia telah dicadangkan oleh Gordon Moore, salah seorang pengasas Intel, pada tahun 1965. Kandungan terasnya ialah: bilangan transistor yang boleh ditampung pada litar bersepadu akan berganda kira-kira setiap 18 hingga 24 bulan. Undang-undang ini bukan sahaja analisis dan ramalan arah aliran pembangunan industri, tetapi juga penggerak untuk pembangunan proses pembuatan semikonduktor - semuanya adalah untuk membuat transistor dengan saiz yang lebih kecil dan prestasi yang stabil. Dari tahun 1950-an hingga sekarang, kira-kira 70 tahun, sejumlah teknologi proses BJT, MOSFET, CMOS, DMOS, dan hibrid BiCMOS dan BCD telah dibangunkan.

1. BJT

Transistor simpang bipolar (BJT), biasanya dikenali sebagai triod. Aliran cas dalam transistor adalah disebabkan terutamanya oleh resapan dan gerakan hanyut pembawa di persimpangan PN. Oleh kerana ia melibatkan aliran kedua-dua elektron dan lubang, ia dipanggil peranti bipolar.

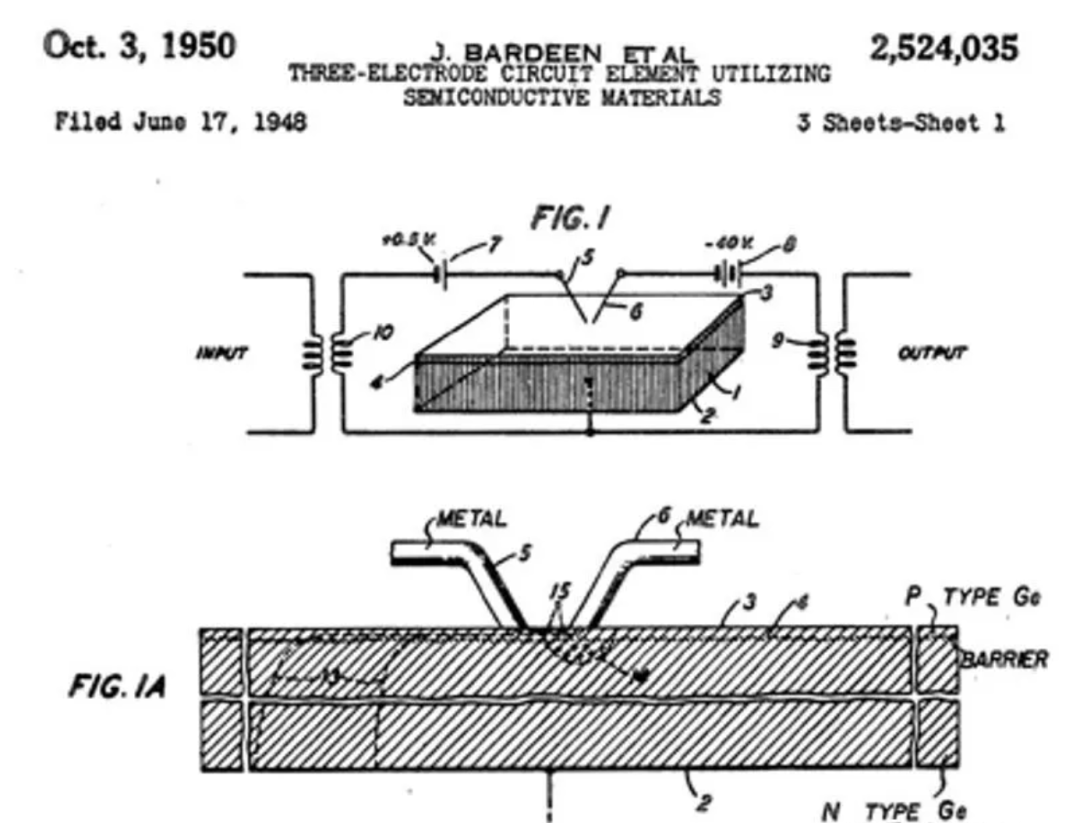

Mengimbas kembali sejarah kelahirannya. Kerana idea menggantikan triod vakum dengan penguat pepejal, Shockley mencadangkan untuk menjalankan penyelidikan asas mengenai semikonduktor pada musim panas 1945. Pada separuh kedua tahun 1945, Bell Labs menubuhkan kumpulan penyelidikan fizik keadaan pepejal yang diketuai oleh Shockley. Dalam kumpulan ini, bukan sahaja ahli fizik, tetapi juga jurutera litar dan ahli kimia, termasuk Bardeen, seorang ahli fizik teori, dan Brattain, seorang ahli fizik eksperimen. Pada Disember 1947, satu peristiwa yang dianggap sebagai peristiwa penting oleh generasi terkemudian berlaku dengan cemerlang - Bardeen dan Brattain berjaya mencipta transistor hubungan titik germanium pertama di dunia dengan penguatan semasa.

Transistor hubungan titik pertama Bardeen dan Brattain

Tidak lama selepas itu, Shockley mencipta transistor simpang bipolar pada tahun 1948. Beliau mencadangkan bahawa transistor boleh terdiri daripada dua simpang pn, satu pincang ke hadapan dan satu lagi pincang songsang, dan memperoleh paten pada Jun 1948. Pada tahun 1949, beliau menerbitkan teori terperinci kerja transistor simpang. Lebih dua tahun kemudian, saintis dan jurutera di Bell Labs membangunkan satu proses untuk mencapai pengeluaran besar-besaran transistor simpang (pencapaian pada tahun 1951), membuka era baru teknologi elektronik. Sebagai mengiktiraf sumbangan mereka kepada ciptaan transistor, Shockley, Bardeen dan Brattain bersama-sama memenangi Hadiah Nobel dalam Fizik 1956.

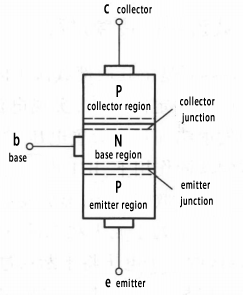

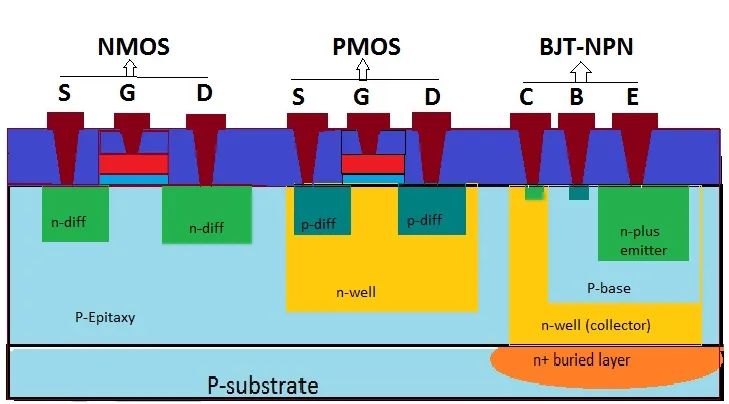

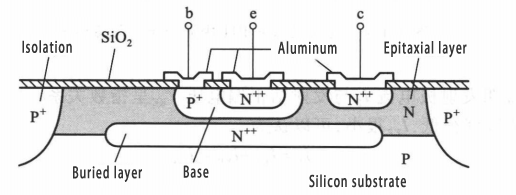

Gambar rajah struktur mudah transistor simpang bipolar NPN

Mengenai struktur transistor simpang bipolar, BJT biasa ialah NPN dan PNP. Struktur dalaman terperinci ditunjukkan dalam rajah di bawah. Kawasan semikonduktor kekotoran yang sepadan dengan pemancar ialah kawasan pemancar, yang mempunyai kepekatan doping yang tinggi; kawasan semikonduktor kekotoran yang sepadan dengan asas ialah kawasan asas, yang mempunyai lebar yang sangat nipis dan kepekatan doping yang sangat rendah; kawasan semikonduktor kekotoran yang sepadan dengan pengumpul ialah kawasan pengumpul, yang mempunyai kawasan yang besar dan kepekatan doping yang sangat rendah.

Kelebihan teknologi BJT ialah kelajuan tindak balas yang tinggi, transkonduktans tinggi (perubahan voltan input sepadan dengan perubahan arus keluaran yang besar), hingar rendah, ketepatan analog yang tinggi, dan keupayaan memandu arus yang kuat; kelemahannya ialah penyepaduan rendah (kedalaman menegak tidak boleh dikurangkan dengan saiz sisi) dan penggunaan kuasa yang tinggi.

2. MOS

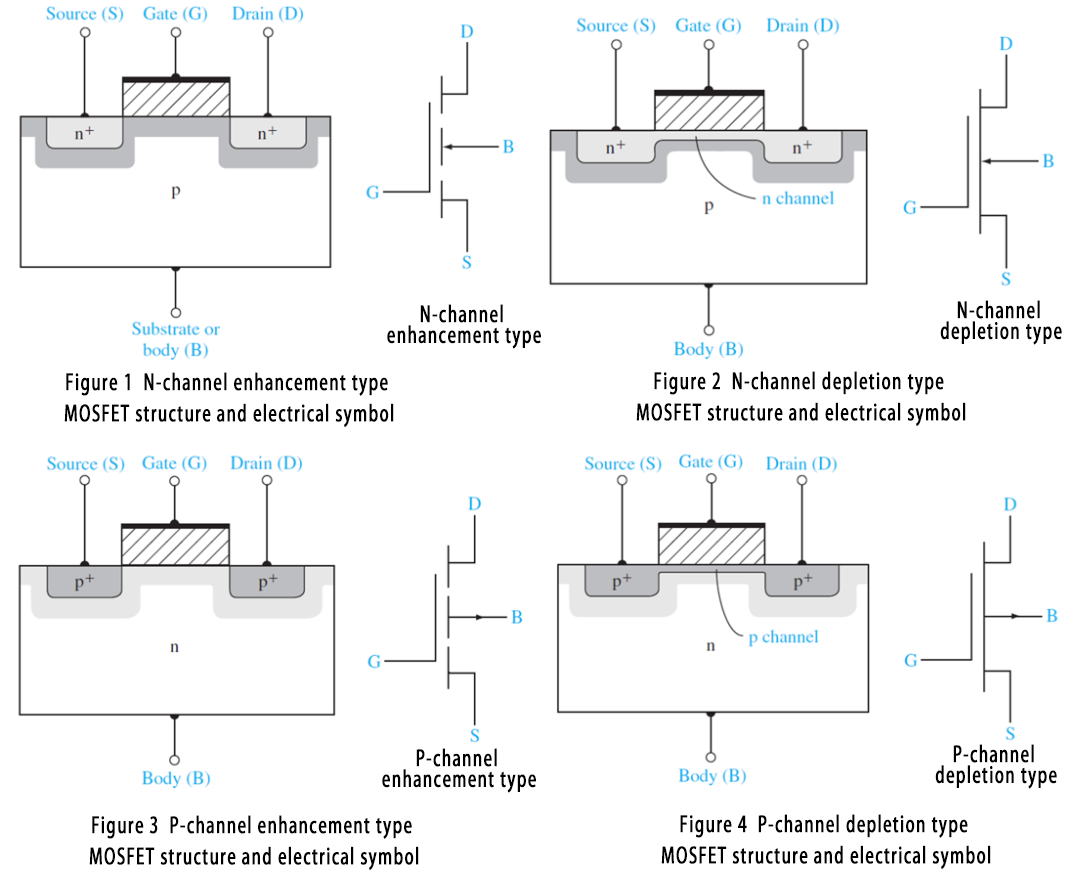

Transistor Kesan Medan Semikonduktor Oksida Logam (Metal Oxide Semiconductor FET), iaitu transistor kesan medan yang mengawal suis saluran pengalir semikonduktor (S) dengan menggunakan voltan pada pintu pagar lapisan logam (aluminium logam M) dan sumber melalui lapisan oksida (lapisan penebat O SiO2) untuk menjana kesan medan elektrik. Oleh kerana pintu pagar dan sumber, dan pintu pagar dan longkang diasingkan oleh lapisan penebat SiO2, MOSFET juga dipanggil transistor kesan medan get terlindung. Pada tahun 1962, Bell Labs secara rasmi mengumumkan pembangunan yang berjaya, yang menjadi salah satu peristiwa penting dalam sejarah pembangunan semikonduktor dan secara langsung meletakkan asas teknikal untuk kemunculan memori semikonduktor.

MOSFET boleh dibahagikan kepada saluran P dan saluran N mengikut jenis saluran konduktif. Mengikut amplitud voltan pintu, ia boleh dibahagikan kepada: jenis penyusutan-apabila voltan pintu sifar, terdapat saluran konduktif antara longkang dan sumber; jenis peningkatan-untuk peranti saluran N (P), terdapat saluran konduktif hanya apabila voltan pintu lebih besar daripada (kurang daripada) sifar, dan MOSFET kuasa terutamanya jenis peningkatan saluran N.

Perbezaan utama antara MOS dan triod termasuk tetapi tidak terhad kepada perkara berikut:

-Triodes ialah peranti bipolar kerana kedua-dua pembawa majoriti dan minoriti mengambil bahagian dalam pengaliran pada masa yang sama; manakala MOS hanya mengalirkan elektrik melalui pembawa majoriti dalam semikonduktor, dan juga dipanggil transistor unipolar.

-Triodes ialah peranti terkawal semasa dengan penggunaan kuasa yang agak tinggi; manakala MOSFET ialah peranti kawalan voltan dengan penggunaan kuasa yang rendah.

-Triodes mempunyai rintangan-on yang besar, manakala tiub MOS mempunyai rintangan-on yang kecil, hanya beberapa ratus miliohm. Dalam peranti elektrik semasa, tiub MOS biasanya digunakan sebagai suis, terutamanya kerana kecekapan MOS agak tinggi berbanding triod.

-Triodes mempunyai kos yang agak berfaedah, dan tiub MOS agak mahal.

-Kini, tiub MOS digunakan untuk menggantikan triod dalam kebanyakan senario. Hanya dalam beberapa senario kuasa rendah atau tidak sensitif kuasa, kami akan menggunakan triod mempertimbangkan kelebihan harga.

3. CMOS

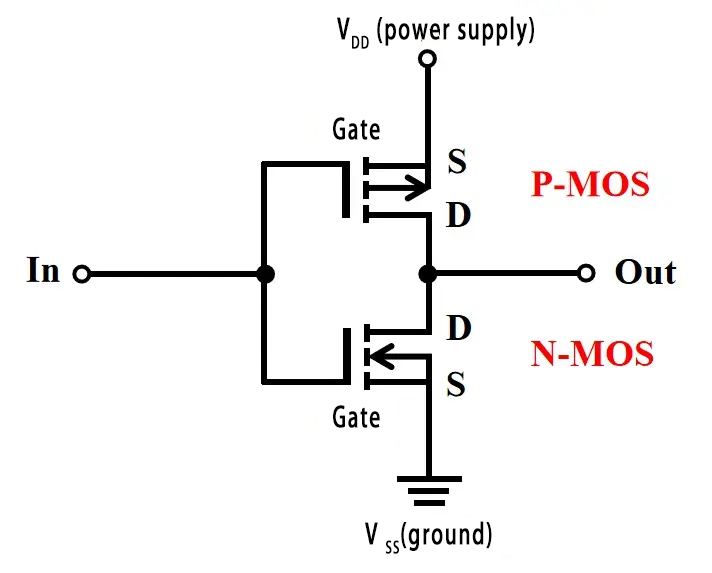

Semikonduktor Oksida Logam Pelengkap: Teknologi CMOS menggunakan transistor semikonduktor oksida logam jenis-p dan n-jenis pelengkap (MOSFET) untuk membina peranti elektronik dan litar logik. Rajah berikut menunjukkan penyongsang CMOS biasa, yang digunakan untuk penukaran "1→0" atau "0→1".

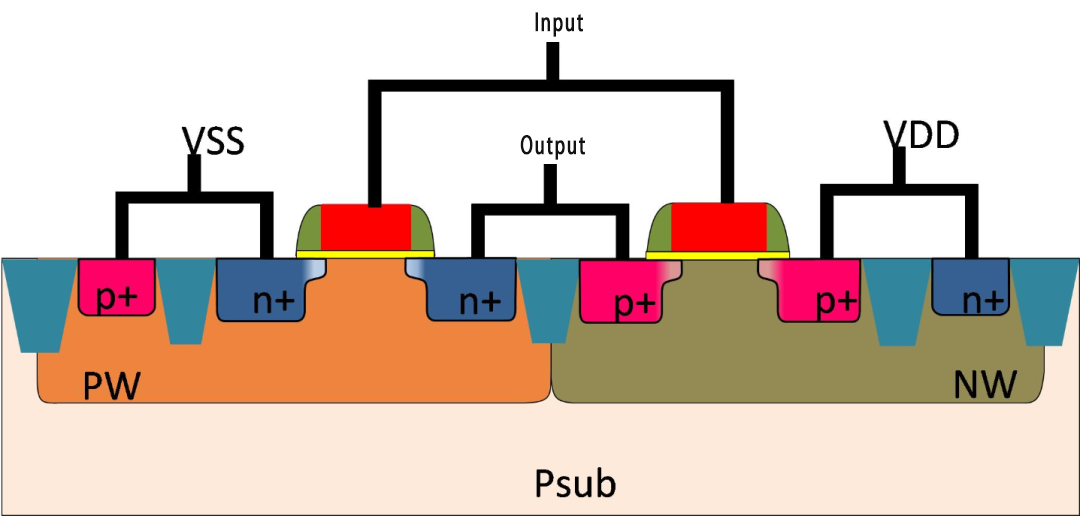

Angka berikut ialah keratan rentas CMOS biasa. Sebelah kiri ialah NMS, dan sebelah kanan ialah PMOS. Kutub G kedua-dua MOS disambungkan bersama sebagai input get biasa, dan kutub D disambungkan bersama sebagai output longkang biasa. VDD disambungkan ke sumber PMOS, dan VSS disambungkan ke sumber NMOS.

Pada tahun 1963, Wanlass dan Sah dari Fairchild Semiconductor mencipta litar CMOS. Pada tahun 1968, American Radio Corporation (RCA) membangunkan produk litar bersepadu CMOS yang pertama, dan sejak itu, litar CMOS telah mencapai pembangunan yang hebat. Kelebihannya ialah penggunaan kuasa yang rendah dan integrasi tinggi (proses STI/LOCOS boleh meningkatkan lagi integrasi); kelemahannya ialah kewujudan kesan kunci (pincang songsang simpang PN digunakan sebagai pengasingan antara tiub MOS, dan gangguan dengan mudah boleh membentuk gelung yang dipertingkatkan dan membakar litar).

4. DMOS

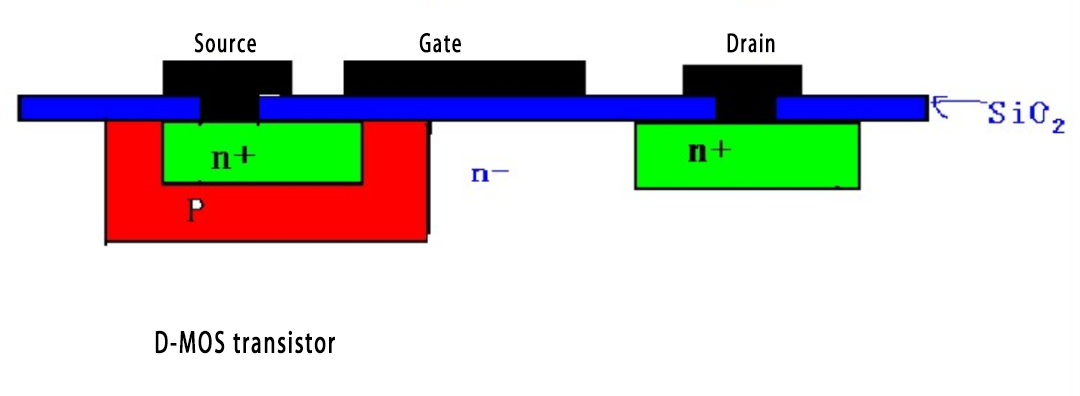

Semikonduktor Oksida Logam Tersebar Berganda: Sama seperti struktur peranti MOSFET biasa, ia juga mempunyai sumber, longkang, pintu dan elektrod lain, tetapi voltan pecahan hujung longkang adalah tinggi. Proses resapan berganda digunakan.

Rajah di bawah menunjukkan keratan rentas DMOS saluran N standard. Peranti DMOS jenis ini biasanya digunakan dalam aplikasi pensuisan sisi rendah, di mana sumber MOSFET disambungkan ke tanah. Di samping itu, terdapat DMOS saluran P. Peranti DMOS jenis ini biasanya digunakan dalam aplikasi pensuisan sisi tinggi, di mana sumber MOSFET disambungkan kepada voltan positif. Sama seperti CMOS, peranti DMOS pelengkap menggunakan MOSFET saluran N dan saluran P pada cip yang sama untuk menyediakan fungsi pensuisan pelengkap.

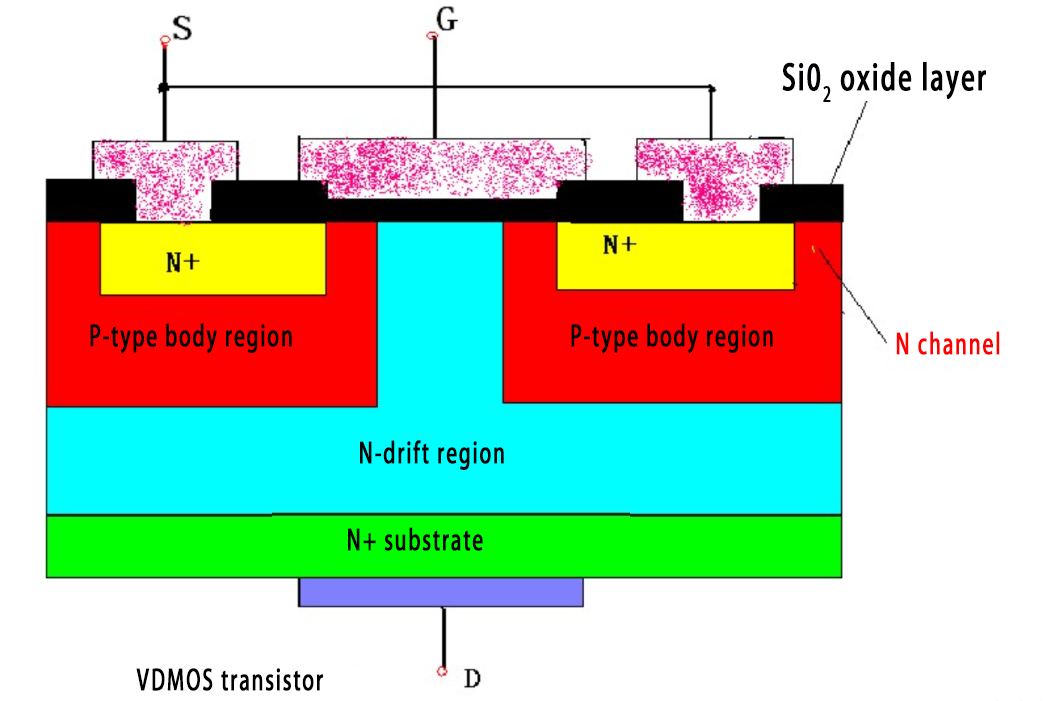

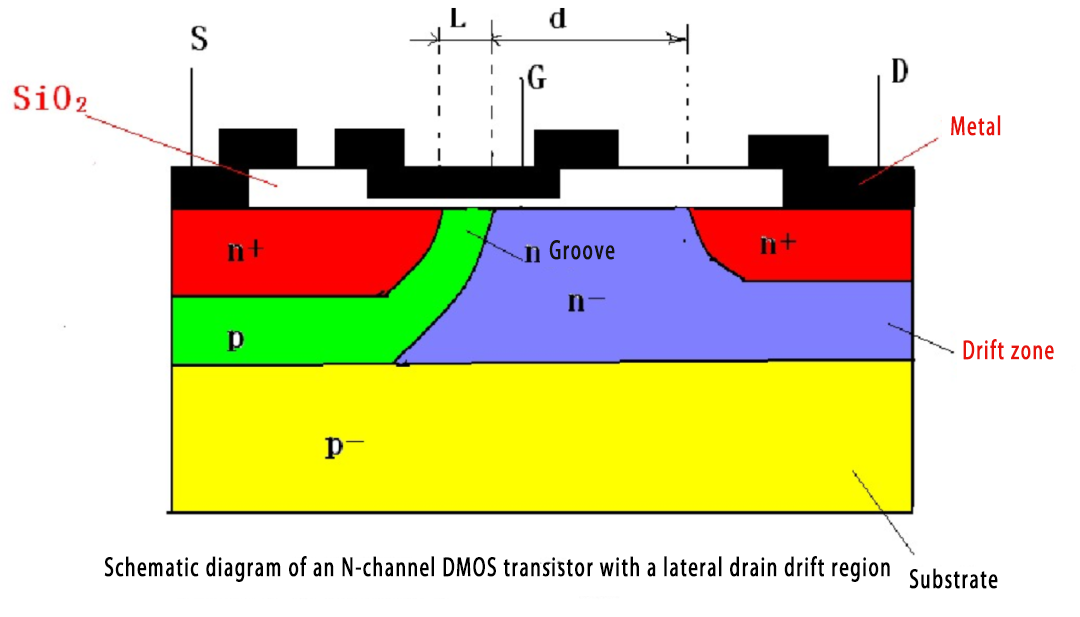

Bergantung kepada arah saluran, DMOS boleh dibahagikan kepada dua jenis, iaitu transistor kesan medan semikonduktor oksida logam oksida dua tegak menegak (Vertical Double-Diffused MOSFET) dan transistor kesan medan semikonduktor oksida logam oksida berganda sisi (Lateral Double). -MOSFET tersebar).

Peranti VDMOS direka bentuk dengan saluran menegak. Berbanding dengan peranti DMOS sisi, mereka mempunyai voltan pecahan yang lebih tinggi dan keupayaan pengendalian semasa, tetapi rintangan pada masih agak besar.

Peranti LDMOS direka bentuk dengan saluran sisi dan merupakan peranti MOSFET kuasa asimetri. Berbanding dengan peranti DMOS menegak, ia membenarkan rintangan pada yang lebih rendah dan kelajuan pensuisan yang lebih pantas.

Berbanding dengan MOSFET tradisional, DMOS mempunyai kapasitans yang lebih tinggi dan rintangan yang lebih rendah, jadi ia digunakan secara meluas dalam peranti elektronik berkuasa tinggi seperti suis kuasa, alat kuasa dan pemacu kenderaan elektrik.

5. BiCMOS

CMOS Bipolar ialah teknologi yang mengintegrasikan CMOS dan peranti bipolar pada cip yang sama pada masa yang sama. Idea asasnya ialah menggunakan peranti CMOS sebagai litar unit utama, dan menambah peranti atau litar bipolar di mana beban kapasitif yang besar diperlukan untuk digerakkan. Oleh itu, litar BiCMOS mempunyai kelebihan integrasi tinggi dan penggunaan kuasa rendah litar CMOS, dan kelebihan kelajuan tinggi dan keupayaan memandu arus kuat litar BJT.

Teknologi BiCMOS SiGe (silikon germanium) STMicroelectronics menyepadukan bahagian RF, analog dan digital pada satu cip, yang boleh mengurangkan bilangan komponen luaran dengan ketara dan mengoptimumkan penggunaan kuasa.

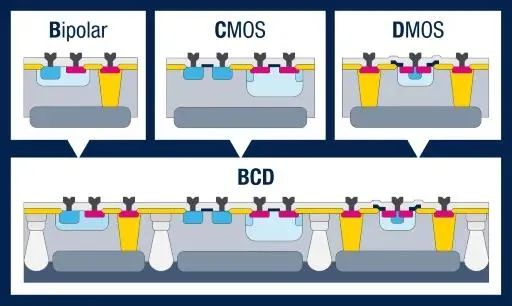

6. BCD

Bipolar-CMOS-DMOS, teknologi ini boleh membuat peranti bipolar, CMOS dan DMOS pada cip yang sama, dipanggil proses BCD, yang pertama kali berjaya dibangunkan oleh STMicroelectronics (ST) pada tahun 1986.

Bipolar sesuai untuk litar analog, CMOS sesuai untuk litar digital dan logik, dan DMOS sesuai untuk peranti kuasa dan voltan tinggi. BCD menggabungkan kelebihan ketiga-tiganya. Selepas penambahbaikan berterusan, BCD digunakan secara meluas dalam produk dalam bidang pengurusan kuasa, pemerolehan data analog dan penggerak kuasa. Menurut laman web rasmi ST, proses matang untuk BCD masih sekitar 100nm, 90nm masih dalam reka bentuk prototaip, dan teknologi 40nmBCD adalah milik produk generasi seterusnya yang sedang dibangunkan.

Masa siaran: Sep-10-2024