Wëllkomm op eiser Websäit fir Produktinformatioun a Berodung.

Eis Websäit:https://www.vet-china.com/

Wéi Hallefleitfabrikatiounsprozesser weider Duerchbroch maachen, ass eng berühmt Ausso mam Numm "Moore's Law" an der Industrie zirkuléiert. Et gouf vum Gordon Moore, ee vun de Grënner vun Intel, am Joer 1965 proposéiert. Seng Kärinhalt ass: d'Zuel vun den Transistoren, déi op engem integréierte Circuit ënnerbruecht kënne ginn, verduebelt ongeféier all 18 bis 24 Méint. Dëst Gesetz ass net nëmmen eng Analyse a Prognose vun der Entwécklung Trend vun der Industrie, mä och eng dreiwend Kraaft fir d'Entwécklung vun semiconductor Fabrikatioun Prozesser - alles ass Transistoren mat méi kleng Gréisst a stabil Leeschtung ze maachen. Vun den 1950er bis haut, ongeféier 70 Joer, sinn am Ganzen BJT, MOSFET, CMOS, DMOS, an Hybrid BiCMOS a BCD Prozesstechnologien entwéckelt ginn.

1. BJT

Bipolare Kräizung Transistor (BJT), allgemeng bekannt als Triode. De Ladefluss am Transistor ass haaptsächlech wéinst der Diffusioun an der Driftbewegung vun Träger um PN Kräizung. Well et de Flux vu béiden Elektronen a Lächer involvéiert, gëtt et e bipolare Apparat genannt.

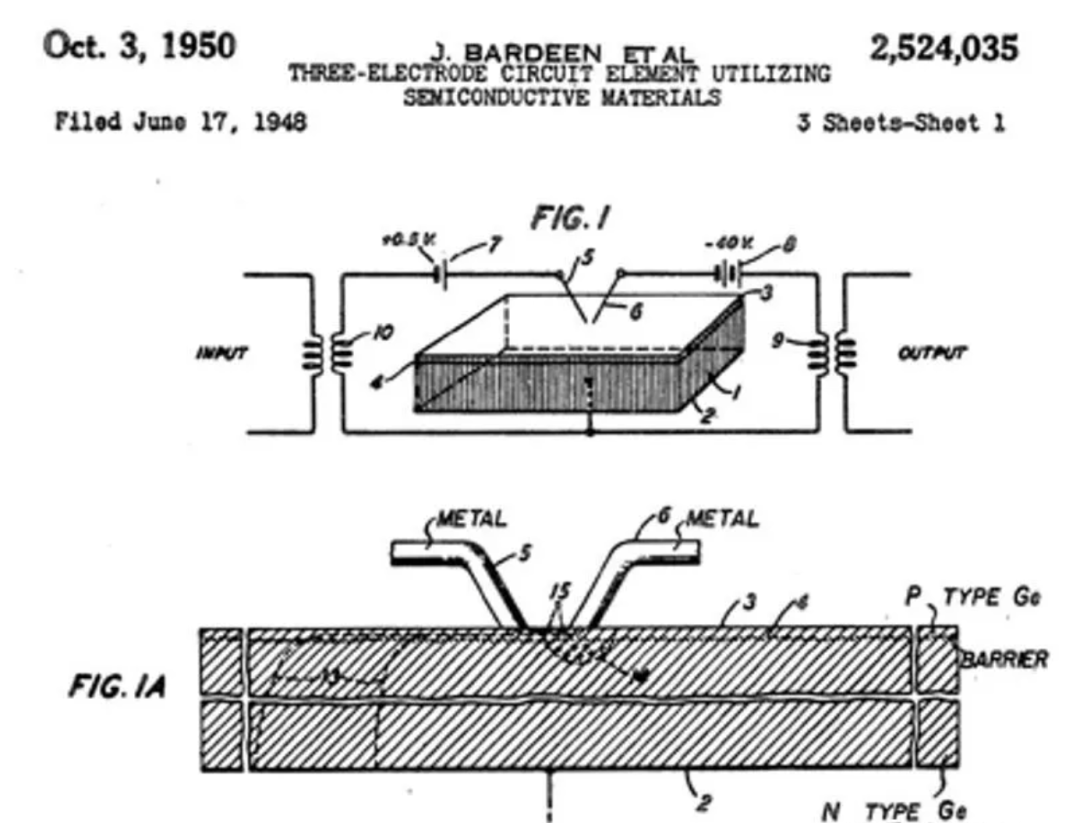

Réckbléck op d'Geschicht vu senger Gebuert. Wéinst der Iddi fir Vakuumtrioden duerch zolidd Verstärker z'ersetzen, huet Shockley proposéiert d'Basisfuerschung iwwer Halbleiteren am Summer vum 1945 auszeféieren. An dëser Grupp sinn net nëmmen Physiker, mee och Circuitingenieuren a Chemiker, dorënner de Bardeen, en theoretesche Physiker, an de Brattain, en experimentelle Physiker. Am Dezember 1947 ass en Event dat als Meilesteen vu spéider Generatiounen ugesi gouf brillant geschitt - Bardeen a Brattain hunn erfollegräich den éischten Germanium Punktkontakt Transistor mat aktueller Verstäerkung erfonnt.

Bardeen a Brattain säin éischte Punkt-Kontakt Transistor

Kuerz drop huet de Shockley de bipolare Kräizungstransistor erfonnt an 1948. Hien huet virgeschloen datt den Transistor aus zwee pn-Kräizungen zesummegesat ka sinn, eng no vir an déi aner ëmgedréint, a krut e Patent am Juni 1948. 1949 huet hien déi detailléiert Theorie publizéiert. vun der Aarbecht vun der Kräizung Transistor. Méi wéi zwee Joer méi spéit hunn d'Wëssenschaftler an d'Ingenieuren vun Bell Labs e Prozess entwéckelt fir d'Massproduktioun vu Kräizungstransistoren z'erreechen (Meilesteen am Joer 1951), an eng nei Ära vun der elektronescher Technologie opzemaachen. Als Unerkennung fir hir Bäiträg zu der Erfindung vun den Transistoren hunn Shockley, Bardeen a Brattain zesummen den 1956 Nobelpräis an der Physik gewonnen.

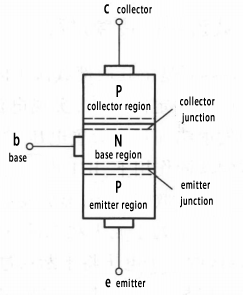

Einfach strukturell Diagramm vum NPN bipolare Kräizungstransistor

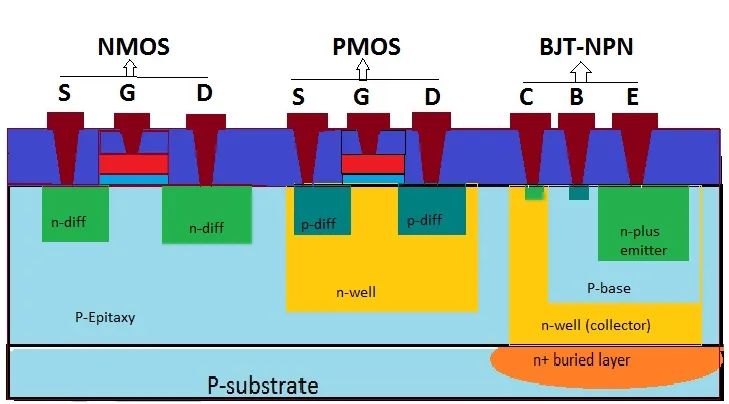

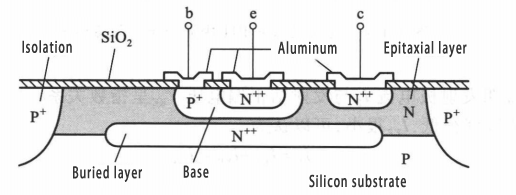

Wat d'Struktur vu bipolare Kräizungstransistoren ugeet, sinn allgemeng BJTs NPN a PNP. Déi detailléiert intern Struktur gëtt an der Figur hei ënnen gewisen. D'Gëftstoffer Hallefleitregioun entsprécht dem Emitter ass d'Emitterregioun, déi eng héich Dopingkonzentratioun huet; d'Gëftstoffer Hallefleitregioun entsprécht der Basis ass d'Basisregioun, déi eng ganz dënn Breet an eng ganz niddereg Dopingkonzentratioun huet; d'Gëftstoffer Halbleiterregioun, déi dem Sammler entsprécht, ass d'Sammlerregioun, déi e grousst Gebitt an eng ganz niddereg Dopingkonzentratioun huet.

D'Virdeeler vun der BJT Technologie sinn héich Reaktiounsgeschwindegkeet, héich Transkonduktanzen (Input Spannungsännerungen entspriechen grouss Ausgangsstroum Ännerungen), niddereg Kaméidi, héich Analog Genauegkeet, a staark Stroumfahrtfäegkeet; d'Nodeeler sinn niddereg Integratioun (vertikal Déift kann net mat saitlech Gréisst reduzéiert ginn) an héich Muecht Konsum.

2. MOS

Metal Oxide Semiconductor Field Effect Transistor (Metal Oxide Semiconductor FET), dat heescht e Feldeffekttransistor, deen de Schalter vum Hallefleitungskanal (S) kontrolléiert andeems d'Spannung op d'Paart vun der Metallschicht (M-Metall Aluminium) an de Quell duerch d'Oxidschicht (O-Isoléierschicht SiO2) fir den Effekt vum elektresche Feld ze generéieren. Zënter datt de Paart an d'Quell, an d'Paart an d'Drain duerch d'SiO2 Isoléierschicht isoléiert sinn, gëtt MOSFET och en isoléierte Paart Feldeffekt Transistor genannt. 1962 huet d'Bell Labs offiziell déi erfollegräich Entwécklung ugekënnegt, déi ee vun de wichtegste Meilesteen an der Geschicht vun der Halbleiterentwécklung gouf an direkt den technesche Grondlag fir d'Entstoe vum Halbleiter-Erënnerung geluecht huet.

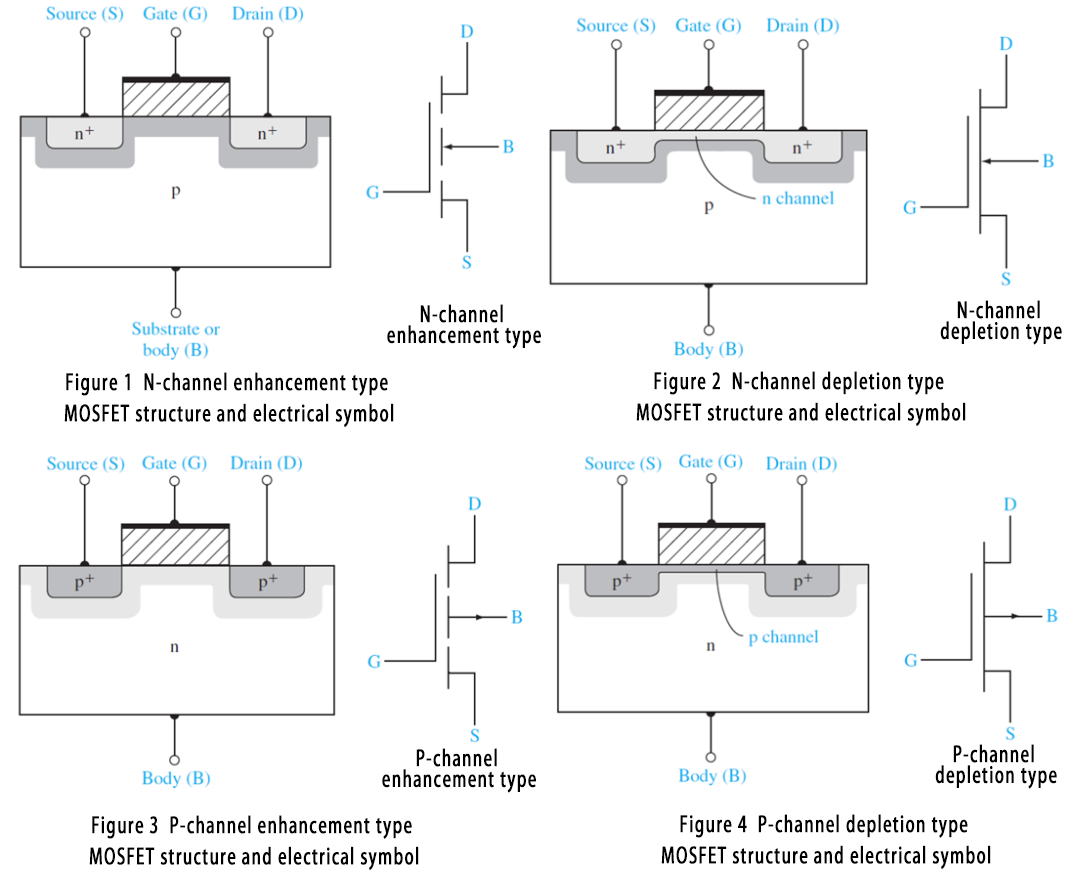

MOSFET kann a P-Kanal an N-Kanal opgedeelt ginn no der konduktiver Kanaltyp. No der Paart Spannung Amplituden, kann et ënnerdeelt ginn an: Ausschöpfung Typ-wann d'Paart Spannung null ass, gëtt et e konduktiv Kanal tëscht dem Drain an der Quell; Verbesserungstyp - fir N (P) Kanal Geräter gëtt et e konduktiven Kanal nëmmen wann d'Paartspannung méi grouss ass wéi (manner wéi) Null, a Kraaft MOSFET ass haaptsächlech N Kanal Verbesserungstyp.

D'Haaptdifferenzen tëscht MOS an Triode enthalen awer sinn net limitéiert op déi folgend Punkten:

-Triodes sinn bipolar Apparater well souwuel Majoritéit a Minoritéit Träger an der Leedung gläichzäiteg matmaachen; während MOS nëmmen Elektrizitéit duerch Majoritéit Carrier an Hallefleit féiert, a gëtt och en unipolare Transistor genannt.

-Triodes sinn aktuell-kontrolléiert Apparater mat relativ héich Muecht Konsum; wärend MOSFETs Spannungskontrolléiert Geräter mat nidderegem Stroumverbrauch sinn.

-Triodes hu grouss On-Resistenz, während MOS-Röhre kleng On-Resistenz hunn, nëmmen e puer honnert Milliohms. An aktuellen elektreschen Apparater ginn MOS-Réier allgemeng als Schalter benotzt, haaptsächlech well d'Effizienz vu MOS relativ héich ass am Verglach mat Trioden.

-Triodes hunn e relativ avantagéis Käschte, a MOS-Réier si relativ deier.

-Haut ginn MOS-Réier benotzt fir Trioden an de meeschte Szenarien ze ersetzen. Nëmmen an e puer niddereg-Muecht oder Muecht-onsensibel Szenarie, wäerte mir Triodes benotzen de Präis Virdeel betruecht.

3. CMOS

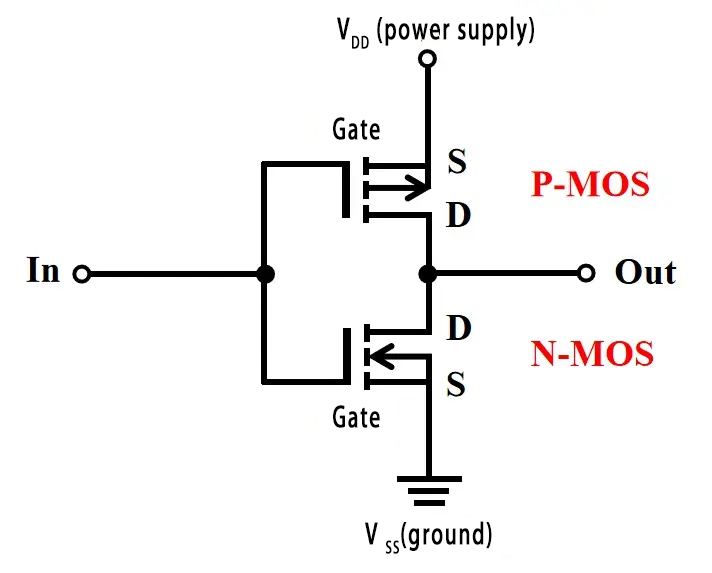

Komplementär Metal Oxide Semiconductor: CMOS Technologie benotzt komplementär p-Typ an n-Typ Metalloxid Hallefleit Transistoren (MOSFETs) fir elektronesch Geräter a Logikkreesser ze bauen. Déi folgend Figur weist e gemeinsame CMOS Inverter, dee fir "1→0" oder "0→1" Konversioun benotzt gëtt.

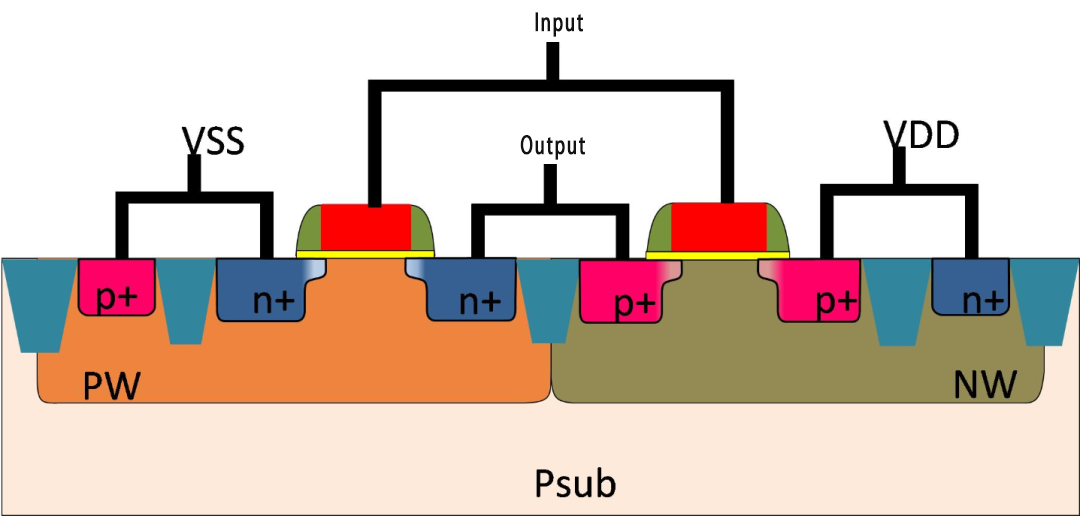

Déi folgend Figur ass eng typesch CMOS Querschnitt. Déi lénks Säit ass NMS, an déi riets Säit ass PMOS. D'G Pole vun deenen zwee MOS si matenee verbonnen als e gemeinsame Gate-Input, an d'D Pole si matenee verbonnen als e gemeinsame Drainoutput. VDD ass mat der Quell vun PMOS ugeschloss, an VSS ass mat der Quell vun NMOS ugeschloss.

Am Joer 1963 hunn de Wanlass a Sah vu Fairchild Semiconductor den CMOS Circuit erfonnt. Am Joer 1968 huet d'American Radio Corporation (RCA) den éischte CMOS integréierte Circuitprodukt entwéckelt, an zënterhier huet de CMOS Circuit eng grouss Entwécklung erreecht. Seng Virdeeler sinn niddereg Muecht Konsum an héich Integratioun (STI / LOCOS Prozess kann Integratioun weider verbesseren); säin Nodeel ass d'Existenz vun engem Sperreffekt (PN-Kräizung ëmgedréint Bias gëtt als Isolatioun tëscht MOS-Röhre benotzt, an d'Interferenz kann einfach eng verstäerkte Loop bilden an de Circuit verbrennen).

4. DMOS

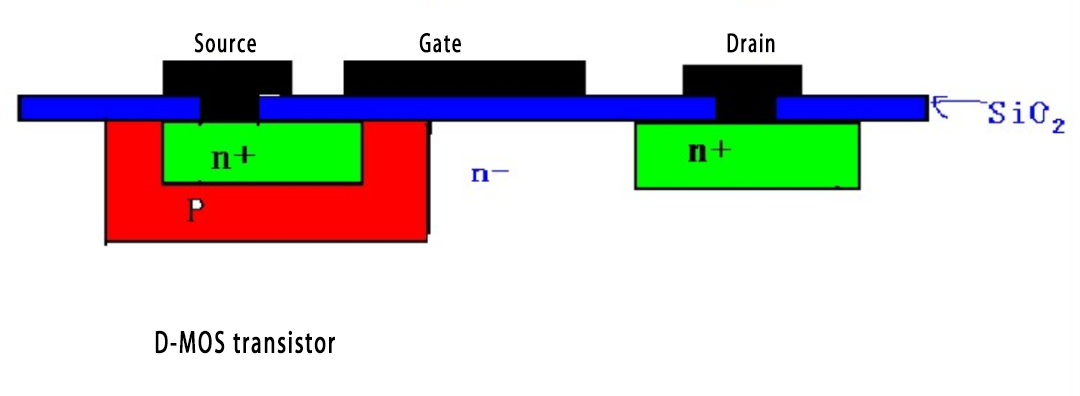

Double-Diffused Metal Oxide Semiconductor: Ähnlech wéi d'Struktur vun gewéinleche MOSFET-Geräter, huet et och Quell, Drain, Gate an aner Elektroden, awer d'Decomptespannung vum Drain Enn ass héich. Duebel Diffusiounsprozess gëtt benotzt.

D'Figur hei ënnen weist de Querschnitt vun engem Standard N-Kanal DMOS. Dës Zort DMOS Apparat gëtt normalerweis a Low-Side Schaltapplikatiounen benotzt, wou d'Quell vum MOSFET mam Buedem verbonnen ass. Zousätzlech gëtt et e P-Kanal DMOS. Dës Zort DMOS Apparat gëtt normalerweis an High-Side Schaltapplikatiounen benotzt, wou d'Quell vum MOSFET mat enger positiver Spannung ugeschloss ass. Ähnlech wéi CMOS benotzen komplementär DMOS-Geräter N-Kanal a P-Kanal MOSFETs um selwechten Chip fir komplementär Schaltfunktiounen ze bidden.

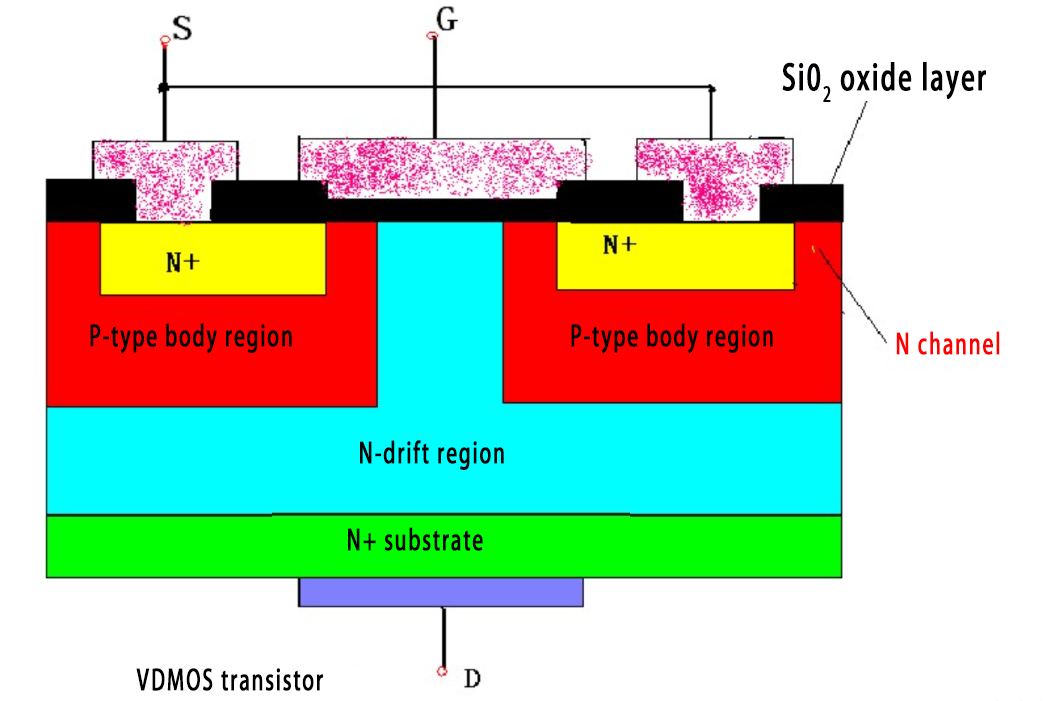

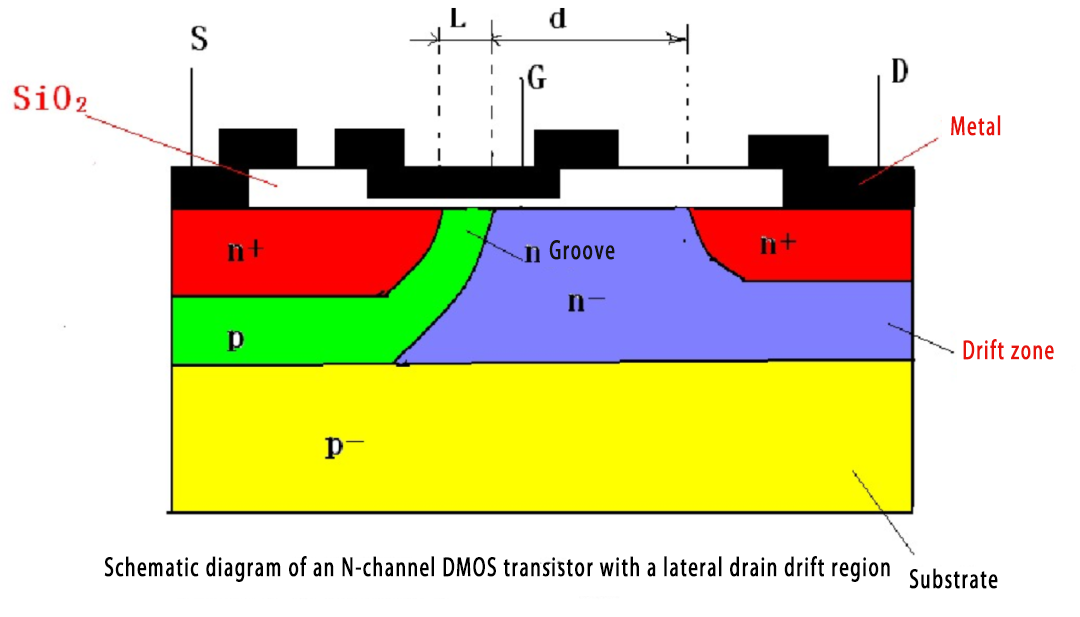

Ofhängeg vun der Richtung vum Kanal, kann DMOS an zwou Zorte ënnerdeelt ginn, nämlech vertikalen duebel-diffuséierten Metalloxid-Hallefferfeldeffekttransistor VDMOS (Vertical Double-Diffused MOSFET) a lateral Double-diffuséierten Metalloxid-Hallefferfeldeffekttransistor LDMOS (Lateral Double-Diffused MOSFET) -Diffuséiert MOSFET).

VDMOS-Geräter si mat engem vertikale Kanal entworf. Am Verglach mat lateralen DMOS-Geräter hu se méi héich Decomptespannung an aktuell Handhabungsfäegkeeten, awer d'On-Resistenz ass nach ëmmer relativ grouss.

LDMOS-Geräter si mat engem laterale Kanal entworf a sinn asymmetresch Kraaft MOSFET-Geräter. Am Verglach mat vertikalen DMOS-Geräter erlaben se méi niddereg On-Resistenz a méi séier Schaltgeschwindegkeet.

Am Verglach mat traditionelle MOSFETs huet DMOS méi héich Kapazitéit a méi niddereg Resistenz, sou datt et vill an héich-Muecht elektronesch Geräter wéi Kraaftschalter, Power Tools an elektresch Gefierer benotzt gëtt.

5. BiCMOS

Bipolar CMOS ass eng Technologie déi CMOS a bipolare Geräter zur selwechter Zäit um selwechten Chip integréiert. Seng Basis Iddi ass CMOS Geräter als Haaptenheet Circuit ze benotzen, a bipolare Apparater oder Circuiten derbäi wou grouss capacitive Laascht gefuer muss ginn. Dofir, BiCMOS Kreesleef hunn d'Virdeeler vun héich Integratioun an niddereg Muecht Konsum vun CMOS Kreesleef, an d'Virdeeler vun héich Vitesse a staark aktuell dreiwend Kënnen vun BJT Kreesleef.

STMicroelectronics 'BiCMOS SiGe (Silicon Germanium) Technologie integréiert RF, Analog an digital Deeler op engem eenzegen Chip, wat d'Zuel vun externen Komponenten wesentlech reduzéiere kann an d'Energieverbrauch optimiséieren.

6. BCD

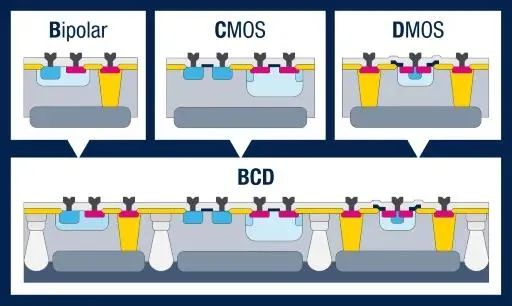

Bipolar-CMOS-DMOS, dës Technologie kann bipolare, CMOS- an DMOS-Geräter um selwechten Chip maachen, BCD-Prozess genannt, deen als éischt erfollegräich vun STMicroelectronics (ST) am Joer 1986 entwéckelt gouf.

Bipolar ass gëeegent fir Analog Circuiten, CMOS ass gëeegent fir digital a logesch Circuiten, an DMOS ass gëeegent fir Muecht an Héichspannung Apparater. BCD kombinéiert d'Virdeeler vun den dräi. No kontinuéierlecher Verbesserung gëtt BCD vill a Produkter an de Beräicher Power Management, Analog Daten Acquisitioun a Kraaftaktuatoren benotzt. Nom ST senger offizieller Websäit ass de reife Prozess fir BCD nach ëmmer ongeféier 100nm, 90nm ass nach ëmmer am Prototyp Design, an 40nmBCD Technologie gehéiert zu sengen nächste Generatioun Produkter ënner Entwécklung.

Post Zäit: Sep-10-2024