De VET Energy 12-Zoll SOI-Wafer ass en héichperformant Hallefleiter-Substratmaterial, dat fir seng exzellent elektresch Eegeschaften a seng eenzegaarteg Struktur héich beléift ass. VET Energy benotzt fortgeschratt SOI-Wafer-Fabrikatiounsprozesser fir sécherzestellen, datt de Wafer extrem niddrege Leckstroum, héich Geschwindegkeet a Stralungsbeständegkeet huet, wat eng solid Basis fir Är héichperformant integréiert Schaltungen ubitt.

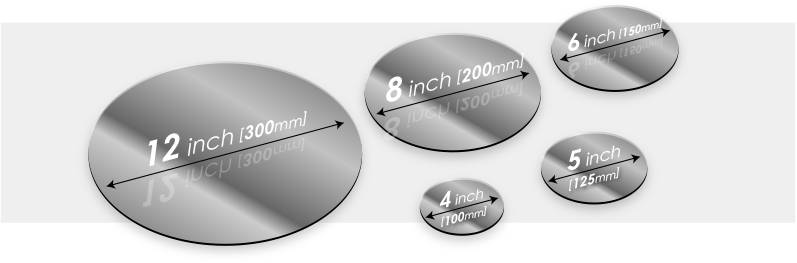

D'Produktlinn vu VET Energy beschränkt sech net op SOI-Waferen. Mir bidden och eng breet Palette vu Hallefleeder-Substratmaterialien, dorënner Si-Wafer, SiC-Substrat, SiN-Substrat, Epi-Wafer, etc., souwéi nei Hallefleedermaterialien mat enger breeder Bandlück wéi Galliumoxid Ga2O3 an AlN-Wafer. Dës Produkter kënnen den Uwendungsbedürfnisser vu verschiddene Clienten an der Leeschtungselektronik, HF, Sensoren an anere Beräicher erfëllen.

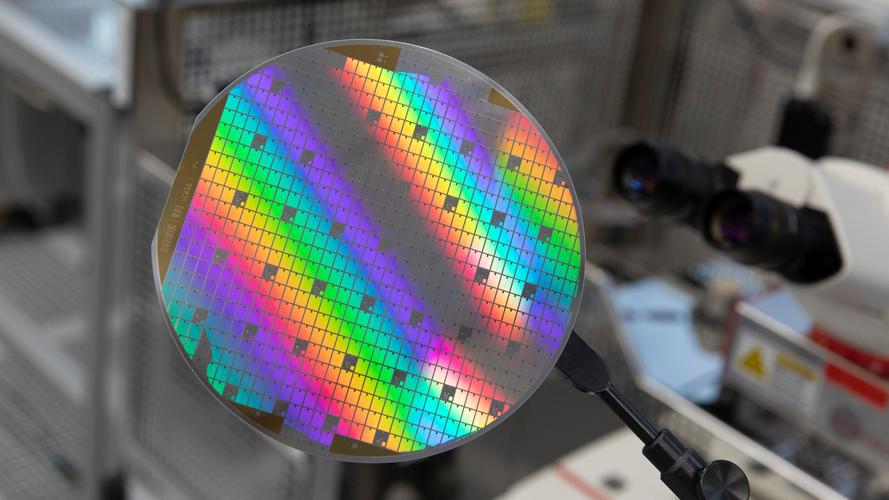

Mat Fokus op Exzellenz benotzen eis SOI-Waferen och fortgeschratt Materialien wéi Galliumoxid Ga2O3, Kassetten an AlN-Waferen, fir Zouverlässegkeet an Effizienz op all operationellen Niveau ze garantéieren. Vertraut op VET Energy fir modern Léisungen ze bidden, déi de Wee fir technologesch Fortschrëtter fräimaachen.

Entlooss de Potenzial vun Ärem Projet mat der iwwerleeëner Leeschtung vun de VET Energy 12-Zoll SOI-Waferen. Verbessert Är Innovatiounsfäegkeeten mat Waferen, déi Qualitéit, Präzisioun an Innovatioun verkierperen an d'Grondlag fir den Erfolleg am dynamesche Beräich vun der Hallefleedertechnologie leeën. Wielt VET Energy fir Premium SOI-Waferléisungen, déi d'Erwaardungen iwwertreffen.

WAFEREN-SPECIFIKATIOUNEN

*n-Pm=n-Typ Pm-Grad, n-Ps=n-Typ Ps-Grad, Sl=Hallefisoléierend

| Artikel | 8-Zoll | 6-Zoll | 4-Zoll | ||

| nP | n-Pm | n-Ps | SI | SI | |

| TTV(GBIR) | ≤6µm | ≤6µm | |||

| Béi(GF3YFCD) - Absolutwäert | ≤15μm | ≤15μm | ≤25μm | ≤15μm | |

| Verdreiwung (GF3YFER) | ≤25μm | ≤25μm | ≤40μm | ≤25μm | |

| LTV(SBIR) - 10mmx10mm | <2μm | ||||

| Waferrand | Ofschrägung | ||||

Uewerflächenofschloss

*n-Pm=n-Typ Pm-Grad, n-Ps=n-Typ Ps-Grad, Sl=Hallefisoléierend

| Artikel | 8-Zoll | 6-Zoll | 4-Zoll | ||

| nP | n-Pm | n-Ps | SI | SI | |

| Uewerflächenfinish | Duebelsäiteg Optesch Politur, Si-Face CMP | ||||

| Uewerflächenrauheet | (10µm x 10µm) Si-FaceRa≤0,2nm | (5µmx5µm) Si-Face Ra≤0,2nm | |||

| Kantchips | Keen erlaabt (Längt a Breet ≥0,5 mm) | ||||

| Aréckungen | Keen erlaabt | ||||

| Kratzer (Si-Face) | Quantitéit ≤5, Kumulativ | Quantitéit ≤5, Kumulativ | Quantitéit ≤5, Kumulativ | ||

| Rëss | Keen erlaabt | ||||

| Randausgrenzung | 3mm | ||||

-

Waasserstoffbrennstoffzellen-Stapelsystemer kënnen personaliséiert ginn...

-

Waasserstoffbrennstoffzellen verkaaft vu Pem Stack Drone Fue...

-

220w Waasserstoff Brennstoffzellgenerator 24v Pemfc Sta...

-

Waasserstoff-Brennstoffzell-Stack fir Waasserstoff-Dronen

-

Gold a Sëlwer Gossform Silikonform, Si ...

-

1kw Brennstoffzellen-Stack fir Drohnen an E-Bikes