製品情報やご相談については、当社の Web サイトへようこそ。

私たちのウェブサイト:https://www.vet-china.com/

半導体製造プロセスが進歩を続ける中、「ムーアの法則」と呼ばれる有名な言葉が業界で広まっています。これは、インテルの創設者の 1 人であるゴードン・ムーアによって 1965 年に提案されました。その中心的な内容は、集積回路上に収容できるトランジスタの数が約 18 ~ 24 か月ごとに 2 倍になるというものです。この法律は、業界の発展傾向の分析と予測であるだけでなく、半導体製造プロセスの発展の原動力でもあります。すべては、より小型で安定した性能のトランジスタを作るためです。 1950 年代から現在までの約 70 年間に、BJT、MOSFET、CMOS、DMOS、BiCMOS と BCD のハイブリッドプロセス技術が開発されてきました。

1.BJT

バイポーラ接合トランジスタ (BJT)、一般に三極管として知られています。トランジスタ内の電荷の流れは主に、PN 接合におけるキャリアの拡散とドリフト運動によるものです。電子と正孔の両方が流れるため、バイポーラデバイスと呼ばれます。

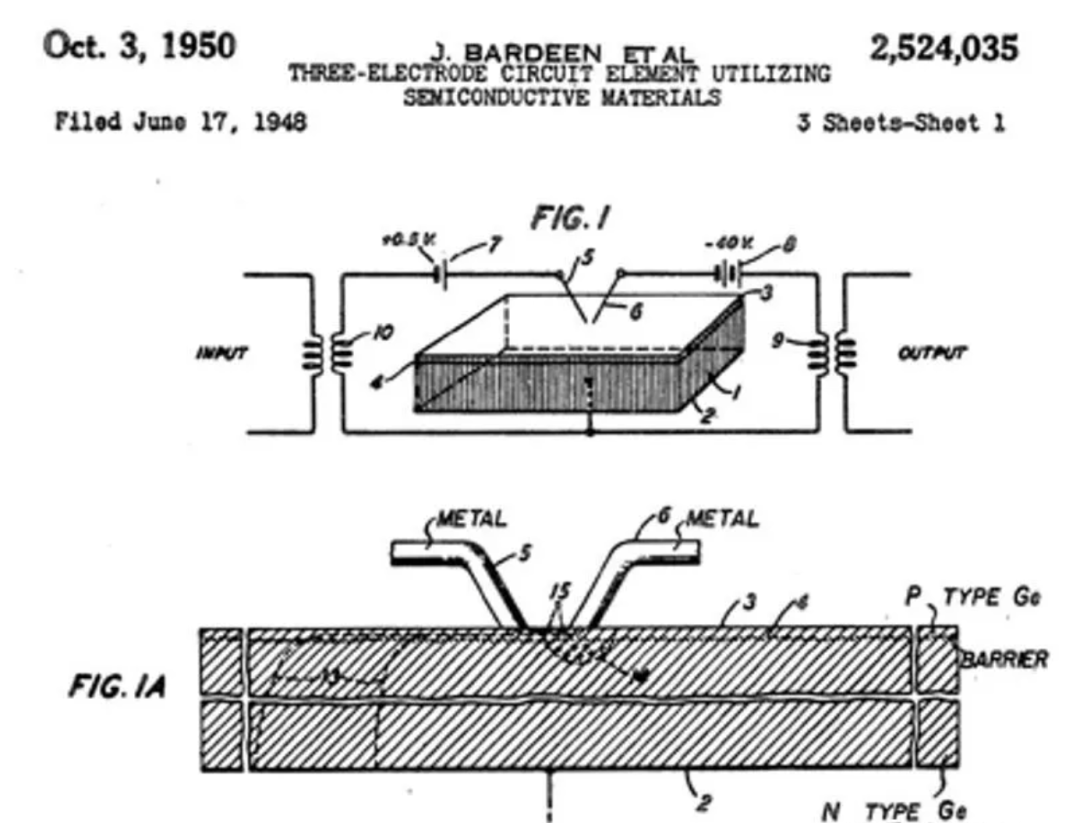

その誕生の歴史を振り返ります。真空三極管を固体増幅器に置き換えるというアイデアのため、ショックレーは 1945 年の夏に半導体の基礎研究を行うことを提案しました。 1945 年後半、ベル研究所はショックレーをリーダーとする固体物理研究グループを設立しました。このグループには、物理学者だけでなく、理論物理学者のバーディーンや実験物理学者のブラッテンを含む回路技術者や化学者もいます。 1947 年 12 月、後の世代にとって画期的な出来事と考えられる出来事が見事に起こりました。バーディーンとブラッテンは、電流増幅機能を備えた世界初のゲルマニウム点接触トランジスタの発明に成功しました。

バーディーンとブラッテンによる初の点接触トランジスタ

その後間もなく、ショックレーは 1948 年にバイポーラ接合トランジスタを発明しました。彼はトランジスタが 2 つの pn 接合 (一方は順バイアス、もう一方は逆バイアス) で構成できることを提案し、1948 年 6 月に特許を取得しました。1949 年に彼は詳細な理論を発表しました。接合トランジスタの動作について説明します。 2 年以上後、ベル研究所の科学者とエンジニアは接合型トランジスタの大量生産 (1951 年のマイルストーン) を達成するプロセスを開発し、電子技術の新時代を切り開きました。トランジスタの発明への貢献が認められ、ショックレー、バーディーン、ブラッテンは共同で 1956 年のノーベル物理学賞を受賞しました。

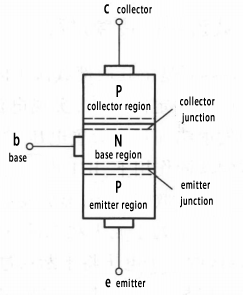

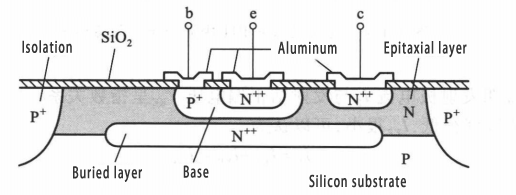

NPNバイポーラ接合トランジスタの簡易構造図

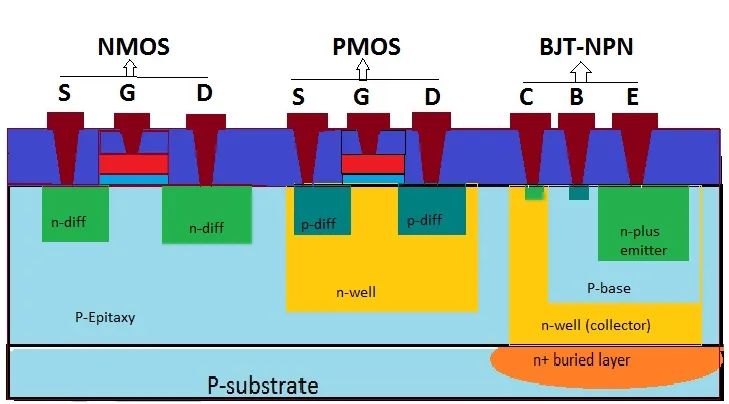

バイポーラ接合トランジスタの構造に関しては、一般的な BJT は NPN と PNP です。詳細な内部構造を下図に示します。エミッタに相当する不純物半導体領域は、不純物濃度が高いエミッタ領域である。ベースに相当する不純物半導体領域はベース領域であり、その幅は非常に薄く、ドーピング濃度は非常に低い。コレクタに相当する不純物半導体領域はコレクタ領域であり、面積が大きく不純物濃度が非常に低い。

BJT テクノロジーの利点は、高い応答速度、高い相互コンダクタンス (入力電圧の変化が大きな出力電流の変化に対応する)、低ノイズ、高いアナログ精度、および強力な電流駆動能力です。欠点は、集積度が低いこと (横方向のサイズでは垂直方向の奥行きを減らすことができない) と消費電力が高いことです。

2.モス

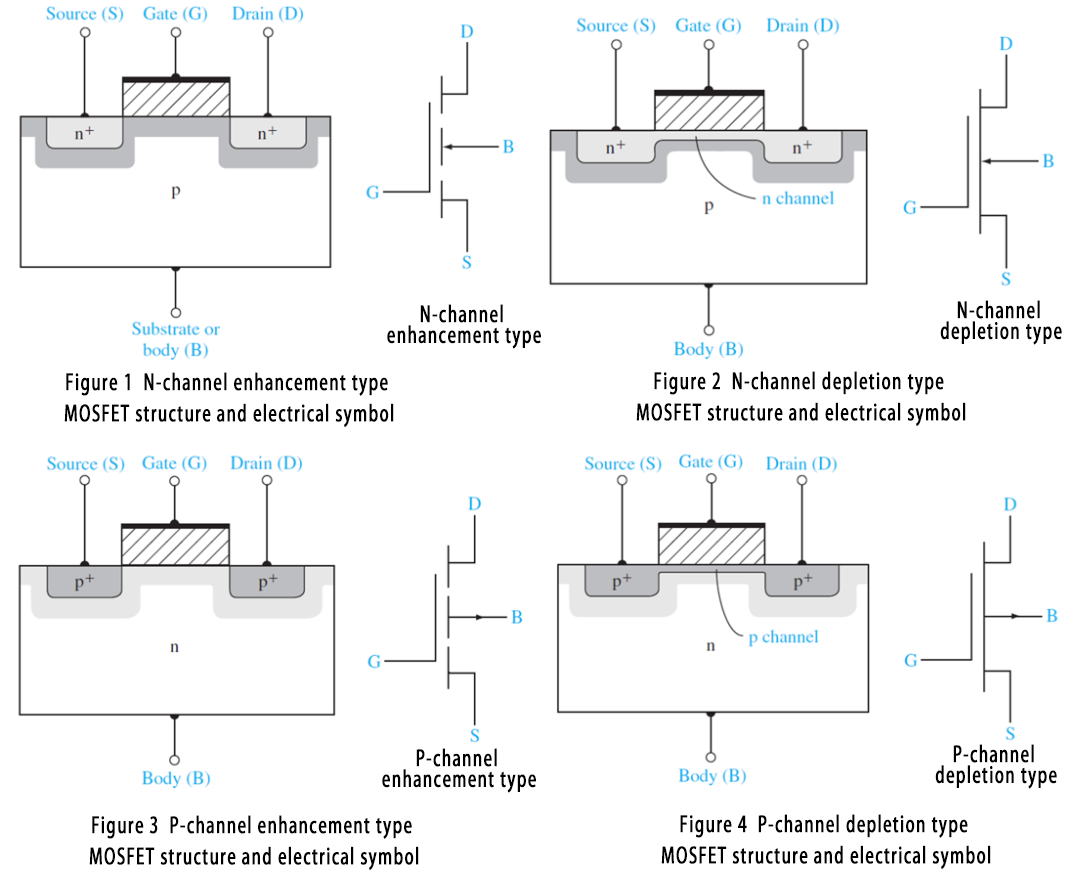

金属酸化物半導体電界効果トランジスタ (金属酸化物半導体 FET)、つまり、金属層 (M 金属アルミニウム) のゲートに電圧を印加することによって、半導体 (S) 導電チャネルのスイッチを制御する電界効果トランジスタです。酸化物層 (O 絶縁層 SiO2) を介してソースを供給し、電界の効果を生成します。 MOSFETはゲートとソース、ゲートとドレインがSiO2絶縁層で分離されているため、絶縁ゲート型電界効果トランジスタとも呼ばれます。 1962 年、ベル研究所は開発の成功を正式に発表しました。これは半導体開発の歴史の中で最も重要なマイルストーンの 1 つとなり、半導体メモリの出現の技術的基盤を直接築きました。

MOSFETは、導電チャネルの種類に応じてPチャネルとNチャネルに分類できます。ゲート電圧の振幅に従って、デプレッション型 - ゲート電圧がゼロの場合、ドレインとソースの間に導電チャネルが存在します。エンハンスメント型 - N (P) チャネルデバイスの場合、ゲート電圧がゼロより大きい (小さい) 場合にのみ導電チャネルが存在し、パワー MOSFET は主に N チャネルエンハンスメント型です。

MOS と三極管の主な違いには次の点が含まれますが、これらに限定されません。

- 三極管は、多数キャリアと少数キャリアの両方が同時に伝導に参加するため、バイポーラデバイスです。一方、MOS は半導体内の多数キャリアを介してのみ電気を伝導し、ユニポーラ トランジスタとも呼ばれます。

-三極管は、比較的消費電力の高い電流制御デバイスです。一方、MOSFET は低消費電力の電圧制御デバイスです。

-三極管のオン抵抗は大きいですが、MOS管のオン抵抗は小さく、わずか数百ミリオームです。現在の電気機器では、主に MOS の効率が三極管に比べて比較的高いため、MOS 管がスイッチとして一般的に使用されています。

・三極管は比較的コストが有利で、MOS管は比較的高価です。

-現在、ほとんどのシナリオで三極管の代わりに MOS 管が使用されています。一部の低電力または電力に敏感でないシナリオでのみ、価格の利点を考慮して三極管を使用します。

3.CMOS

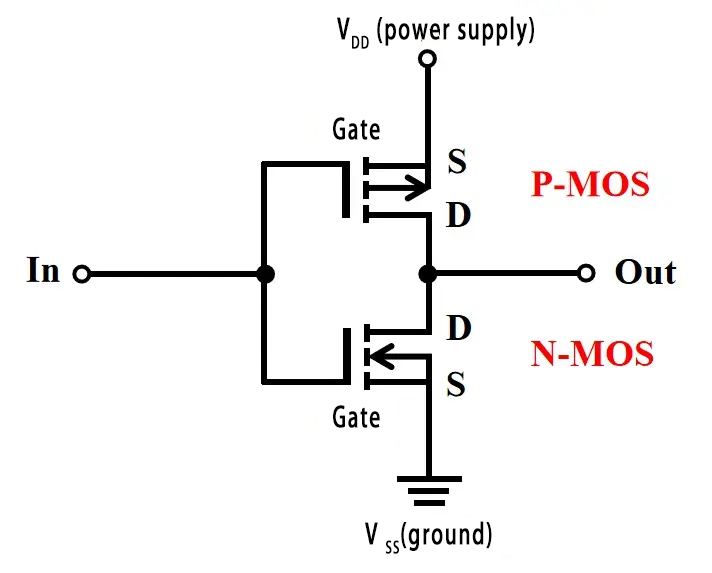

相補型金属酸化物半導体: CMOS テクノロジーでは、相補型の p 型および n 型の金属酸化物半導体トランジスタ (MOSFET) を使用して、電子デバイスおよび論理回路を構築します。次の図は、「1→0」または「0→1」変換に使用される一般的な CMOS インバータを示しています。

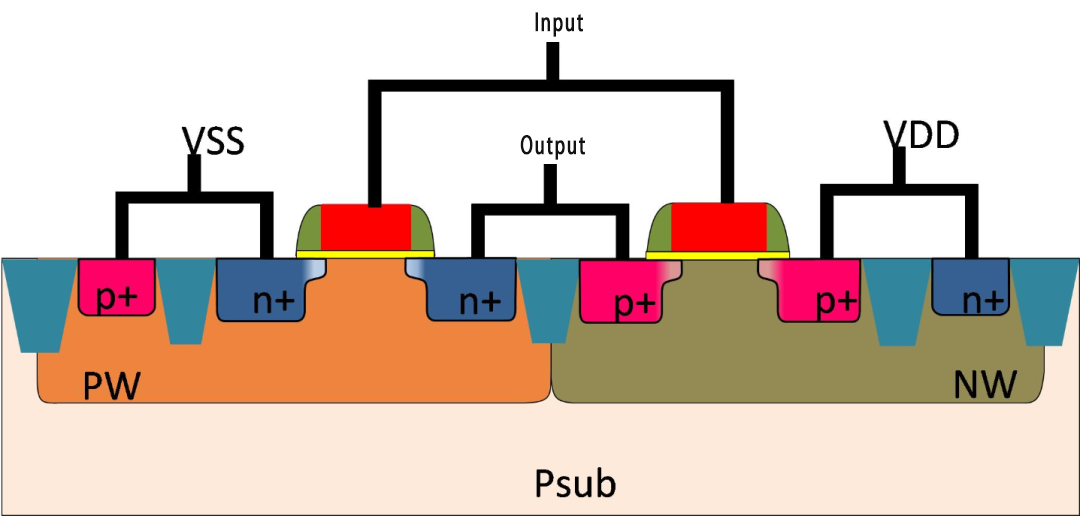

次の図は、一般的な CMOS の断面図です。左側がNMS、右側がPMOSです。 2 つの MOS の G 極は共通のゲート入力として一緒に接続され、D 極は共通のドレイン出力として一緒に接続されます。 VDD は PMOS のソースに接続され、VSS は NMOS のソースに接続されます。

1963 年、フェアチャイルド セミコンダクターのワンラスとサーが CMOS 回路を発明しました。 1968 年にアメリカン ラジオ コーポレーション (RCA) が最初の CMOS 集積回路製品を開発して以来、CMOS 回路は大きな発展を遂げてきました。その利点は、低消費電力と高集積化です (STI/LOCOS プロセスにより集積度がさらに向上します)。欠点は、ロック効果が存在することです (PN 接合の逆バイアスが MOS チューブ間の絶縁として使用され、干渉により強化されたループが容易に形成され、回路が焼損する可能性があります)。

4.DMOS

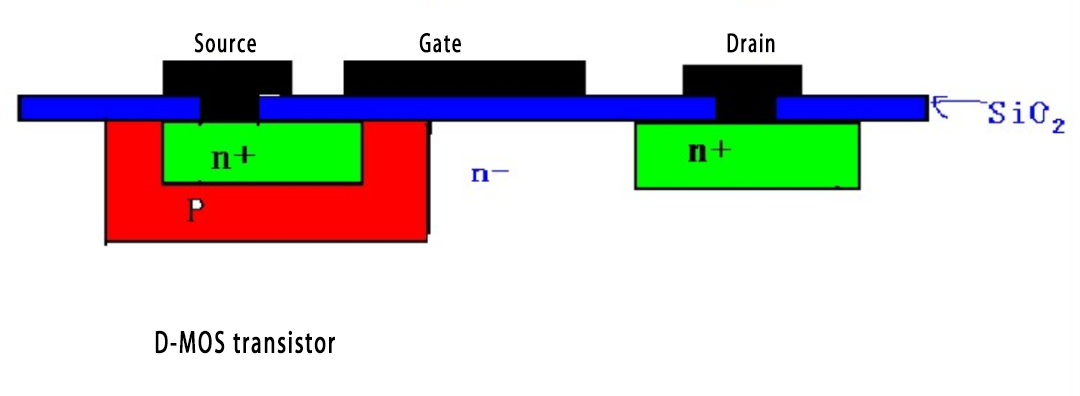

二重拡散金属酸化膜半導体: 通常の MOSFET デバイスの構造と同様に、ソース、ドレイン、ゲートなどの電極を備えていますが、ドレイン端の耐圧が高くなります。二重拡散プロセスを採用しています。

以下の図は、標準的な N チャネル DMOS の断面図を示しています。このタイプの DMOS デバイスは通常、MOSFET のソースがグランドに接続されるローサイド スイッチング アプリケーションで使用されます。さらに、P チャネル DMOS もあります。このタイプの DMOS デバイスは通常、MOSFET のソースが正電圧に接続されるハイサイド スイッチング アプリケーションで使用されます。 CMOS と同様に、相補型 DMOS デバイスは、同じチップ上で N チャネルおよび P チャネル MOSFET を使用して、相補的なスイッチング機能を提供します。

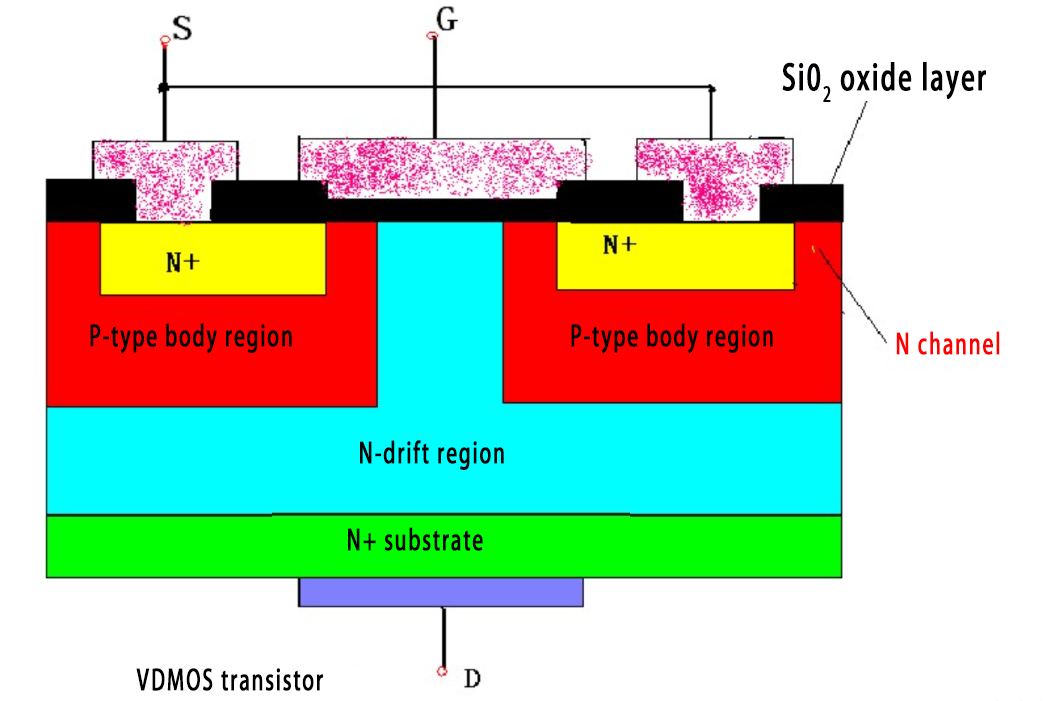

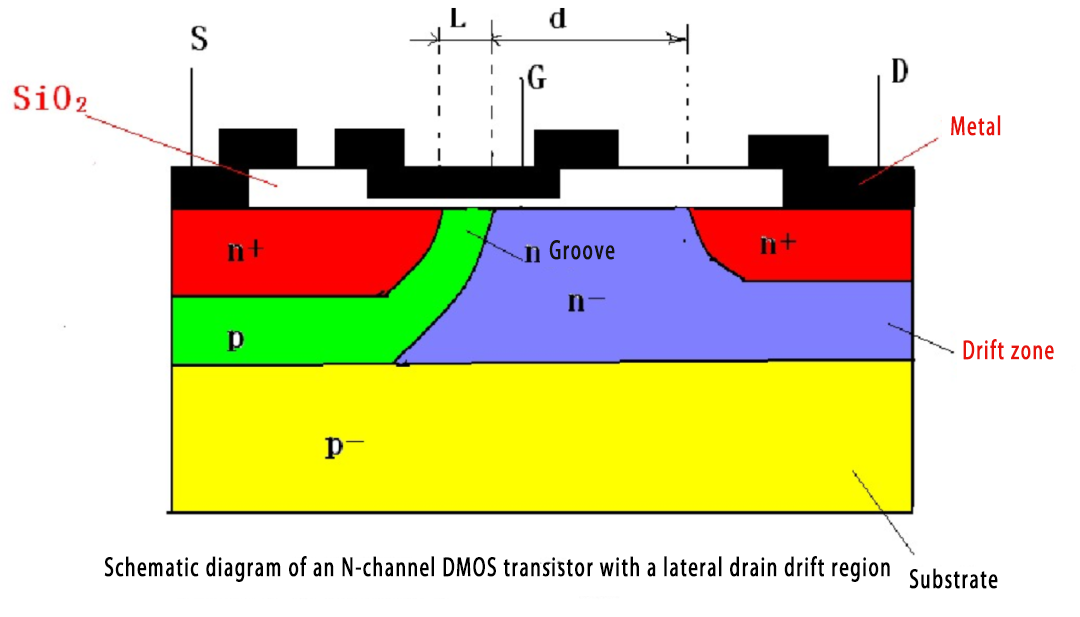

DMOSはチャネルの方向に応じて、縦型二重拡散金属酸化物半導体電界効果トランジスタVDMOS(Vertical Double-Diffused MOSFET)と横型二重拡散金属酸化物半導体電界効果トランジスタLDMOS(Lateral Double)の2種類に分けられます。 -拡散MOSFET)。

VDMOS デバイスは垂直チャネルを使用して設計されています。横型 DMOS デバイスと比較すると、耐圧と電流処理能力が高くなりますが、オン抵抗は依然として比較的大きいです。

LDMOS デバイスは横方向チャネルを使用して設計されており、非対称パワー MOSFET デバイスです。縦型 DMOS デバイスと比較して、オン抵抗が低く、スイッチング速度が高速になります。

従来の MOSFET と比較して、DMOS はオン容量が高く、抵抗が低いため、電源スイッチ、電動工具、電気自動車のドライブなどの高出力電子デバイスに広く使用されています。

5. BiCMOS

バイポーラ CMOS は、CMOS とバイポーラ デバイスを同じチップ上に同時に統合するテクノロジーです。その基本的な考え方は、CMOS デバイスを本体回路として使用し、大きな容量性負荷を駆動する必要があるバイポーラ デバイスや回路を追加することです。したがって、BiCMOS回路は、CMOS回路の高集積化および低消費電力という利点と、BJT回路の高速かつ強力な電流駆動能力という利点を併せ持っています。

STMicroelectronicsのBiCMOS SiGe(シリコン・ゲルマニウム)テクノロジーは、RF、アナログ、デジタル部品を単一チップ上に統合しており、外付け部品の数を大幅に削減し、消費電力を最適化できます。

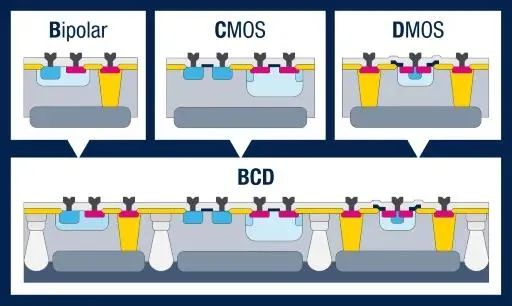

6.BCD

バイポーラ-CMOS-DMOS、このテクノロジは、BCD プロセスと呼ばれる、同じチップ上にバイポーラ、CMOS、および DMOS デバイスを作成できます。このテクノロジは、1986 年に STMicroelectronics (ST) によって初めて開発に成功しました。

バイポーラはアナログ回路に適しており、CMOSはデジタルおよびロジック回路に適しており、DMOSはパワーおよび高電圧デバイスに適しています。 BCD は 3 つの利点を組み合わせたものです。継続的な改良を経て、BCD は電源管理、アナログ データ収集、パワー アクチュエーターの分野の製品に広く使用されています。 STの公式Webサイトによると、BCDの成熟プロセスはまだ100nm程度で、90nmはまだプロトタイプ設計段階にあり、40nmBCDテクノロジは開発中の次世代製品に属します。

投稿日時: 2024 年 9 月 10 日