Byenveni nan sit entènèt nou an pou enfòmasyon pwodwi ak konsiltasyon.

Sit entènèt nou an:https://www.vet-china.com/

Kòm pwosesis fabrikasyon semi-conducteurs kontinye fè avans, yon deklarasyon pi popilè ki rele "Lwa Moore" te sikile nan endistri an. Li te pwopoze pa Gordon Moore, youn nan fondatè yo nan Intel, an 1965. Kontni debaz li yo se: kantite tranzistò ki ka akomode sou yon sikwi entegre ap double apeprè chak 18 a 24 mwa. Lwa sa a se pa sèlman yon analiz ak prediksyon nan tandans devlopman endistri a, men tou, yon fòs kondwi pou devlopman nan pwosesis fabrikasyon semi-conducteurs - tout bagay se fè tranzistò ak pi piti gwosè ak pèfòmans ki estab. Soti nan ane 1950 yo jiska prezan, apeprè 70 ane, yon total de BJT, MOSFET, CMOS, DMOS, ak ibrid BiCMOS ak teknoloji pwosesis BCD yo te devlope.

1. BJT

Bipolè junction tranzistò (BJT), souvan ke yo rekonèt kòm triode. Koule chaj nan tranzistò a se sitou akòz difizyon ak mouvman drift transpòtè nan junction PN. Depi li enplike koule nan tou de elektwon ak twou, yo rele li yon aparèy bipolè.

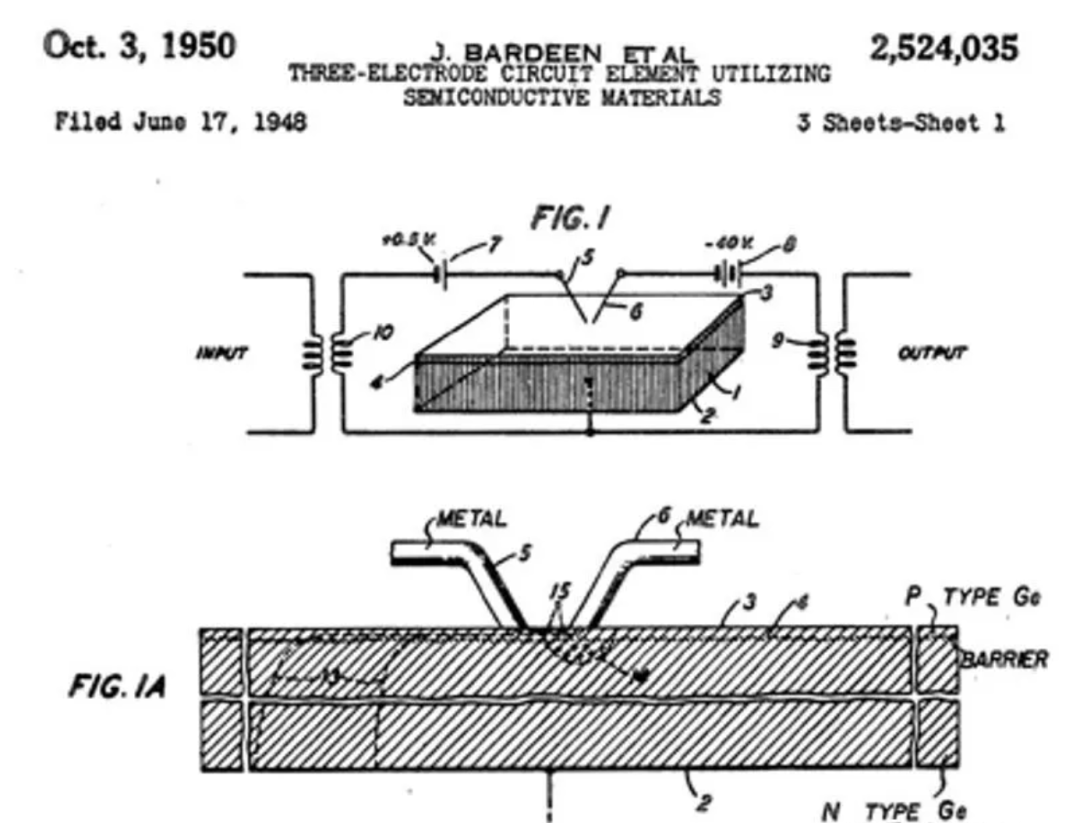

Gade tounen nan istwa a nan nesans li. Akòz lide pou ranplase triyod vakyòm ak anplifikatè solid, Shockley te pwopoze pou fè rechèch debaz sou semi-conducteurs nan sezon lete an 1945. Nan dezyèm mwatye nan 1945, Bell Labs te etabli yon gwoup rechèch fizik eta solid te dirije pa Shockley. Nan gwoup sa a, pa gen sèlman fizisyen, men tou, enjenyè sikwi ak famasi, ki gen ladan Bardeen, yon fizisyen teyorik, ak Brattain, yon fizisyen eksperimantal. Nan mwa desanm 1947, yon evènman ki te konsidere kòm yon etap enpòtan pa jenerasyon pita yo te rive briyan - Bardeen ak Brattain avèk siksè envante premye tranzistò pwen-kontak germanium nan mond lan ak anplifikasyon aktyèl.

Premye tranzistò pwen-kontak Bardeen ak Brattain

Yon ti tan apre sa, Shockley te envante tranzistò junction bipolè a an 1948. Li te pwopoze ke tranzistò a ka konpoze de de junctions pn, youn patipri pou pi devan ak lòt patipri ranvèse a, epi li te jwenn yon patant nan mwa jen 1948. An 1949, li te pibliye teyori an detay. nan travay la nan tranzistò a junction. Plis pase de ane pita, syantis ak enjenyè nan Bell Labs devlope yon pwosesis pou reyalize pwodiksyon an mas tranzistò junction (etap enpòtan an 1951), louvri yon nouvo epòk nan teknoloji elektwonik. An rekonesans pou kontribisyon yo nan envansyon nan tranzistò, Shockley, Bardeen ak Brattain te genyen ansanm 1956 Pri Nobèl nan Fizik.

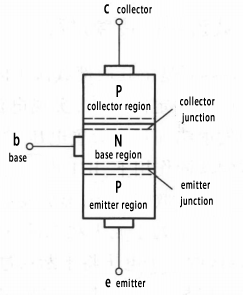

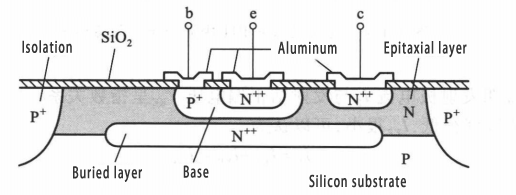

Senp dyagram estriktirèl tranzistò junction bipolè NPN

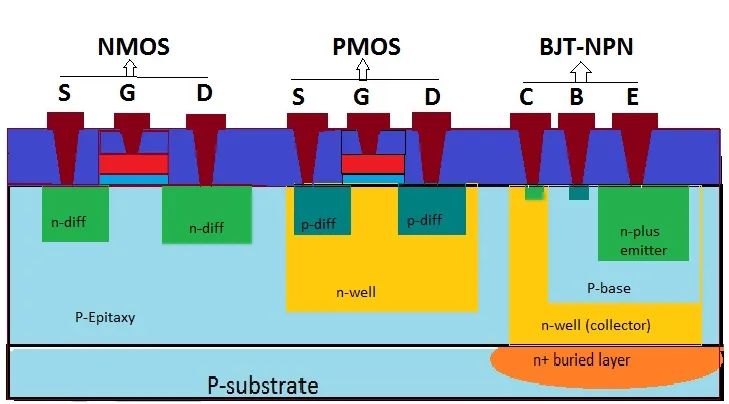

Konsènan estrikti tranzistò junction bipolè, BJT komen yo se NPN ak PNP. Estrikti detaye entèn yo montre nan figi ki anba a. Rejyon semi-conducteurs enpurte ki koresponn ak emeteur a se rejyon an emeteur, ki gen yon gwo konsantrasyon dopan; rejyon semiconductor enpurte ki koresponn ak baz la se rejyon baz la, ki gen yon lajè trè mens ak yon konsantrasyon dopan ki ba anpil; rejyon an enpurte semi-conducteurs ki koresponn ak pèseptè a se rejyon an pèseptè, ki gen yon zòn gwo ak yon konsantrasyon dopan ki ba anpil.

Avantaj ki genyen nan teknoloji BJT yo se gwo vitès repons, segondè transkonduktans (chanjman vòltaj antre koresponn ak gwo chanjman aktyèl pwodiksyon), bri ki ba, gwo presizyon analòg, ak gwo kapasite kondwi aktyèl; dezavantaj yo se entegrasyon ki ba (pwofondè vètikal pa ka redwi ak gwosè lateral) ak gwo konsomasyon pouvwa.

2. MOS

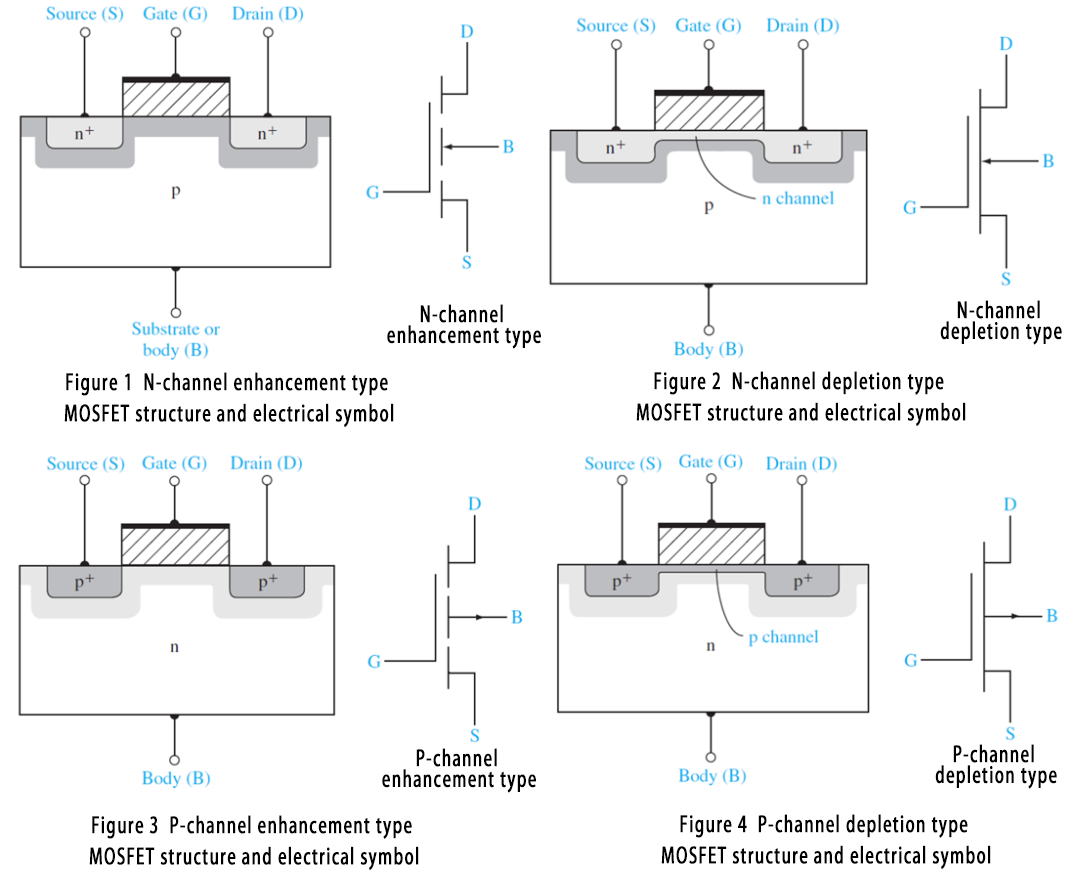

Metal oksid Semiconductor Field Effect Transistor (Metal Oxide Semiconductor FET), se sa ki, yon tranzistò efè jaden ki kontwole switch la nan semi-conducteurs (S) chanèl konduktif la lè li aplike vòltaj nan pòtay la nan kouch metal la (M-metal aliminyòm) ak la. sous nan kouch nan oksid (O-izolasyon kouch SiO2) jenere efè a nan jaden elektrik la. Depi pòtay la ak sous la, ak pòtay la ak drenaj la izole pa kouch nan posibilite SiO2, MOSFET yo rele tou yon tranzistò efè jaden pòtay izole. An 1962, Bell Labs te anonse ofisyèlman devlopman siksè, ki te vin youn nan etap enpòtan yo ki pi enpòtan nan istwa devlopman semi-conducteurs ak dirèkteman mete fondasyon teknik pou avènement memwa semi-conducteurs.

MOSFET ka divize an P chanèl ak N chanèl selon kalite kanal konduktif la. Dapre anplitid vòltaj pòtay la, li ka divize an: kalite rediksyon-lè vòltaj pòtay la se zewo, gen yon kanal konduktif ant drenaj la ak sous la; amelyorasyon kalite-pou N (P) aparèy chanèl, gen yon chanèl kondiktif sèlman lè vòltaj pòtay la pi gran pase (mwens pase) zewo, ak MOSFET pouvwa se sitou N chanèl amelyorasyon kalite.

Diferans prensipal yo ant MOS ak triode gen ladan men yo pa limite a pwen sa yo:

-Triod yo se aparèy bipolè paske tou de transpòtè majorite ak minorite patisipe nan kondiksyon an menm tan; pandan y ap MOS sèlman fè elektrisite atravè transpòtè majorite nan semi-conducteurs, epi yo rele tou yon tranzistò unipolè.

-Triod yo se aparèy aktyèl kontwole ak konsomasyon pouvwa relativman wo; pandan y ap MOSFET yo se aparèy vòltaj ki kontwole ak konsomasyon pouvwa ki ba.

-Triodes gen gwo sou-rezistans, pandan y ap MOS tib gen ti sou-rezistans, sèlman kèk santèn milliohms. Nan aparèy elektrik aktyèl yo, tib MOS yo jeneralman itilize kòm switch, sitou paske efikasite MOS relativman wo konpare ak triyod.

-Triod gen yon pri relativman avantaje, ak tib MOS yo relativman chè.

-Sèjousi, MOS tib yo te itilize pou ranplase triodes nan pifò scénarios. Se sèlman nan kèk senaryo ki ba-pouvwa oswa pouvwa-sensib, nou pral sèvi ak triyod konsidere avantaj nan pri.

3. CMOS

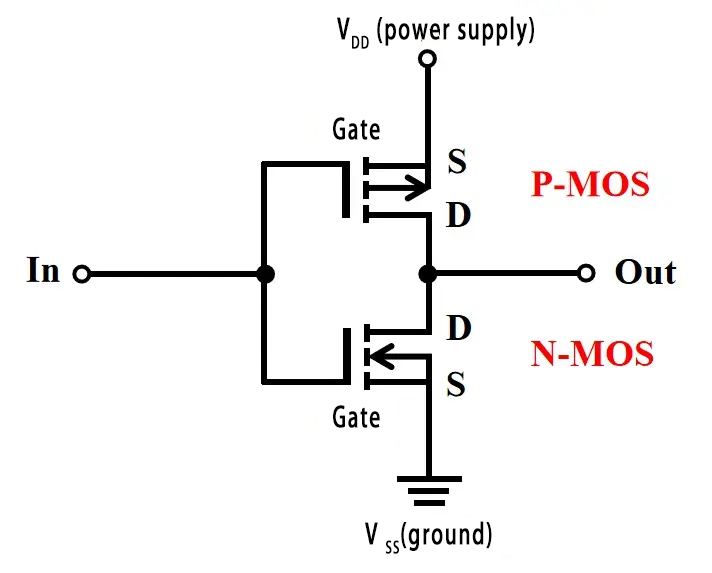

Semiconductor oksid metal konplemantè: teknoloji CMOS sèvi ak tranzistò semi-conducteurs konplemantè p-tip ak n-tip metal oksid (MOSFET) pou konstwi aparèy elektwonik ak sikwi lojik. Figi sa a montre yon varyateur CMOS komen, ki itilize pou konvèsyon "1→0" oswa "0→1".

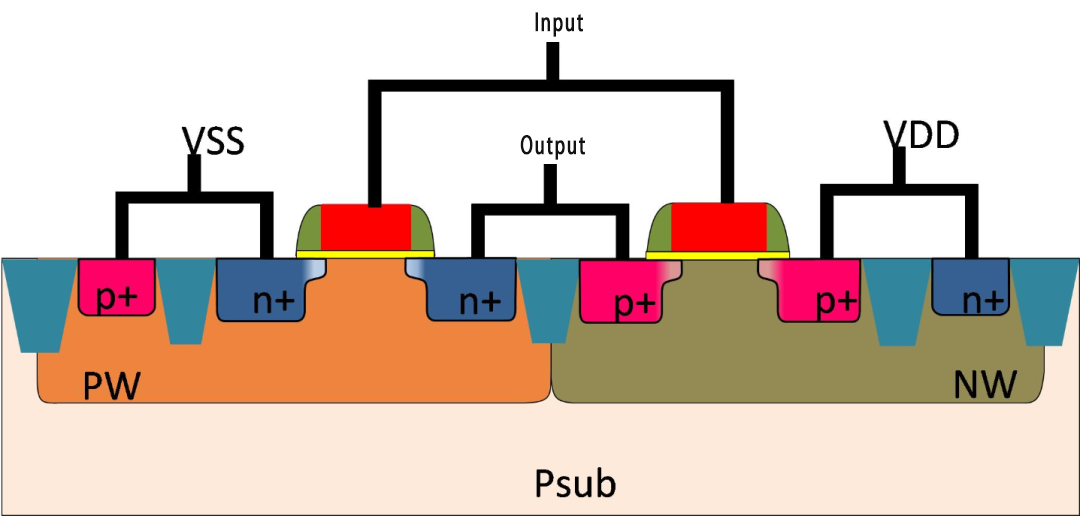

Figi sa a se yon koup transvèsal CMOS tipik. Bò gòch la se NMS, ak bò dwat la se PMOS. Pòl G nan de MOS yo konekte ansanm kòm yon opinyon pòtay komen, ak poto D yo konekte ansanm kòm yon pwodiksyon drenaj komen. VDD konekte ak sous PMOS, epi VSS konekte ak sous NMOS.

An 1963, Wanlass ak Sah nan Fairchild Semiconductor te envante kous CMOS la. An 1968, American Radio Corporation (RCA) te devlope premye pwodwi sikwi entegre CMOS, e depi lè sa a, sikwi CMOS te reyalize gwo devlopman. Avantaj li yo se konsomasyon pouvwa ki ba ak entegrasyon segondè (pwosesis STI / LOCOS ka plis amelyore entegrasyon); dezavantaj li se egzistans lan nan yon efè fèmen (PN junction patipri ranvèse yo itilize kòm izolasyon ant tib MOS, ak entèferans ka byen fasil fòme yon bouk amelyore epi boule kous la).

4. DMOS

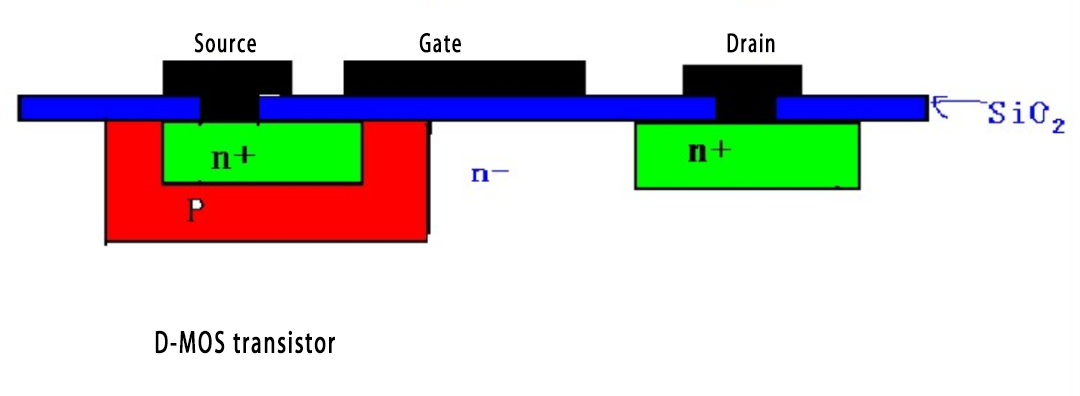

Double-diffuse metal oksid Semiconductor: Menm jan ak estrikti a nan aparèy MOSFET òdinè, li tou gen sous, drenaj, pòtay ak lòt elektwòd, men vòltaj la pann nan fen drenaj la wo. Yo itilize pwosesis difizyon doub.

Figi ki anba a montre koup transvèsal yon DMOS N-chanèl estanda. Sa a se kalite aparèy DMOS anjeneral yo itilize nan aplikasyon pou chanje bò ki ba, kote sous MOSFET la konekte ak tè a. Anplis de sa, gen yon DMOS P-chanèl. Sa a se kalite aparèy DMOS anjeneral yo itilize nan aplikasyon pou chanje segondè-bò, kote sous MOSFET la konekte ak yon vòltaj pozitif. Menm jan ak CMOS, aparèy DMOS konplemantè yo itilize MOSFET N-chanèl ak P-chanèl sou menm chip la pou bay fonksyon switch konplemantè.

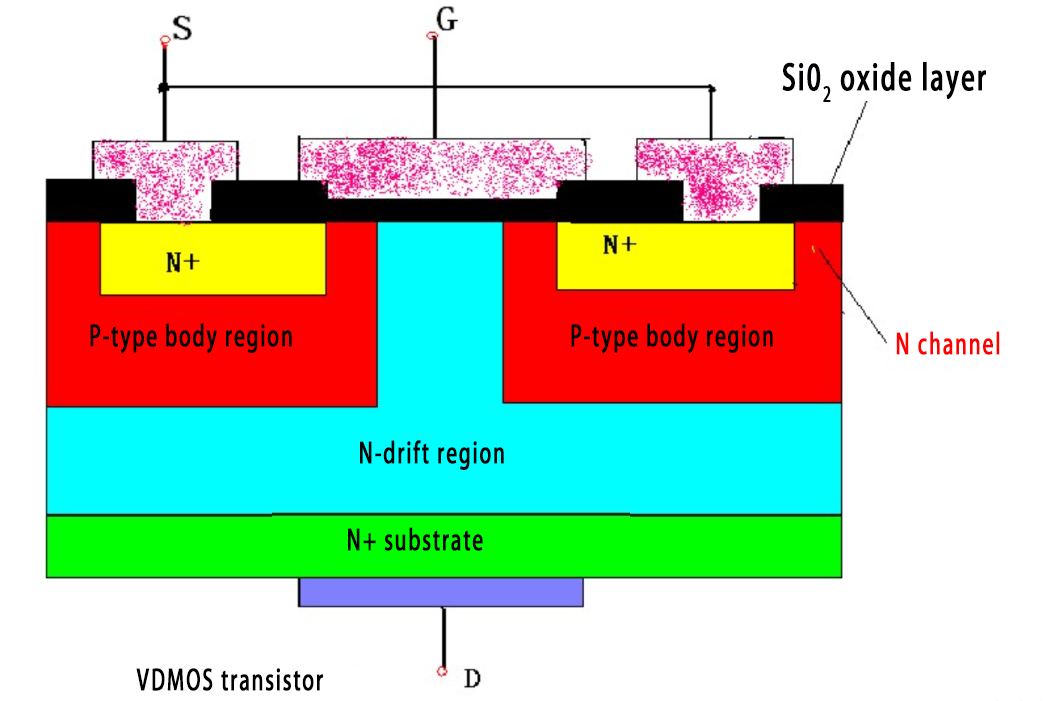

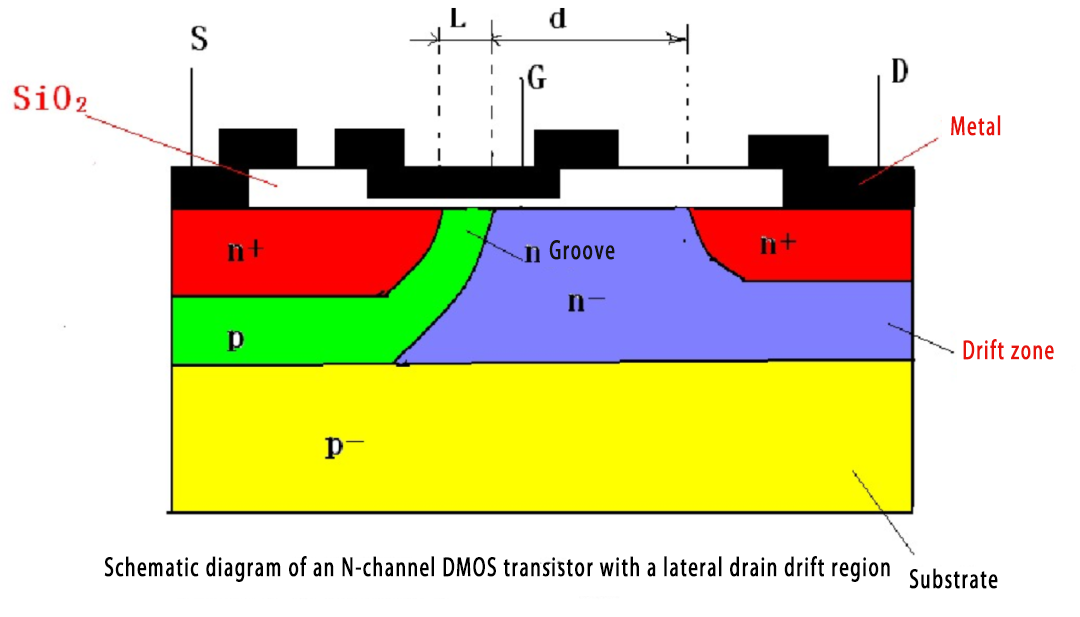

Tou depan de direksyon kanal la, DMOS ka divize an de kalite, sètadi vètikal doub-difize metal oksid semi-conducteurs efè jaden tranzistò VDMOS (vètikal Double-Diffused MOSFET) ak lateral doub-difize metal oksid semi-conducteurs efè jaden tranzistò LDMOS (Lateral Double. -Difize MOSFET).

Aparèy VDMOS yo fèt ak yon kanal vètikal. Konpare ak aparèy DMOS lateral yo, yo gen pi wo vòltaj pann ak kapasite manyen aktyèl, men rezistans nan toujou relativman gwo.

Aparèy LDMOS yo fèt ak yon kanal lateral epi yo se aparèy MOSFET pouvwa asimetri. Konpare ak aparèy DMOS vètikal yo, yo pèmèt pi ba sou-rezistans ak pi vit vitès switch.

Konpare ak MOSFET tradisyonèl yo, DMOS gen pi wo kapasite ak pi ba rezistans, kidonk li se lajman ki itilize nan aparèy elektwonik gwo pouvwa tankou switch pouvwa, zouti pouvwa ak kondwi machin elektrik.

5. BiCMOS

Bipolè CMOS se yon teknoloji ki entegre CMOS ak aparèy bipolè sou menm chip an menm tan an. Lide debaz li se sèvi ak aparèy CMOS kòm sikwi inite prensipal la, epi ajoute aparèy bipolè oswa sikui kote gwo chaj kapasitif yo oblije kondwi. Se poutèt sa, sikui BiCMOS gen avantaj ki genyen nan gwo entegrasyon ak konsomasyon pouvwa ki ba nan sikui CMOS, ak avantaj ki genyen nan gwo vitès ak gwo kapasite aktyèl kondwi nan sikui BJT.

Teknoloji BiCMOS SiGe (Silisyòm germanium) STMicroelectronics entegre RF, pati analòg ak dijital sou yon sèl chip, ki ka siyifikativman redwi kantite konpozan ekstèn ak optimize konsomasyon pouvwa.

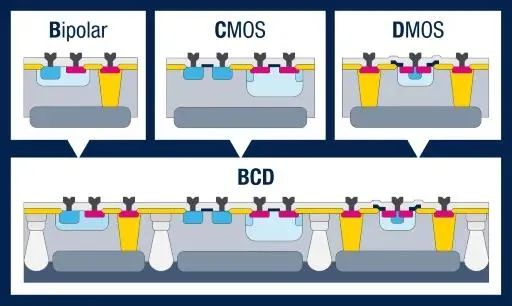

6. BCD

Bipolè-CMOS-DMOS, teknoloji sa a ka fè aparèy bipolè, CMOS ak DMOS sou menm chip, yo rele pwosesis BCD, ki te premye devlope avèk siksè pa STMicroelectronics (ST) an 1986.

Bipolè se apwopriye pou sikui analòg, CMOS se apwopriye pou sikui dijital ak lojik, ak DMOS se apwopriye pou pouvwa ak aparèy wo-vòltaj. BCD konbine avantaj twa yo. Apre amelyorasyon kontinyèl, BCD se lajman ki itilize nan pwodwi nan domèn jesyon pouvwa, akizisyon done analòg ak actuators pouvwa. Dapre sit entènèt ofisyèl ST a, pwosesis la matirite pou BCD se toujou alantou 100nm, 90nm se toujou nan konsepsyon pwototip, ak teknoloji 40nmBCD ki dwe nan pwodwi pwochen jenerasyon li yo ki anba devlopman.

Tan pòs: Sep-10-2024