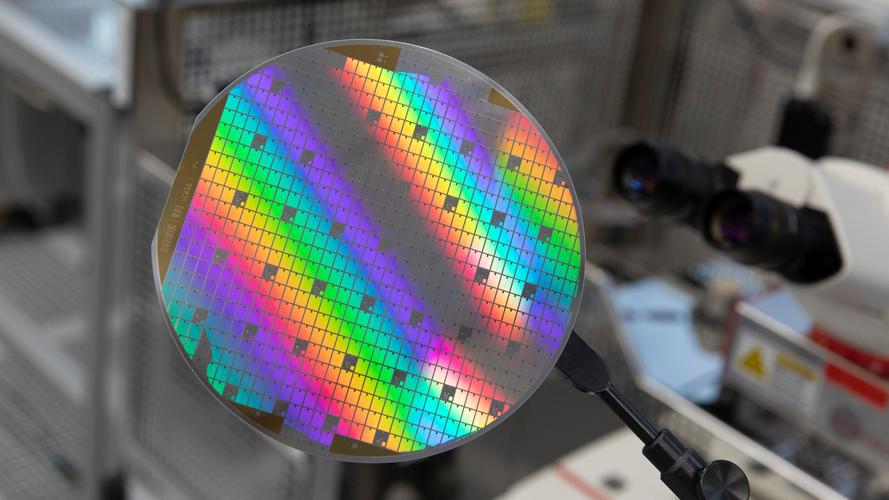

VET Energy cov khoom lag luam tsis txwv rau silicon wafers. Peb kuj muab ntau yam khoom siv semiconductor substrate, suav nrog SiC Substrate, SOI Wafer, SiN Substrate, Epi Wafer, thiab lwm yam, nrog rau cov ntaub ntawv tshiab dav dav semiconductor xws li Gallium Oxide Ga2O3 thiab AlN Wafer. Cov khoom no tuaj yeem ua tau raws li daim ntawv thov kev xav tau ntawm cov neeg siv khoom sib txawv hauv lub zog hluav taws xob, xov tooj cua zaus, sensors thiab lwm yam.

Daim ntawv thov teb:

•Integrated Circuits:Raws li cov khoom siv yooj yim rau kev tsim hluav taws xob sib txuas, P-hom silicon wafers tau siv dav hauv ntau lub logic circuits, nco, thiab lwm yam.

•Cov khoom siv fais fab:P-hom silicon wafers tuaj yeem siv los ua cov khoom siv hluav taws xob xws li fais fab transistors thiab diodes.

•Sensors:P-hom silicon wafers tuaj yeem siv los ua ntau hom sensors, xws li lub siab sensors, kub sensors, thiab lwm yam.

•Solar Cell:P-hom silicon wafers yog ib qho tseem ceeb ntawm lub hnub ci hlwb.

VET Energy muab cov neeg siv khoom nrog cov kev daws teeb meem wafer, thiab tuaj yeem hloov kho wafers nrog sib txawv resistivity, sib txawv oxygen cov ntsiab lus, txawv thickness thiab lwm yam specifications raws li cov kev xav tau ntawm cov neeg muas zaub. Tsis tas li ntawd, peb kuj muab kev pabcuam kev tshaj lij thiab kev pabcuam tomqab muag los pab cov neeg siv khoom daws teebmeem ntau yam uas tau ntsib hauv cov txheej txheem tsim khoom.

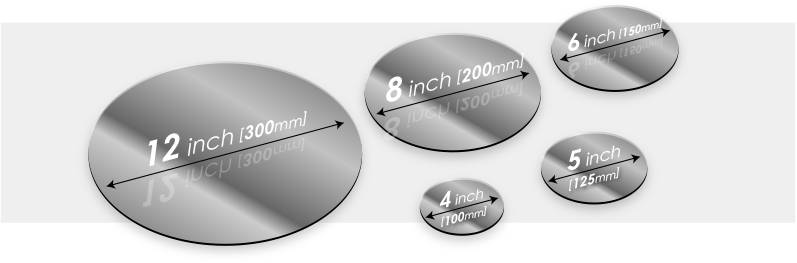

WAFFERING SPECIFICATIONS

*n-Pm=n-type Pm-Grade,n-Ps=n-type Ps-Qib,Sl=Semi-lnsulating

| Yam khoom | 8-Inch | 6-Inch | 4-Inch | ||

| np | n- Pm | n-Ps | SI | SI | |

| TVV (GBIR) | ≤ 6 hli | ≤ 6 hli | |||

| Hneev (GF3YFCD) - Tus Nqi Tsis Muaj | ≤15μm | ≤15μm | ≤ 25μm | ≤15μm | |

| Warp (GF3YFER) | ≤ 25μm | ≤ 25μm | ≤ 40μm | ≤ 25μm | |

| LTV (SBIR)-10mmx10mm | < 2 m os | ||||

| Wafer Ntug | Beveling | ||||

NTAU NTAU

*n-Pm=n-type Pm-Grade,n-Ps=n-type Ps-Qib,Sl=Semi-lnsulating

| Yam khoom | 8-Inch | 6-Inch | 4-Inch | ||

| np | n- Pm | n-Ps | SI | SI | |

| Nto tiav | Ob chav sab Optical Polish, Si- ntsej muag CMP | ||||

| SurfaceRoughness | (10um x 10um) Si-FaceRa≤0.2nm | (5umx5um) Si-Face Ra≤0.2nm | |||

| Ntug Chips | Tsis Muaj Kev Tso Cai (ntev thiab dav ≥0.5mm) | ||||

| Indents | Tsis Muaj Tso Cai | ||||

| Scratches (Si-Face) | Qty.≤ 5, Ua kom tiav | Qty.≤ 5, Ua kom tiav | Qty.≤ 5, Ua kom tiav | ||

| Kev tawg | Tsis Muaj Tso Cai | ||||

| Ntug Exclusion | 3mm ib | ||||