Welkom by ons webwerf vir produkinligting en konsultasie.

Ons webwerf:https://www.vet-china.com/

Namate halfgeleiervervaardigingsprosesse voortgaan om deurbrake te maak, het 'n bekende verklaring genaamd "Moore's Law" in die bedryf die rondte gedoen. Dit is voorgestel deur Gordon Moore, een van die stigters van Intel, in 1965. Die kerninhoud daarvan is: die aantal transistors wat op 'n geïntegreerde stroombaan geakkommodeer kan word, sal ongeveer elke 18 tot 24 maande verdubbel. Hierdie wet is nie net 'n ontleding en voorspelling van die ontwikkelingstendens van die bedryf nie, maar ook 'n dryfveer vir die ontwikkeling van halfgeleiervervaardigingsprosesse - alles is om transistors met kleiner grootte en stabiele werkverrigting te maak. Vanaf die 1950's tot die hede, ongeveer 70 jaar, is 'n totaal van BJT-, MOSFET-, CMOS-, DMOS- en hibriede BiCMOS- en BCD-prosestegnologieë ontwikkel.

1. BJT

Bipolêre aansluitingstransistor (BJT), algemeen bekend as triode. Die ladingvloei in die transistor is hoofsaaklik as gevolg van die diffusie en dryfbeweging van draers by die PN-aansluiting. Aangesien dit die vloei van beide elektrone en gate behels, word dit 'n bipolêre toestel genoem.

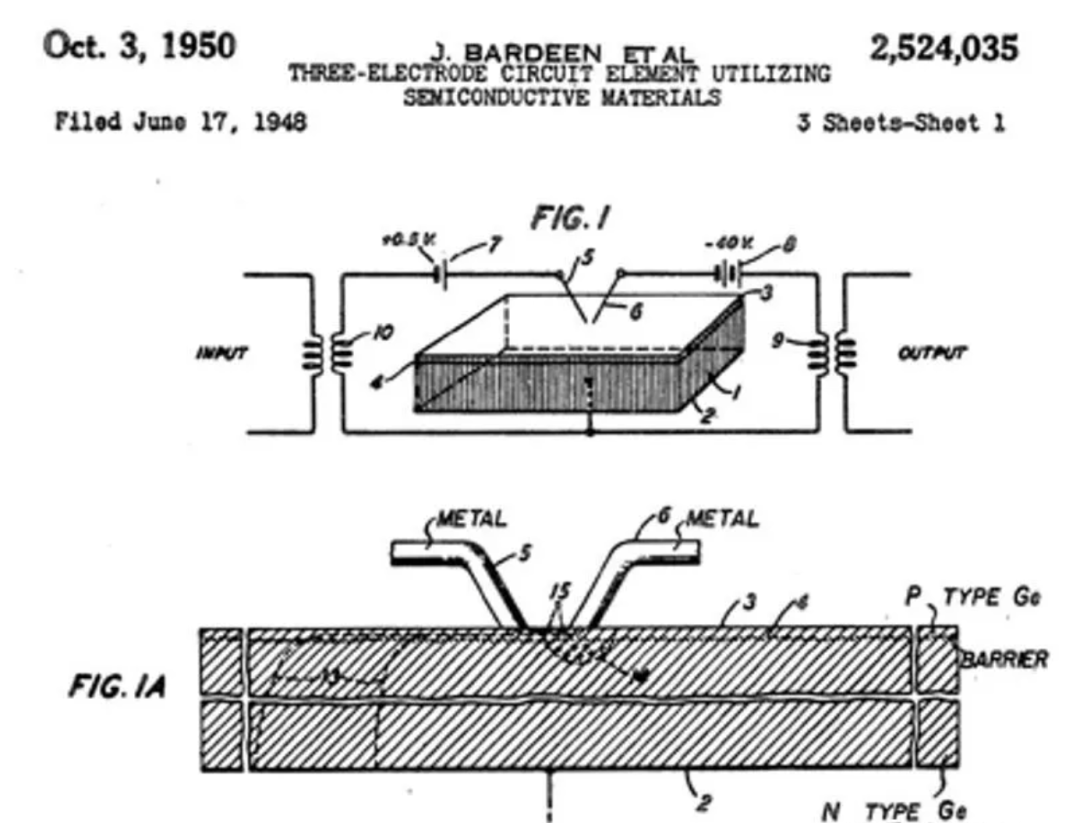

Terugblik op die geskiedenis van sy geboorte. As gevolg van die idee om vakuumtriodes met soliede versterkers te vervang, het Shockley voorgestel om basiese navorsing oor halfgeleiers uit te voer in die somer van 1945. In die tweede helfte van 1945 het Bell Labs 'n vastestof-fisika-navorsingsgroep onder leiding van Shockley gestig. In hierdie groep is daar nie net fisici nie, maar ook kringingenieurs en chemici, insluitend Bardeen, 'n teoretiese fisikus, en Brattain, 'n eksperimentele fisikus. In Desember 1947 het 'n gebeurtenis wat deur latere generasies as 'n mylpaal beskou is, briljant plaasgevind - Bardeen en Brattain het die wêreld se eerste germaniumpuntkontaktransistor met stroomversterking suksesvol uitgevind.

Bardeen en Brattain se eerste punt-kontak transistor

Kort daarna het Shockley die bipolêre aansluitingstransistor uitgevind in 1948. Hy het voorgestel dat die transistor uit twee pn-aansluitings saamgestel kan word, een vorentoe bevooroordeeld en die ander omgekeerde bevooroordeeld, en het 'n patent verkry in Junie 1948. In 1949 het hy die gedetailleerde teorie gepubliseer van die werking van die aansluitingstransistor. Meer as twee jaar later het wetenskaplikes en ingenieurs by Bell Labs 'n proses ontwikkel om massaproduksie van aansluitingstransistors te bereik (mylpaal in 1951), wat 'n nuwe era van elektroniese tegnologie begin. Ter erkenning van hul bydraes tot die uitvinding van transistors, het Shockley, Bardeen en Brattain gesamentlik die 1956 Nobelprys in Fisika gewen.

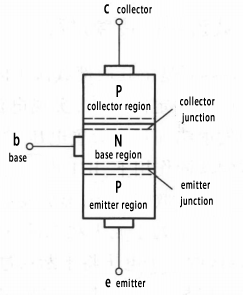

Eenvoudige struktuurdiagram van NPN bipolêre aansluitingstransistor

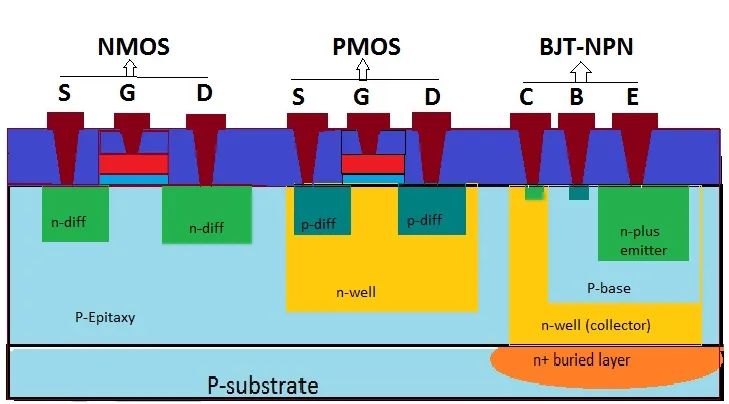

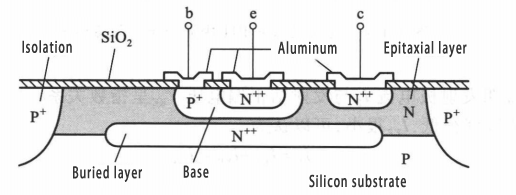

Wat die struktuur van bipolêre aansluitingstransistors betref, is algemene BJT's NPN en PNP. Die gedetailleerde interne struktuur word in die figuur hieronder getoon. Die onreinheid-halfgeleiergebied wat met die emittor ooreenstem, is die emittorstreek, wat 'n hoë dopingkonsentrasie het; die onreinheid halfgeleiergebied wat met die basis ooreenstem, is die basisgebied, wat 'n baie dun breedte en 'n baie lae dopingkonsentrasie het; die onsuiwerheidshalfgeleiergebied wat met die versamelaar ooreenstem, is die versamelaargebied, wat 'n groot oppervlakte en 'n baie lae dopingkonsentrasie het.

Die voordele van BJT-tegnologie is hoë reaksiespoed, hoë transgeleiding (insetspanningveranderinge stem ooreen met groot uitsetstroomveranderings), lae geraas, hoë analoogakkuraatheid en sterk stroomaandryfvermoë; die nadele is lae integrasie (vertikale diepte kan nie met laterale grootte verminder word nie) en hoë kragverbruik.

2. MOS

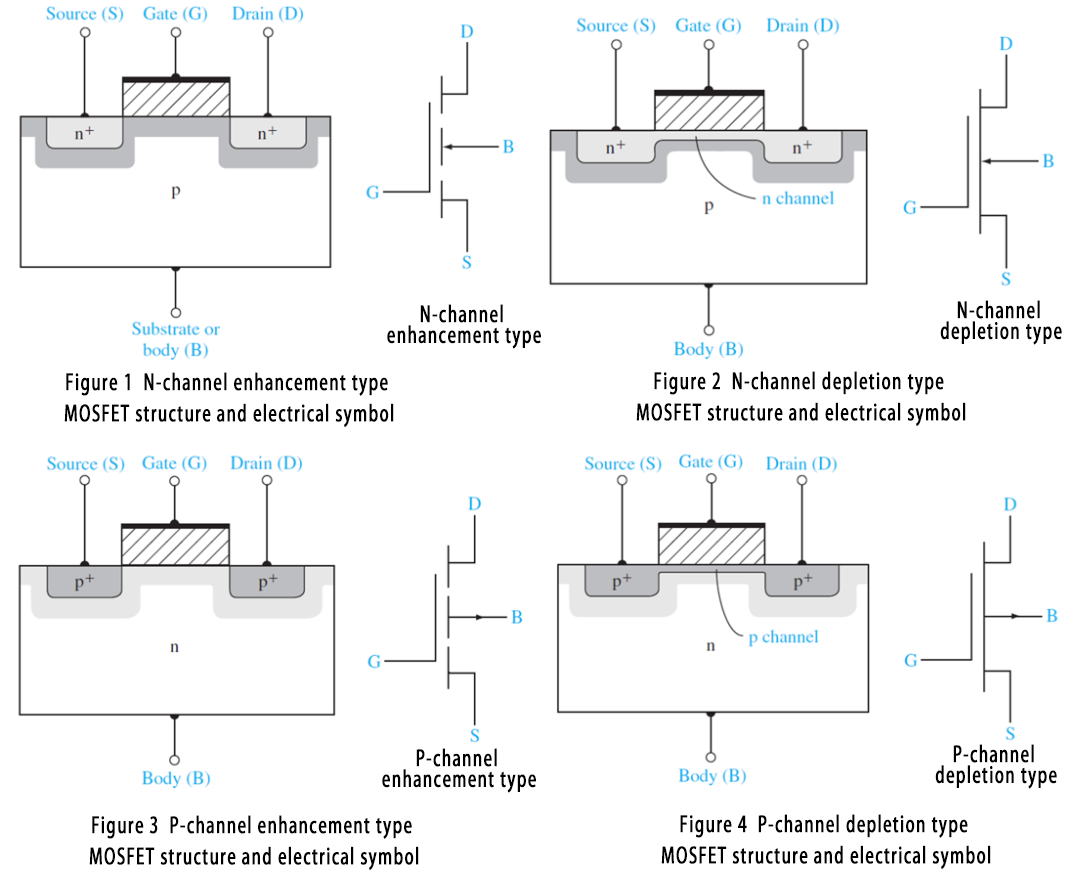

Metaaloksied-halfgeleier-veldeffektransistor (metaaloksied-halfgeleier-FET), dit wil sê 'n veldeffektransistor wat die skakelaar van die halfgeleier (S) geleidende kanaal beheer deur spanning aan die hek van die metaallaag (M-metaal aluminium) en die bron deur die oksiedlaag (O-isolerende laag SiO2) om die effek van die elektriese veld te genereer. Aangesien die hek en die bron, en die hek en die drein deur die SiO2-isolerende laag geïsoleer word, word MOSFET ook 'n geïsoleerde hek-veldeffektransistor genoem. In 1962 het Bell Labs die suksesvolle ontwikkeling amptelik aangekondig, wat een van die belangrikste mylpale in die geskiedenis van halfgeleierontwikkeling geword het en direk die tegniese grondslag gelê het vir die koms van halfgeleiergeheue.

MOSFET kan volgens die tipe geleidende kanaal in P-kanaal en N-kanaal verdeel word. Volgens die hekspanningsamplitude kan dit verdeel word in: uitputtingstipe - wanneer die hekspanning nul is, is daar 'n geleidende kanaal tussen die drein en die bron; verbetering tipe - vir N (P) kanaal toestelle, daar is 'n geleidende kanaal slegs wanneer die hek spanning groter as (minder as) nul is, en krag MOSFET is hoofsaaklik N kanaal verbetering tipe.

Die belangrikste verskille tussen MOS en triode sluit in, maar is nie beperk tot, die volgende punte:

-Triodes is bipolêre toestelle omdat beide meerderheids- en minderheidsdraers terselfdertyd aan geleiding deelneem; terwyl MOS slegs elektrisiteit deur meerderheid draers in halfgeleiers gelei, en ook 'n unipolêre transistor genoem word.

-Triodes is stroombeheerde toestelle met relatief hoë kragverbruik; terwyl MOSFET's spanningsbeheerde toestelle met lae kragverbruik is.

-Triodes het groot aan-weerstand, terwyl MOS-buise klein aan-weerstand het, slegs 'n paar honderd milliohm. In huidige elektriese toestelle word MOS-buise oor die algemeen as skakelaars gebruik, hoofsaaklik omdat die doeltreffendheid van MOS relatief hoog is in vergelyking met triodes.

-Triodes het 'n relatief voordelige koste, en MOS-buise is relatief duur.

-Deesdae word MOS-buise gebruik om triodes in die meeste scenario's te vervang. Slegs in sommige lae-krag of krag-onsensitiewe scenario's, sal ons triodes gebruik met inagneming van die prysvoordeel.

3. CMOS

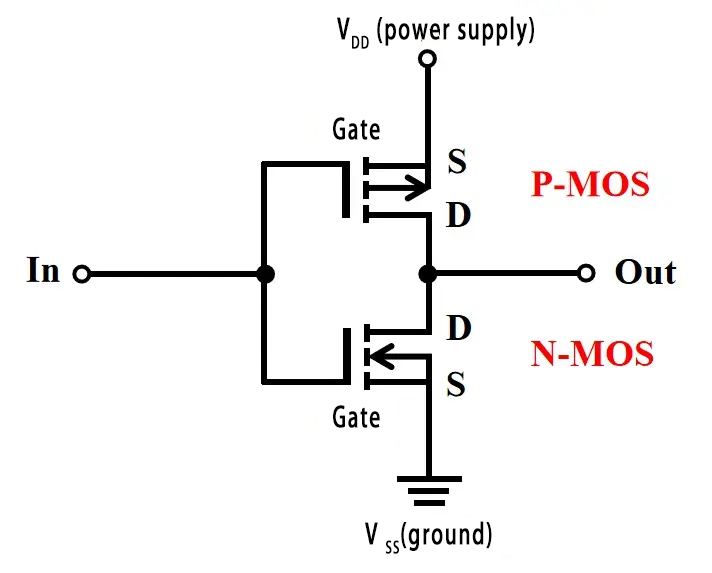

Komplementêre metaaloksiedhalfgeleier: CMOS-tegnologie gebruik komplementêre p-tipe en n-tipe metaaloksied-halfgeleiertransistors (MOSFET's) om elektroniese toestelle en logiese stroombane te bou. Die volgende figuur toon 'n algemene CMOS-omskakelaar, wat gebruik word vir "1→0" of "0→1" omskakeling.

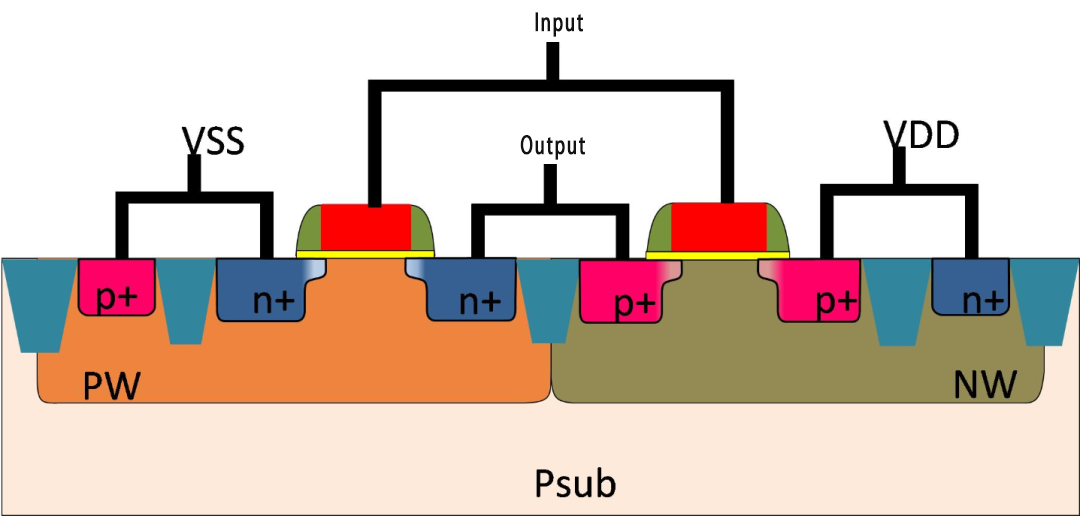

Die volgende figuur is 'n tipiese CMOS-deursnit. Die linkerkant is NMS, en die regterkant is PMOS. Die G-pole van die twee MOS is aan mekaar verbind as 'n gemeenskaplike hek-invoer, en die D-pole is saam verbind as 'n gemeenskaplike drein-uitset. VDD is gekoppel aan die bron van PMOS, en VSS is gekoppel aan die bron van NMOS.

In 1963 het Wanlass en Sah van Fairchild Semiconductor die CMOS-kring uitgevind. In 1968 het die American Radio Corporation (RCA) die eerste CMOS-geïntegreerde stroombaanproduk ontwikkel, en sedertdien het die CMOS-kring groot ontwikkeling bereik. Die voordele daarvan is lae kragverbruik en hoë integrasie (STI/LOCOS-proses kan integrasie verder verbeter); die nadeel daarvan is die bestaan van 'n slot-effek (PN-aansluiting omgekeerde voorspanning word as isolasie tussen MOS-buise gebruik, en interferensie kan maklik 'n verbeterde lus vorm en die stroombaan verbrand).

4. DMOS

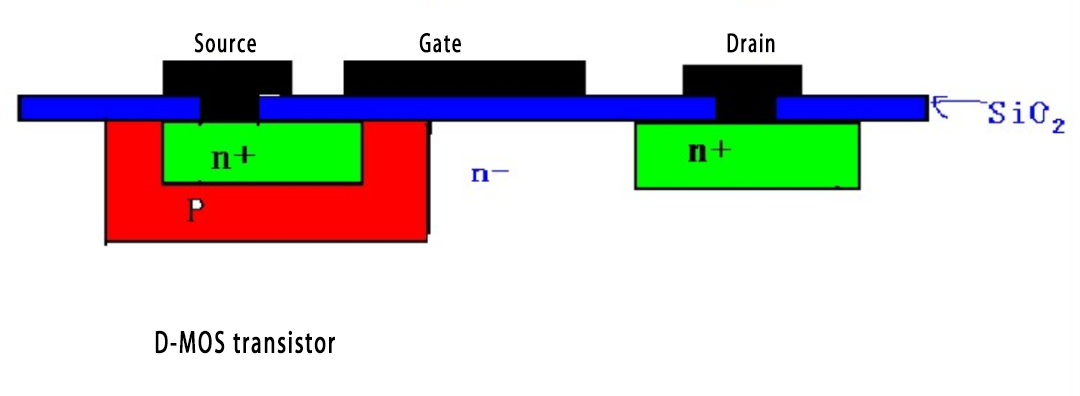

Dubbeldiffusie metaaloksiedhalfgeleier: Soortgelyk aan die struktuur van gewone MOSFET-toestelle, het dit ook bron-, drein-, hek- en ander elektrodes, maar die afbreekspanning van die dreineerkant is hoog. Dubbel diffusie proses word gebruik.

Die figuur hieronder toon die deursnee van 'n standaard N-kanaal DMOS. Hierdie tipe DMOS-toestel word gewoonlik gebruik in laekant-skakeltoepassings, waar die bron van die MOSFET aan die grond gekoppel is. Daarbenewens is daar 'n P-kanaal DMOS. Hierdie tipe DMOS-toestel word gewoonlik in hoëkantskakeltoepassings gebruik, waar die bron van die MOSFET aan 'n positiewe spanning gekoppel is. Soortgelyk aan CMOS, gebruik komplementêre DMOS-toestelle N-kanaal en P-kanaal MOSFET's op dieselfde skyfie om komplementêre skakelfunksies te verskaf.

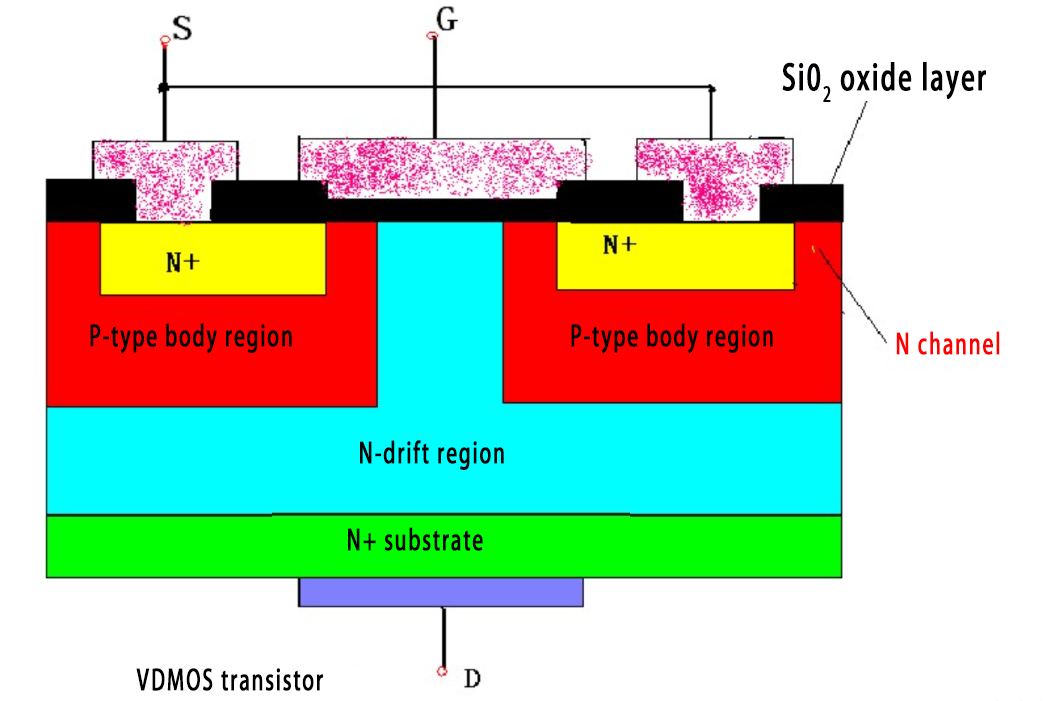

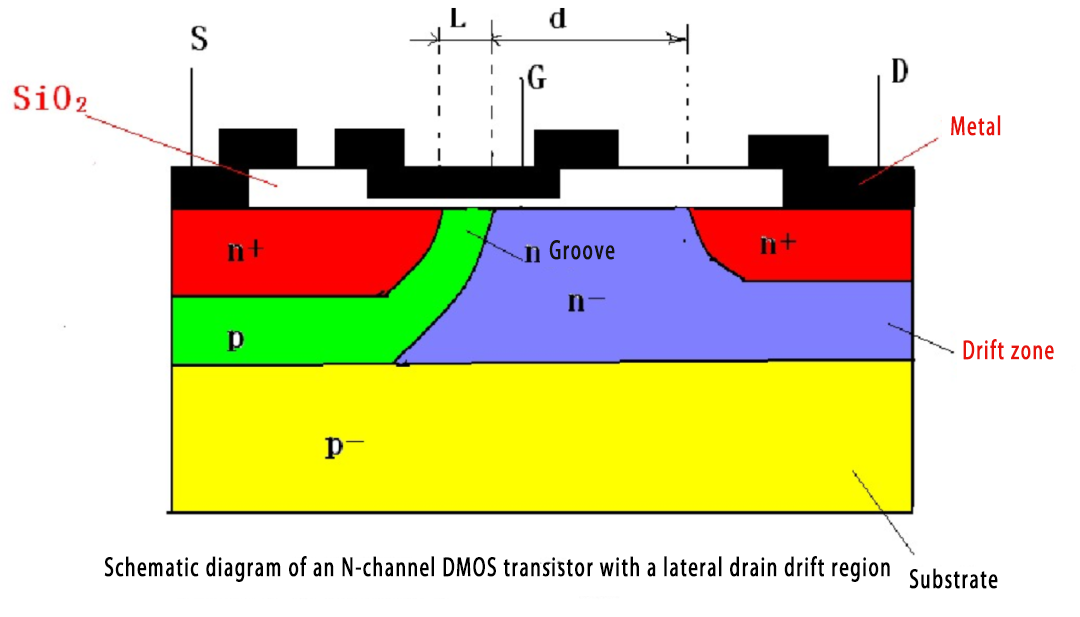

Afhangende van die rigting van die kanaal, kan DMOS in twee tipes verdeel word, naamlik vertikale dubbeldiffusie metaaloksied halfgeleier veldeffek transistor VDMOS (Vertical Double-Diffused MOSFET) en laterale dubbeldiffusie metaaloksied halfgeleier veldeffek transistor LDMOS (Lateral Double-Diffused MOSFET) -Verspreide MOSFET).

VDMOS-toestelle is ontwerp met 'n vertikale kanaal. In vergelyking met laterale DMOS-toestelle, het hulle hoër afbreekspanning en stroomhanteringsvermoëns, maar die aan-weerstand is steeds relatief groot.

LDMOS toestelle is ontwerp met 'n laterale kanaal en is asimmetriese krag MOSFET toestelle. In vergelyking met vertikale DMOS-toestelle, laat hulle laer aanweerstand en vinniger skakelspoed toe.

In vergelyking met tradisionele MOSFET's, het DMOS hoër aan-kapasitansie en laer weerstand, so dit word wyd gebruik in hoëkrag elektroniese toestelle soos kragskakelaars, kraggereedskap en elektriese voertuigaandrywings.

5. BiCMOS

Bipolêre CMOS is 'n tegnologie wat CMOS en bipolêre toestelle op dieselfde skyfie op dieselfde tyd integreer. Die basiese idee daarvan is om CMOS-toestelle as die hoofeenheidkring te gebruik, en bipolêre toestelle of stroombane by te voeg waar groot kapasitiewe ladings aangedryf moet word. Daarom het BiCMOS-stroombane die voordele van hoë integrasie en lae kragverbruik van CMOS-stroombane, en die voordele van hoëspoed- en sterk stroomaandryfvermoë van BJT-stroombane.

STMicroelectronics se BiCMOS SiGe (silicon germanium) tegnologie integreer RF, analoog en digitale dele op 'n enkele skyfie, wat die aantal eksterne komponente aansienlik kan verminder en kragverbruik kan optimaliseer.

6. BCD

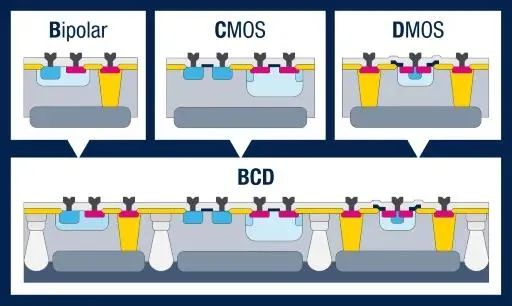

Bipolêre-CMOS-DMOS, hierdie tegnologie kan bipolêre, CMOS- en DMOS-toestelle op dieselfde skyfie maak, genaamd BCD-proses, wat die eerste keer suksesvol deur STMicroelectronics (ST) in 1986 ontwikkel is.

Bipolêr is geskik vir analoog stroombane, CMOS is geskik vir digitale en logiese stroombane, en DMOS is geskik vir krag- en hoëspanningstoestelle. BCD kombineer die voordele van die drie. Na voortdurende verbetering word BCD wyd gebruik in produkte op die gebied van kragbestuur, analoogdata-verkryging en kragaktuators. Volgens ST se amptelike webwerf is die volwasse proses vir BCD steeds rondom 100nm, 90nm is nog in prototipe-ontwerp, en 40nmBCD-tegnologie behoort tot sy volgende generasie produkte wat ontwikkel word.

Postyd: 10 September 2024