च्या वाढीसाठी मुख्य तंत्रज्ञानSiC एपिटॅक्सियलसाहित्य हे सर्वप्रथम दोष नियंत्रण तंत्रज्ञान आहे, विशेषत: दोष नियंत्रण तंत्रज्ञानासाठी जे उपकरणाच्या अपयशाची किंवा विश्वासार्हतेच्या ऱ्हासाची शक्यता असते. एपिटॅक्सियल वाढीच्या प्रक्रियेदरम्यान एपिटॅक्सियल थरात पसरलेल्या सब्सट्रेट दोषांच्या यंत्रणेचा अभ्यास, सब्सट्रेट आणि एपिटॅक्सियल थर यांच्यातील इंटरफेसवरील दोषांचे हस्तांतरण आणि परिवर्तन कायदे आणि दोषांचे न्यूक्लिएशन यंत्रणा हे सब्सट्रेट दोष आणि एपिटॅक्सियल स्ट्रक्चरल दोषांमधील सहसंबंध स्पष्ट करण्यासाठी आधार आहेत, जे सब्सट्रेट स्क्रीनिंग आणि एपिटॅक्सियल प्रक्रिया ऑप्टिमायझेशनला प्रभावीपणे मार्गदर्शन करू शकतात.

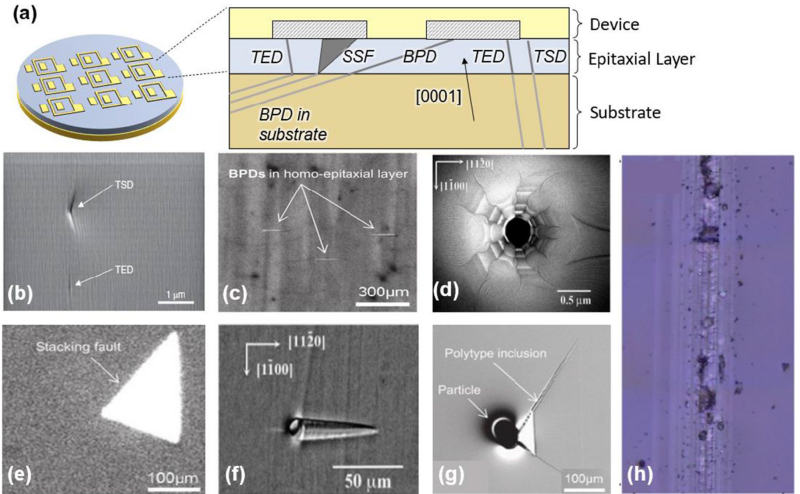

चे दोषसिलिकॉन कार्बाइड एपिटॅक्सियल थरप्रामुख्याने दोन श्रेणींमध्ये विभागले गेले आहेत: क्रिस्टल दोष आणि पृष्ठभाग आकारविज्ञान दोष. पॉइंट दोष, स्क्रू विस्थापन, सूक्ष्मनलिका दोष, कडा विस्थापन इत्यादींसह क्रिस्टल दोष बहुतेकदा SiC सब्सट्रेट्सवरील दोषांपासून उद्भवतात आणि एपिटॅक्सियल थरात पसरतात. पृष्ठभागावरील आकारविज्ञान दोष सूक्ष्मदर्शकाचा वापर करून उघड्या डोळ्यांनी थेट पाहिले जाऊ शकतात आणि त्यांच्यात विशिष्ट आकारविज्ञान वैशिष्ट्ये आहेत. पृष्ठभागावरील आकारविज्ञान दोषांमध्ये प्रामुख्याने समाविष्ट आहे: स्क्रॅच, त्रिकोणी दोष, गाजर दोष, डाउनफॉल आणि कण, आकृती 4 मध्ये दर्शविल्याप्रमाणे. एपिटॅक्सियल प्रक्रियेदरम्यान, परदेशी कण, सब्सट्रेट दोष, पृष्ठभागाचे नुकसान आणि एपिटॅक्सियल प्रक्रिया विचलन हे सर्व स्थानिक स्टेप फ्लो ग्रोथ मोडवर परिणाम करू शकतात, परिणामी पृष्ठभाग आकारविज्ञान दोष निर्माण होतात.

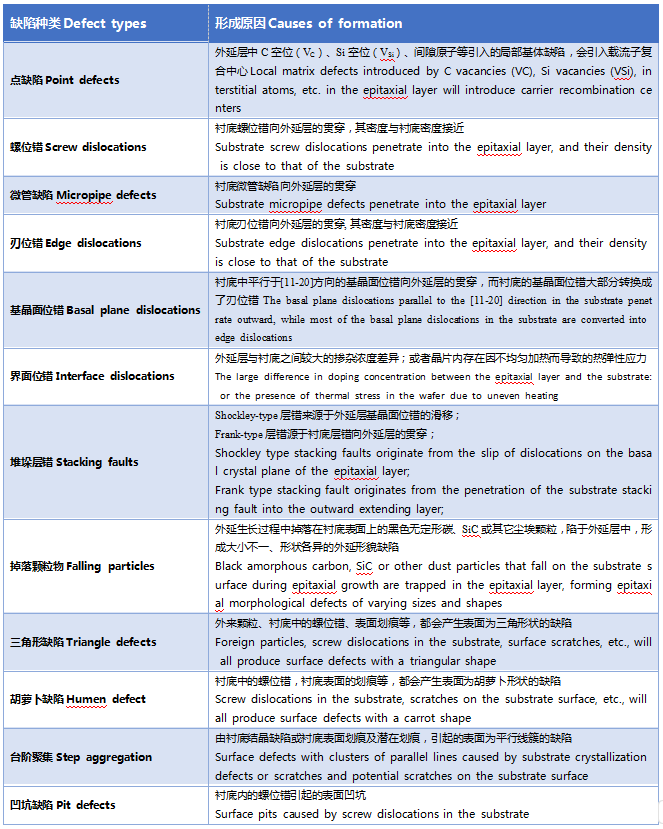

तक्ता १. SiC एपिटॅक्सियल थरांमध्ये सामान्य मॅट्रिक्स दोष आणि पृष्ठभागाच्या आकारविज्ञान दोषांच्या निर्मितीची कारणे

बिंदू दोष

बिंदू दोष एकाच जाळीच्या बिंदूवर किंवा अनेक जाळीच्या बिंदूंवर रिक्त जागा किंवा अंतरांमुळे तयार होतात आणि त्यांचा कोणताही अवकाशीय विस्तार नसतो. प्रत्येक उत्पादन प्रक्रियेत, विशेषतः आयन इम्प्लांटेशनमध्ये, बिंदू दोष उद्भवू शकतात. तथापि, ते शोधणे कठीण आहे आणि बिंदू दोषांचे रूपांतर आणि इतर दोषांमधील संबंध देखील बरेच गुंतागुंतीचे आहे.

मायक्रोपाइप्स (एमपी)

मायक्रोपाइप्स हे पोकळ स्क्रू डिस्लोकेशन असतात जे वाढीच्या अक्षावर पसरतात, ज्यामध्ये बर्गर वेक्टर <0001> असतो. मायक्रोट्यूबचा व्यास एका मायक्रॉनच्या अंशापासून दहा मायक्रॉनपर्यंत असतो. मायक्रोट्यूब SiC वेफर्सच्या पृष्ठभागावर मोठ्या खड्ड्यांसारख्या पृष्ठभागाची वैशिष्ट्ये दर्शवितात. सामान्यतः, मायक्रोट्यूबची घनता सुमारे 0.1~1cm-2 असते आणि व्यावसायिक वेफर उत्पादन गुणवत्ता देखरेखीमध्ये कमी होत राहते.

स्क्रू डिसलोकेशन (TSD) आणि एज डिसलोकेशन (TED)

SiC मधील विस्थापन हे उपकरणाच्या ऱ्हासाचे आणि अपयशाचे मुख्य स्रोत आहेत. स्क्रू विस्थापन (TSD) आणि एज विस्थापन (TED) दोन्ही अनुक्रमे <0001> आणि 1/3<11–20> च्या बर्गर वेक्टरसह वाढीच्या अक्षावर चालतात.

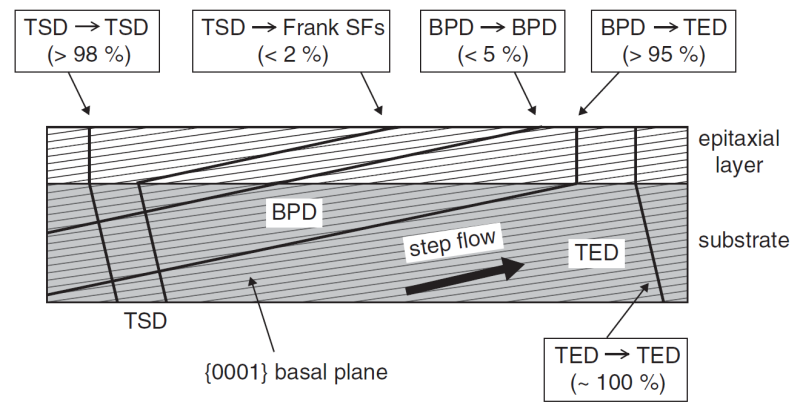

स्क्रू डिस्लोकेशन (TSD) आणि एज डिस्लोकेशन (TED) दोन्ही सब्सट्रेटपासून वेफर पृष्ठभागावर पसरू शकतात आणि लहान खड्ड्यांसारखे पृष्ठभाग वैशिष्ट्ये आणू शकतात (आकृती 4b). सामान्यतः, एज डिस्लोकेशनची घनता स्क्रू डिस्लोकेशनच्या सुमारे 10 पट असते. विस्तारित स्क्रू डिस्लोकेशन, म्हणजेच सब्सट्रेटपासून एपिलेयरपर्यंत पसरलेले, इतर दोषांमध्ये देखील रूपांतरित होऊ शकतात आणि वाढीच्या अक्षावर पसरू शकतात. दरम्यानSiC एपिटॅक्सियलवाढीदरम्यान, स्क्रू डिस्लोकेशन स्टॅकिंग फॉल्ट्स (SF) किंवा कॅरेट डिफेक्ट्समध्ये रूपांतरित होतात, तर एपिलियर्समधील एज डिस्लोकेशन एपिटॅक्सियल वाढीदरम्यान सब्सट्रेटमधून वारशाने मिळालेल्या बेसल प्लेन डिस्लोकेशन्स (BPDs) मधून रूपांतरित होतात असे दिसून आले आहे.

बेसिक प्लेन डिसलोकेशन (BPD)

SiC बेसल प्लेनवर स्थित, ज्याचा बर्गर वेक्टर 1/3 <11–20> आहे. SiC वेफर्सच्या पृष्ठभागावर BPD क्वचितच दिसतात. ते सहसा 1500 cm-2 घनतेसह सब्सट्रेटवर केंद्रित असतात, तर एपिलेयरमध्ये त्यांची घनता फक्त 10 cm-2 असते. फोटोल्युमिनेसेन्स (PL) वापरून BPDs शोधणे आकृती 4c मध्ये दर्शविल्याप्रमाणे रेषीय वैशिष्ट्ये दर्शवते. दरम्यानSiC एपिटॅक्सियलवाढीसह, विस्तारित बीपीडी स्टॅकिंग फॉल्ट्स (एसएफ) किंवा एज डिस्लोकेशन (टीईडी) मध्ये रूपांतरित होऊ शकतात.

स्टॅकिंग फॉल्ट्स (SFs)

SiC बेसल प्लेनच्या स्टॅकिंग अनुक्रमातील दोष. सब्सट्रेटमधील SFs वारशाने मिळाल्याने एपिटॅक्सियल लेयरमध्ये स्टॅकिंग फॉल्ट दिसू शकतात किंवा बेसल प्लेन डिस्लोकेशन (BPDs) आणि थ्रेडिंग स्क्रू डिस्लोकेशन (TSDs) च्या विस्तार आणि रूपांतरणाशी संबंधित असू शकतात. साधारणपणे, SFs ची घनता 1 सेमी-2 पेक्षा कमी असते आणि आकृती 4e मध्ये दाखवल्याप्रमाणे PL वापरून शोधल्यावर ते त्रिकोणी वैशिष्ट्य प्रदर्शित करतात. तथापि, SiC मध्ये विविध प्रकारचे स्टॅकिंग फॉल्ट तयार होऊ शकतात, जसे की शॉकली प्रकार आणि फ्रँक प्रकार, कारण प्लेनमधील स्टॅकिंग एनर्जी डिसऑर्डरची थोडीशी मात्रा देखील स्टॅकिंग अनुक्रमात लक्षणीय अनियमितता निर्माण करू शकते.

पडझड

वाढीच्या प्रक्रियेदरम्यान प्रतिक्रिया कक्षातील वरच्या आणि बाजूच्या भिंतींवर पडणाऱ्या कणांच्या थेंबातून मुख्यतः डाउनफॉल दोष उद्भवतो, जो प्रतिक्रिया कक्षातील ग्रेफाइट उपभोग्य वस्तूंच्या नियतकालिक देखभाल प्रक्रियेला अनुकूलित करून सुधारता येतो.

त्रिकोणी दोष

आकृती ४g मध्ये दाखवल्याप्रमाणे, हा एक ३C-SiC पॉलीटाइप समावेश आहे जो SiC एपिलियरच्या पृष्ठभागावर बेसल प्लेन दिशेने पसरतो. एपिटॅक्सियल वाढीदरम्यान SiC एपिलियरच्या पृष्ठभागावर पडणाऱ्या कणांमुळे ते निर्माण होऊ शकते. कण एपिलियरमध्ये एम्बेड केलेले असतात आणि वाढीच्या प्रक्रियेत व्यत्यय आणतात, परिणामी ३C-SiC पॉलीटाइप समावेश होतो, जे त्रिकोणी प्रदेशाच्या शिरोबिंदूंवर असलेल्या कणांसह तीक्ष्ण-कोन त्रिकोणी पृष्ठभागाची वैशिष्ट्ये दर्शवितात. अनेक अभ्यासांनी पृष्ठभागावरील ओरखडे, मायक्रोपाइप्स आणि वाढीच्या प्रक्रियेच्या अयोग्य पॅरामीटर्सना देखील पॉलीटाइप समावेशाचे कारण दिले आहे.

गाजर दोष

गाजर दोष हा एक स्टॅकिंग फॉल्ट कॉम्प्लेक्स आहे ज्याचे दोन टोक TSD आणि SF बेसल क्रिस्टल प्लेनवर असतात, जे फ्रँक-प्रकारच्या विस्थापनाने संपतात आणि गाजर दोषाचा आकार प्रिझमॅटिक स्टॅकिंग फॉल्टशी संबंधित असतो. या वैशिष्ट्यांचे संयोजन गाजर दोषाचे पृष्ठभाग आकारविज्ञान तयार करते, जे आकृती 4f मध्ये दर्शविल्याप्रमाणे 1 सेमी-2 पेक्षा कमी घनतेसह गाजर आकारासारखे दिसते. पॉलिशिंग स्क्रॅच, TSD किंवा सब्सट्रेट दोषांवर गाजर दोष सहजपणे तयार होतात.

ओरखडे

आकृती ४h मध्ये दाखवल्याप्रमाणे, उत्पादन प्रक्रियेदरम्यान SiC वेफर्सच्या पृष्ठभागावर ओरखडे निर्माण होतात आणि यांत्रिक नुकसान होते. SiC सब्सट्रेटवरील ओरखडे एपिलेयरच्या वाढीमध्ये अडथळा आणू शकतात, एपिलेयरमध्ये उच्च-घनतेचे विस्थापन निर्माण करू शकतात किंवा ओरखडे गाजर दोषांच्या निर्मितीचा आधार बनू शकतात. म्हणून, SiC वेफर्सना योग्यरित्या पॉलिश करणे अत्यंत महत्वाचे आहे कारण जेव्हा हे ओरखडे डिव्हाइसच्या सक्रिय क्षेत्रात दिसतात तेव्हा त्यांचा डिव्हाइसच्या कार्यक्षमतेवर लक्षणीय परिणाम होऊ शकतो.

इतर पृष्ठभागाचे आकारविज्ञान दोष

स्टेप बंचिंग हा SiC एपिटॅक्सियल ग्रोथ प्रक्रियेदरम्यान निर्माण होणारा पृष्ठभागावरील दोष आहे, जो SiC एपिलियरच्या पृष्ठभागावर ओब्ट्यूज त्रिकोण किंवा ट्रॅपेझॉइडल वैशिष्ट्ये निर्माण करतो. पृष्ठभागावरील खड्डे, अडथळे आणि डाग यासारखे इतर अनेक पृष्ठभाग दोष आहेत. हे दोष सहसा अप्रभावित वाढीच्या प्रक्रियेमुळे आणि पॉलिशिंग नुकसान अपूर्ण काढून टाकल्यामुळे होतात, ज्यामुळे डिव्हाइसच्या कार्यक्षमतेवर प्रतिकूल परिणाम होतो.

पोस्ट वेळ: जून-०५-२०२४