A uaiflefeumaidh e trì atharrachaidhean a dhèanamh gus a bhith na fhìor chip leth-chonnsachaidh: an toiseach, thèid an ingot cumadh bloc a ghearradh ann an uaifearan; san dàrna pròiseas, thèid transistors a ghràbhaladh air aghaidh an uaifeir tron phròiseas roimhe; mu dheireadh, thèid pacadh a dhèanamh, is e sin, tron phròiseas gearraidh, anuaiflea’ fàs na chip leth-chonnsachaidh iomlan. Chithear gur ann mar phàirt den phròiseas cùil a bhuineas am pròiseas pacaidh. Anns a’ phròiseas seo, thèid an wafer a ghearradh ann an grunn chips fa leth heicsahedron. Canar “Singulation” ris a’ phròiseas seo airson chips neo-eisimeileach fhaighinn, agus canar “gearradh wafer (Die Sawing)” ris a’ phròiseas airson bòrd na wafer a ghearradh ann an ciùban neo-eisimeileach. O chionn ghoirid, le leasachadh amalachadh leth-chonnsachaidh, tha tiugh anuaifleanair fàs nas taine agus nas taine, agus gu dearbh tha sin a’ toirt tòrr duilgheadas don phròiseas “singilte”.

Mean-fhàs dìsneadh wafer

Tha pròiseasan aghaidh is cùil air atharrachadh tro eadar-obrachadh ann an diofar dhòighean: faodaidh mean-fhàs phròiseasan cùil structar agus suidheachadh nan sgoltagan beaga heicsahedron a tha air an sgaradh bhon bhàs air an dearbhadh.uaifle, a bharrachd air structar agus suidheachadh nam padaichean (slighean ceangail dealain) air an wafer; air an làimh eile, tha mean-fhàs phròiseasan aghaidh air atharrachadh a dhèanamh air a’ phròiseas agus an dòigh-obrachuaifletanachadh cùil agus “die dicing” sa phròiseas cùil. Mar sin, bidh buaidh mhòr aig coltas a tha a’ sìor fhàs iom-fhillte air a’ phacaid air a’ phròiseas cùil. A bharrachd air an sin, atharraichidh an àireamh, an dòigh-obrach agus an seòrsa discing cuideachd a rèir an atharrachaidh ann an coltas a’ phacaid.

Sgrìobhaiche a' Dìsneachadh

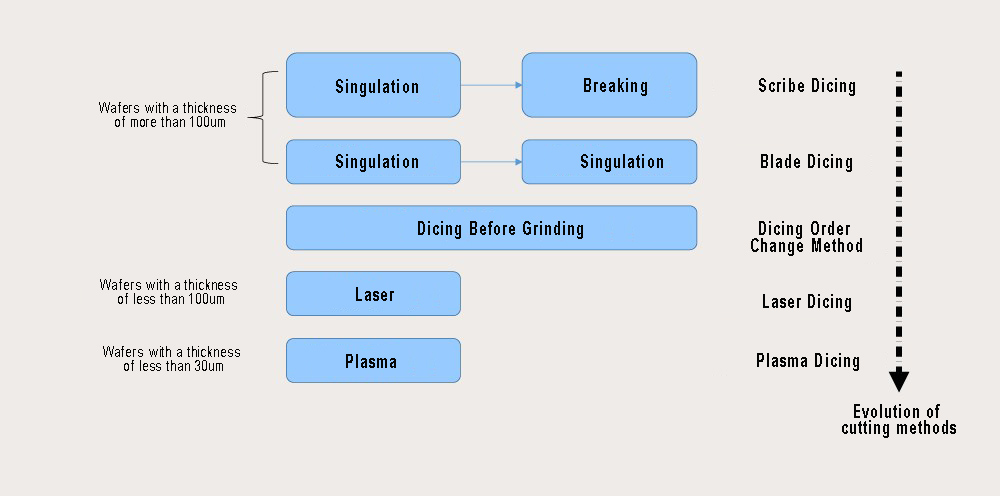

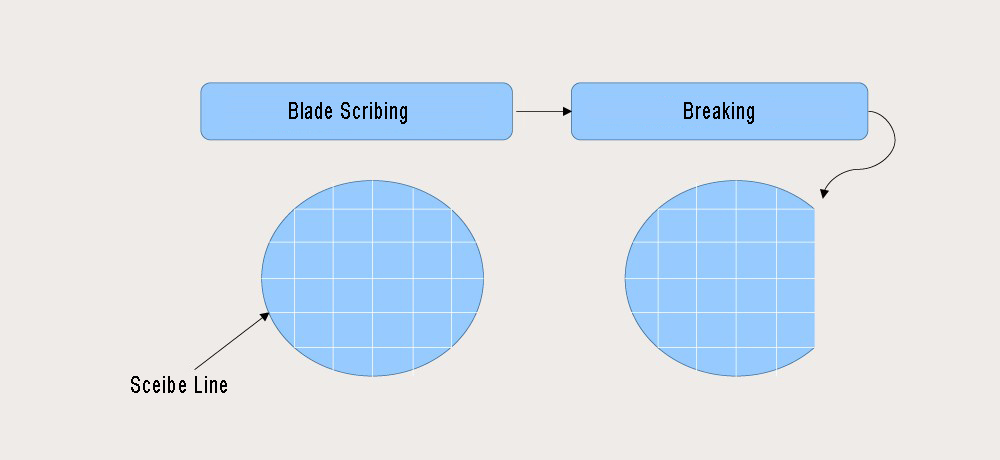

Anns na làithean tràtha, b’ e “briseadh” le bhith a’ cur feachd bhon taobh a-muigh an aon dhòigh dìsneachaidh a b’ urrainn an roinn.uaiflea-steach do bhàsan heicsahedron. Ach, tha eas-bhuannachdan aig an dòigh seo, is e sin sgoltadh no sgàineadh oir a’ chip bhig. A bharrachd air an sin, leis nach tèid na burrs air uachdar a’ mheatailt a thoirt air falbh gu tur, tha an uachdar gearraidh glè gharbh cuideachd.

Gus an duilgheadas seo fhuasgladh, thàinig an dòigh gearraidh “Scribing” gu bith, is e sin, mus tèid uachdar an “bhriseadh”.uaifleair a ghearradh gu mu leth na doimhneachd. Tha “sgrìobadh”, mar a tha an t-ainm ag ràdh, a’ toirt iomradh air a bhith a’ cleachdadh impeller gus taobh aghaidh a’ chliath-bhùird a shàbhadh (leth-ghearradh) ro-làimh. Anns na làithean tràtha, chleachd a’ mhòr-chuid de chliath-bhùird fo 6 òirlich an dòigh gearraidh seo de bhith an toiseach a’ “sgoltadh” eadar sgoltagan agus an uairsin a’ “briseadh”.

Dìosadh Lann no Sàbhadh Lann

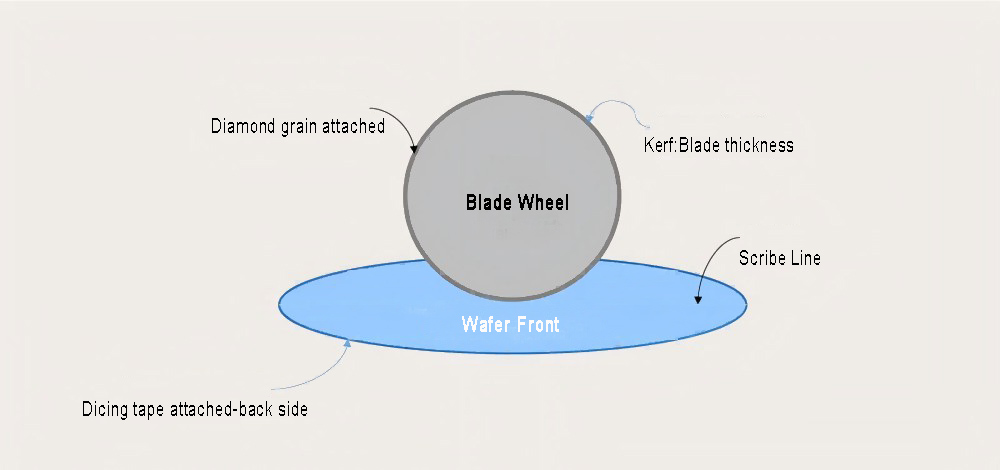

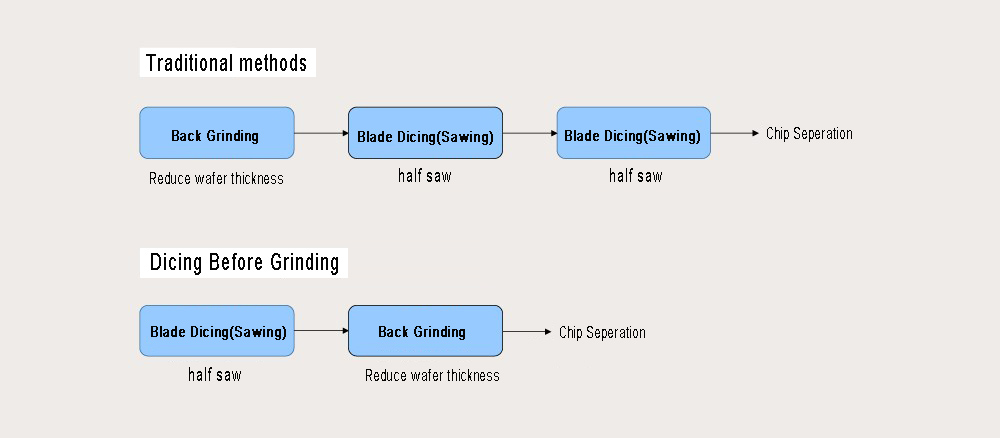

Mean air mhean, dh’fhàs an dòigh gearraidh “Scribing” gu bhith na dòigh gearraidh (no sàbhaidh) “Blade dicing”, a tha na dhòigh gearraidh le lann dà no trì thursan ann an sreath. Faodaidh an dòigh gearraidh “Blade” dèanamh suas airson iongantas sgoltagan beaga a’ rùsgadh nuair a bhios iad “a’ briseadh” às deidh “scribing”, agus faodaidh e sgoltagan beaga a dhìon rè a’ phròiseis “singulation”. Tha gearradh “Blade” eadar-dhealaichte bhon ghearradh “dicing” roimhe, is e sin, às deidh gearradh “lann”, chan eil e “a’ briseadh”, ach a’ gearradh a-rithist le lann. Mar sin, canar dòigh “step dicing” ris cuideachd.

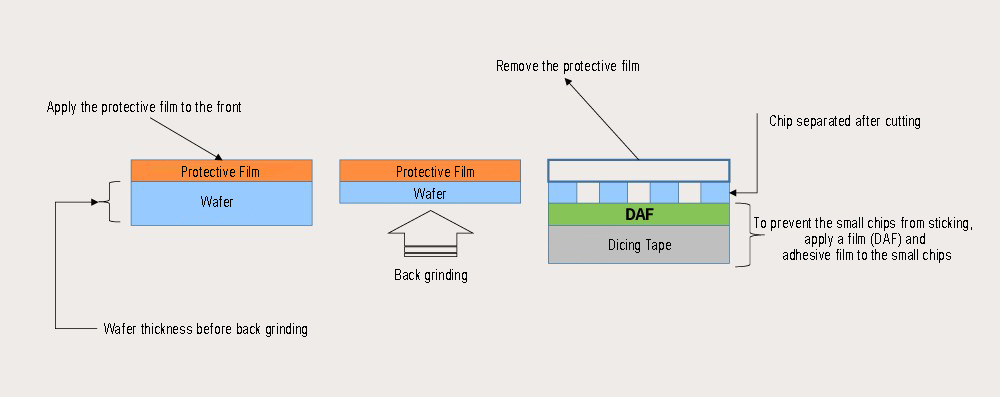

Gus an wafer a dhìon bho mhilleadh bhon taobh a-muigh rè a’ phròiseas gearraidh, thèid film a chuir air an wafer ro-làimh gus dèanamh cinnteach à “singling” nas sàbhailte. Rè a’ phròiseas “back bleith”, thèid am film a cheangal ri aghaidh an wafer. Ach air an làimh eile, ann an gearradh “lann”, bu chòir am film a bhith ceangailte ri cùl an wafer. Rè ceangal die eutectic (ceangal die, a’ daingneachadh nan sgoltagan air an sgaradh air a’ PCB no frèam stèidhichte), tuitidh am film a tha ceangailte ris a’ chùl dheth gu fèin-ghluasadach. Air sgàth an fhrith-bhualadh àrd rè gearradh, bu chòir uisge DI a bhith air a spraeadh gu leantainneach bho gach taobh. A bharrachd air an sin, bu chòir an impeller a bhith ceangailte le mìrean daoimean gus an tèid na sliseagan a ghearradh nas fheàrr. Aig an àm seo, feumaidh an gearradh (tiugh lann: leud clais) a bhith co-ionnan agus chan fhaod e a bhith nas motha na leud clais an dìosganaich.

Airson ùine mhòr, b’ e sàbhadh an dòigh gearraidh thraidiseanta as fharsainge a chaidh a chleachdadh. Is e a’ bhuannachd as motha a th’ aige gum faod e àireamh mhòr de wafers a ghearradh ann an ùine ghoirid. Ach, ma thèid astar beathachaidh an t-sliseag a mheudachadh gu mòr, bidh an cothrom gun tèid oir na sliseagan a rùsgadh ag àrdachadh. Mar sin, bu chòir àireamh rothlaidhean an impeller a bhith air a smachdachadh aig timcheall air 30,000 uair sa mhionaid. Chithear gu bheil teicneòlas pròiseas leth-chonnsachaidh gu tric na dhìomhaireachd a chruinnicheas mean air mhean tro ùine fhada de chruinneachadh agus deuchainn is mearachd (anns an ath earrann air ceangal eutectic, bruidhnidh sinn air an t-susbaint mu ghearradh agus DAF).

Dìsneachadh mus tèid bleith (DBG): tha an t-sreath gearraidh air an dòigh atharrachadh

Nuair a thèid gearradh lann a dhèanamh air wafer le trast-thomhas de 8 òirleach, chan eil feum a bhith draghail mu bhith a’ rùsgadh no a’ sgàineadh oir na sliseagan. Ach mar a bhios trast-thomhas na wafer ag àrdachadh gu 21 òirleach agus an tighead a’ fàs gu math tana, bidh iongantas rùsgadh is sgàineadh a’ tòiseachadh a’ nochdadh a-rithist. Gus a’ bhuaidh chorporra air an wafer a lughdachadh gu mòr rè a’ phròiseas gearraidh, bidh dòigh DBG de “dhìosadh mus tèid a bleith” a’ dol an àite an t-sreath gearraidh traidiseanta. Eu-coltach ris an dòigh gearraidh “lann” traidiseanta a bhios a’ gearradh gu leantainneach, bidh DBG an toiseach a’ dèanamh gearradh “lann”, agus an uairsin mean air mhean a’ tanachadh tighead na wafer le bhith a’ tanachadh taobh cùil gu leantainneach gus an tèid a’ chip a sgoltadh. Faodar a ràdh gur e dreach ùraichte den dòigh gearraidh “lann” a bh’ ann roimhe a th’ ann an DBG. Leis gun urrainn dha buaidh an dàrna gearraidh a lughdachadh, tha an dòigh DBG air a bhith mòr-chòrdte gu luath ann am “pacadh ìre wafer”.

Dìosadh Leusair

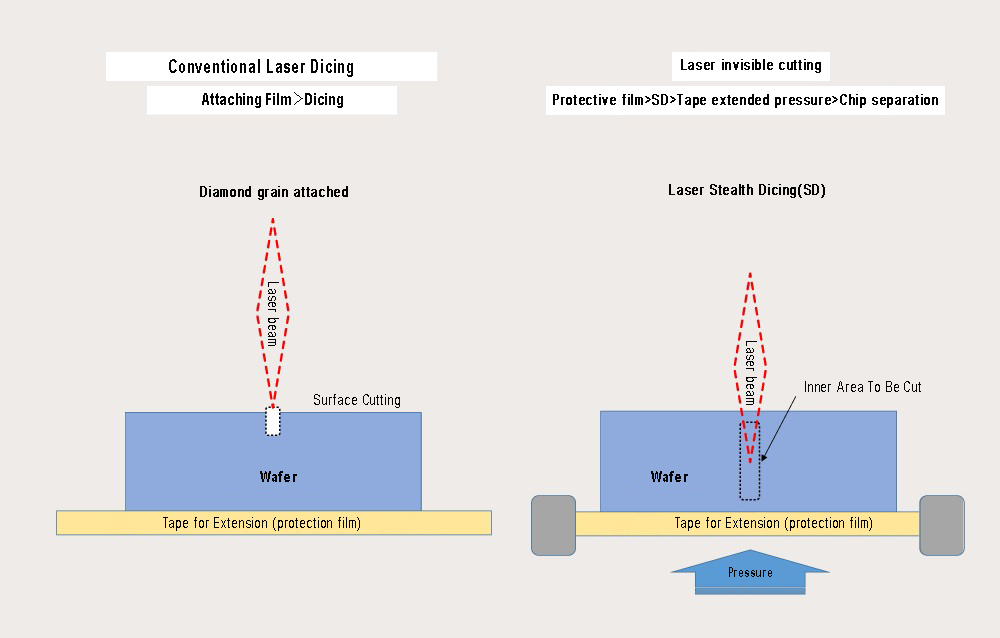

Bidh am pròiseas pasgan sgèile sliseagan ìre-wafer (WLCSP) a’ cleachdadh gearradh leusair sa mhòr-chuid. Faodaidh gearradh leusair lùghdachadh a dhèanamh air iongantas leithid rùsgadh agus sgàineadh, agus mar sin sgoltagan de chàileachd nas fheàrr fhaighinn, ach nuair a tha tiugh an wafer nas motha na 100μm, thèid an cinneasachd a lùghdachadh gu mòr. Mar sin, thathas ga chleachdadh sa mhòr-chuid air wafers le tiugh nas lugha na 100μm (gu ìre mhath tana). Bidh gearradh leusair a’ gearradh silicon le bhith a’ cur leusair àrd-lùtha air clais sgrìobhaidh an wafer. Ach, nuair a thathar a’ cleachdadh an dòigh gearraidh leusair àbhaisteach (Leusair Àbhaisteach), feumar film dìon a chuir air uachdar an wafer ro-làimh. Leis gu bheil uachdar an wafer air a theasachadh no air a shoilleireachadh le leusair, bidh na ceanglaichean corporra sin a’ cruthachadh claisean air uachdar an wafer, agus bidh na pìosan silicon gearraichte cuideachd a’ cumail ris an uachdar. Chithear gu bheil an dòigh gearraidh leusair traidiseanta cuideachd a’ gearradh uachdar an wafer gu dìreach, agus san t-seagh seo, tha e coltach ris an dòigh gearraidh “lann”.

’S e dòigh a th’ ann an Stealth Dicing (SD) airson an toiseach taobh a-staigh a’ chlais a ghearradh le lùth laser, agus an uairsin cuideam bhon taobh a-muigh a chuir air an teip a tha ceangailte ris a’ chùl gus a bhriseadh, agus mar sin a’ sgaradh a’ chip. Nuair a chuirear cuideam air an teip air a’ chùl, thèid an clias a thogail suas sa bhad air sgàth sìneadh an teip, agus mar sin a’ sgaradh a’ chip. Is iad na buannachdan a tha aig SD thairis air an dòigh gearraidh laser traidiseanta: an toiseach, chan eil sprùilleach silicon ann; san dàrna àite, tha an kerf (Kerf: leud clais an sgrìobhaiche) cumhang, agus mar sin gheibhear barrachd chips. A bharrachd air an sin, thèid an iongantas rùsgadh is sgàineadh a lughdachadh gu mòr le bhith a’ cleachdadh an dòigh SD, a tha deatamach do chàileachd iomlan a’ ghearraidh. Mar sin, tha e glè choltach gum bi an dòigh SD mar an teicneòlas as mòr-chòrdte san àm ri teachd.

Dìosadh Plasma

’S e teicneòlas a chaidh a leasachadh o chionn ghoirid a th’ ann an gearradh plasma a bhios a’ cleachdadh gràbhaladh plasma gus gearradh rè a’ phròiseas saothrachaidh (Fab). Bidh gearradh plasma a’ cleachdadh stuthan leth-ghasach an àite lionntan, agus mar sin tha a’ bhuaidh air an àrainneachd an ìre mhath beag. Agus tha an dòigh air an wafer gu lèir a ghearradh aig an aon àm air a ghabhail os làimh, agus mar sin tha an astar “gearraidh” an ìre mhath luath. Ach, bidh an dòigh plasma a’ cleachdadh gas ath-bhualadh ceimigeach mar stuth amh, agus tha am pròiseas gràbhaladh gu math toinnte, agus mar sin tha sruth a’ phròiseis an ìre mhath trom. Ach an taca ri gearradh “lann” agus gearradh laser, chan eil gearradh plasma ag adhbhrachadh milleadh air uachdar an wafer, agus mar sin a’ lughdachadh an ìre locht agus a’ faighinn barrachd sgoltagan.

O chionn ghoirid, leis gun deach tiughas nan uaifearan a lùghdachadh gu 30μm, agus gu bheil tòrr copair (Cu) no stuthan le cunbhalachd dielectric ìosal (Low-k) gan cleachdadh. Mar sin, gus casg a chuir air burrs (Burr), bidh dòighean gearraidh plasma air am brosnachadh cuideachd. Gu dearbh, tha teicneòlas gearraidh plasma cuideachd a’ sìor leasachadh. Tha mi a’ creidsinn, a dh’ aithghearr, nach bi feum air masg sònraichte a chaitheamh nuair a bhios tu a’ seargadh, oir is e seo prìomh stiùireadh leasachaidh gearradh plasma.

Leis gu bheil tiugh nan uaifearan air a bhith air a lùghdachadh gu leantainneach bho 100μm gu 50μm agus an uairsin gu 30μm, tha na dòighean gearraidh airson sgoltagan neo-eisimeileach fhaighinn air a bhith ag atharrachadh agus a’ leasachadh cuideachd bho bhith a’ gearradh “briseadh” agus “lann” gu gearradh leusair agus gearradh plasma. Ged a tha na dòighean gearraidh a tha a’ sìor fhàs nas aibidh air cosgais cinneasachaidh a’ phròiseis gearraidh fhèin a mheudachadh, air an làimh eile, le bhith a’ lughdachadh gu mòr na rudan nach eilear ag iarraidh leithid rùsgadh agus sgàineadh a bhios gu tric a’ tachairt ann an gearradh sgoltagan leth-chonnsachaidh agus a’ meudachadh an àireamh de sgoltagan a gheibhear gach aonad uaifearan, tha cosgais cinneasachaidh aon sgoltagan air gluasad sìos a nochdadh. Gu dearbh, tha an àrdachadh ann an àireamh nan sgoltagan a gheibhear gach aonad farsaingeachd den uaifearan ceangailte gu dlùth ri lùghdachadh ann an leud sràid an dìsnean. Le bhith a’ cleachdadh gearradh plasma, gheibhear faisg air 20% barrachd sgoltagan an taca ri bhith a’ cleachdadh an dòigh gearraidh “lann”, agus is e sin cuideachd prìomh adhbhar carson a tha daoine a’ taghadh gearradh plasma. Le leasachadh agus atharrachaidhean uaifearan, coltas sgoltagan agus dòighean pacaidh, tha diofar phròiseasan gearraidh leithid teicneòlas giullachd uaifearan agus DBG a’ nochdadh cuideachd.

Àm puist: 10 Dàmhair 2024