Croeso i'n gwefan ar gyfer gwybodaeth am gynnyrch ac ymgynghori.

Ein gwefan:https://www.vet-china.com/

Wrth i brosesau gweithgynhyrchu lled-ddargludyddion barhau i wneud datblygiadau arloesol, mae datganiad enwog o'r enw "Moore's Law" wedi bod yn cylchredeg yn y diwydiant. Fe'i cynigiwyd gan Gordon Moore, un o sylfaenwyr Intel, ym 1965. Ei gynnwys craidd yw: bydd nifer y transistorau y gellir eu gosod ar gylched integredig yn dyblu tua bob 18 i 24 mis. Mae'r gyfraith hon nid yn unig yn ddadansoddiad a rhagfynegiad o duedd datblygu'r diwydiant, ond hefyd yn rym gyrru ar gyfer datblygu prosesau gweithgynhyrchu lled-ddargludyddion - popeth yw gwneud transistorau gyda maint llai a pherfformiad sefydlog. O'r 1950au i'r presennol, tua 70 mlynedd, mae cyfanswm o dechnolegau proses BJT, MOSFET, CMOS, DMOS, a BiCMOS hybrid a BCD wedi'u datblygu.

1. BJT

Transistor cyffordd deubegwn (BJT), a elwir yn gyffredin yn triode. Mae'r llif gwefr yn y transistor yn bennaf oherwydd symudiad tryledu a drifft cludwyr ar gyffordd PN. Gan ei fod yn cynnwys llif electronau a thyllau, fe'i gelwir yn ddyfais deubegwn.

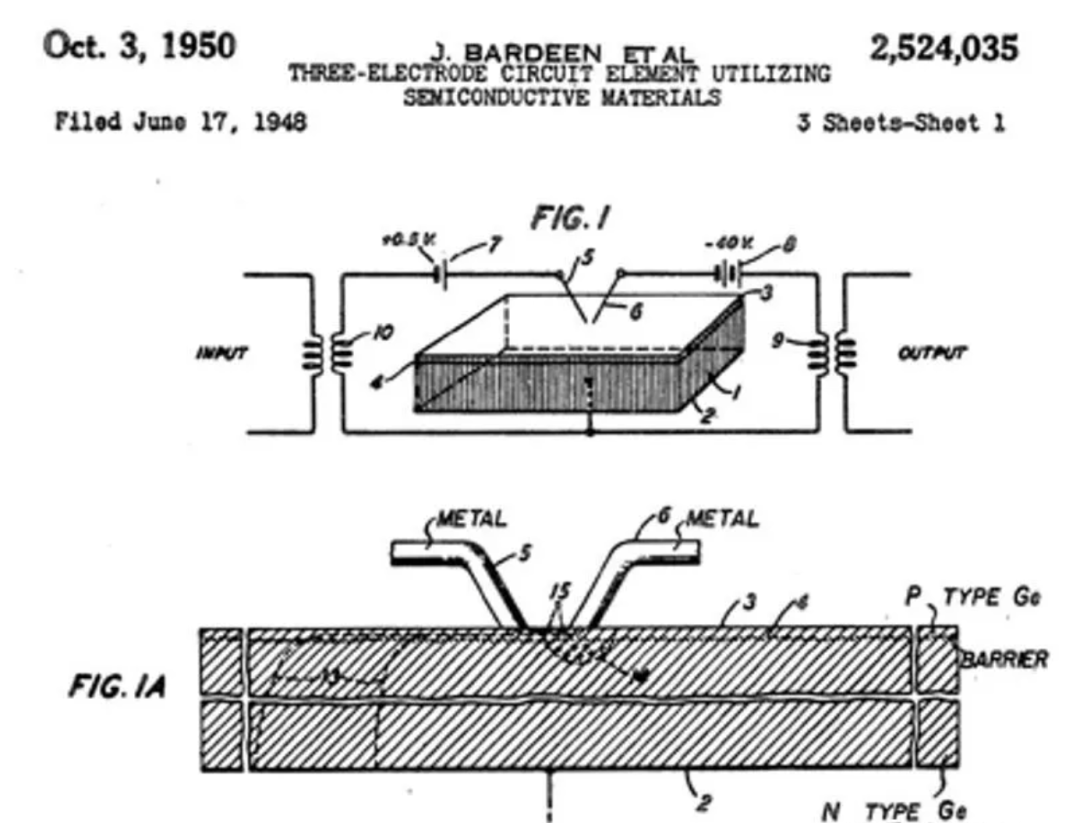

Edrych yn ôl ar hanes ei eni. Oherwydd y syniad o ddisodli triawdau gwactod â mwyhaduron solet, cynigiodd Shockley gynnal ymchwil sylfaenol ar lled-ddargludyddion yn haf 1945. Yn ail hanner 1945, sefydlodd Bell Labs grŵp ymchwil ffiseg cyflwr solet dan arweiniad Shockley. Yn y grŵp hwn, nid yn unig y mae ffisegwyr, ond hefyd peirianwyr cylched a chemegwyr, gan gynnwys Bardeen, ffisegydd damcaniaethol, a Brattain, ffisegydd arbrofol. Ym mis Rhagfyr 1947, digwyddodd digwyddiad a ystyriwyd yn garreg filltir gan genedlaethau diweddarach yn wych - llwyddodd Bardeen a Brattain i ddyfeisio'r transistor pwynt-cyswllt germaniwm cyntaf yn y byd gyda mwyhad cyfredol.

Transistor pwynt cyswllt cyntaf Bardeen a Brattain

Yn fuan wedi hynny, dyfeisiodd Shockley y transistor cyffordd deubegwn ym 1948. Cynigiodd y gall y transistor fod yn cynnwys dwy gyffordd pn, un â thuedd ymlaen a'r llall yn rhagfarnllyd, a chafodd batent ym mis Mehefin 1948. Ym 1949, cyhoeddodd y ddamcaniaeth fanwl o weithrediad y transistor cyffordd. Fwy na dwy flynedd yn ddiweddarach, datblygodd gwyddonwyr a pheirianwyr yn Bell Labs broses i gyflawni masgynhyrchu transistorau cyffordd (carreg filltir ym 1951), gan agor cyfnod newydd o dechnoleg electronig. I gydnabod eu cyfraniadau at ddyfeisio transistorau, enillodd Shockley, Bardeen a Brattain Wobr Nobel mewn Ffiseg 1956 ar y cyd.

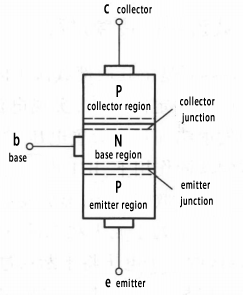

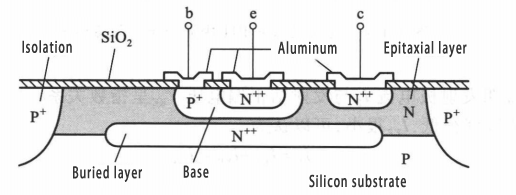

Diagram strwythurol syml o transistor cyffordd deubegwn NPN

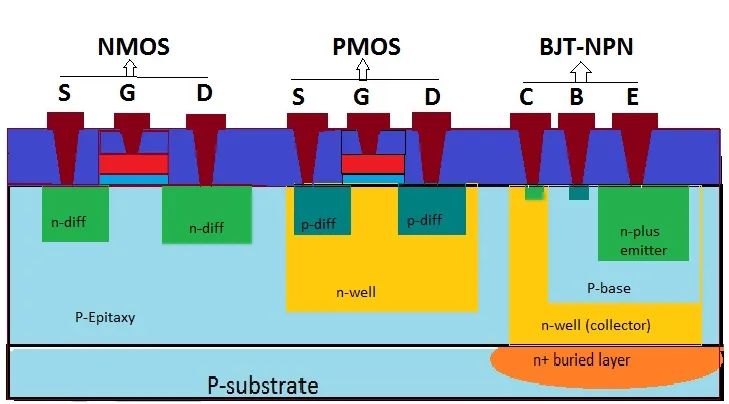

O ran strwythur transistorau cyffordd deubegwn, BJTs cyffredin yw NPN a PNP. Dangosir y strwythur mewnol manwl yn y ffigur isod. Y rhanbarth lled-ddargludyddion amhuredd sy'n cyfateb i'r allyrrydd yw'r rhanbarth allyrrydd, sydd â chrynodiad dopio uchel; y rhanbarth lled-ddargludyddion amhuredd sy'n cyfateb i'r sylfaen yw'r rhanbarth sylfaen, sydd â lled tenau iawn a chrynodiad dopio isel iawn; y rhanbarth lled-ddargludyddion amhuredd sy'n cyfateb i'r casglwr yw'r rhanbarth casglwr, sydd ag ardal fawr a chrynodiad dopio isel iawn.

Manteision technoleg BJT yw cyflymder ymateb uchel, traws-ddargludedd uchel (mae newidiadau foltedd mewnbwn yn cyfateb i newidiadau cerrynt allbwn mawr), sŵn isel, cywirdeb analog uchel, a gallu gyrru cyfredol cryf; yr anfanteision yw integreiddio isel (ni ellir lleihau dyfnder fertigol gyda maint ochrol) a defnydd pŵer uchel.

2. MOS

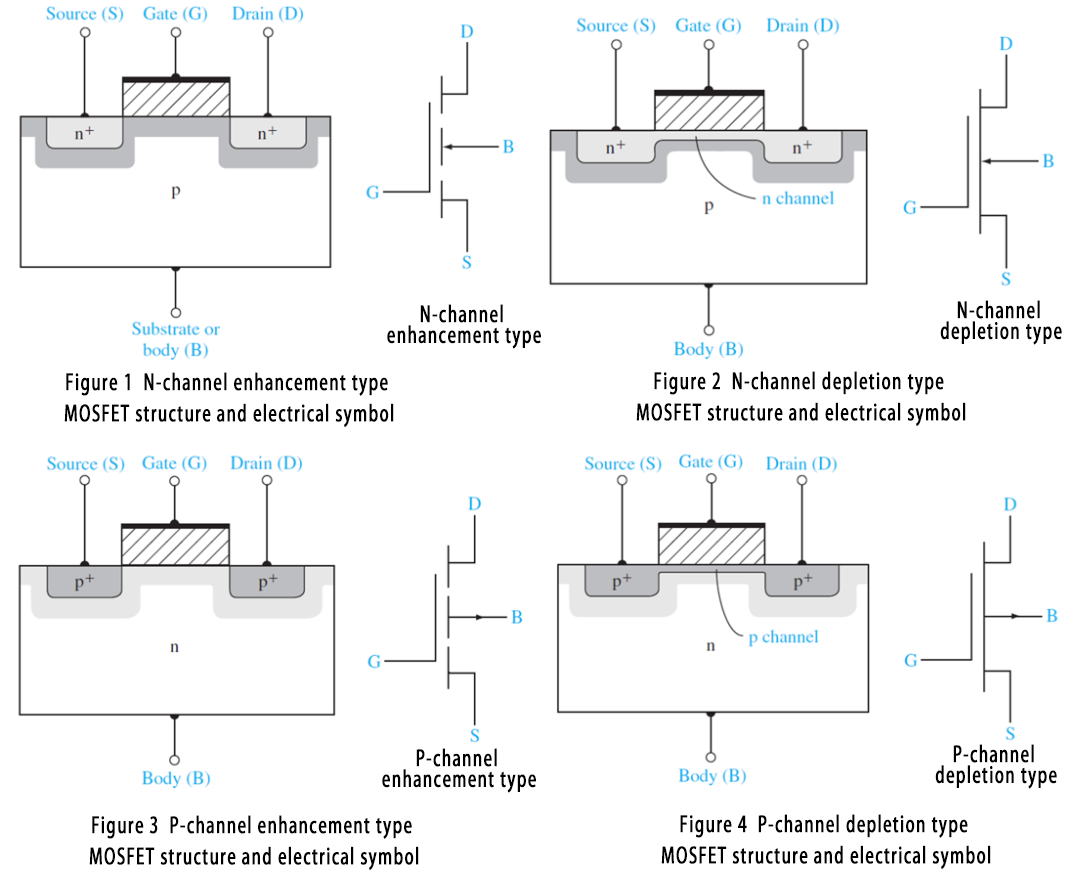

Transistor Effaith Maes Lled-ddargludyddion Metel Ocsid (FET Lled-ddargludyddion Metel Ocsid), hynny yw, transistor effaith maes sy'n rheoli switsh y sianel ddargludol lled-ddargludyddion (S) trwy gymhwyso foltedd i giât yr haen fetel (alwminiwm M-metel) a'r ffynhonnell trwy'r haen ocsid (haen O-inswleiddio SiO2) i gynhyrchu effaith y maes trydan. Gan fod y giât a'r ffynhonnell, a'r giât a'r draen yn cael eu hynysu gan yr haen inswleiddio SiO2, gelwir MOSFET hefyd yn transistor effaith cae giât wedi'i inswleiddio. Ym 1962, cyhoeddodd Bell Labs y datblygiad llwyddiannus yn swyddogol, a ddaeth yn un o'r cerrig milltir pwysicaf yn hanes datblygiad lled-ddargludyddion a gosododd y sylfaen dechnegol yn uniongyrchol ar gyfer dyfodiad cof lled-ddargludyddion.

Gellir rhannu MOSFET yn sianel P a sianel N yn ôl y math o sianel dargludol. Yn ôl osgled foltedd y giât, gellir ei rannu'n: math disbyddu-pan fo foltedd y giât yn sero, mae sianel ddargludol rhwng y draen a'r ffynhonnell; gwella math-ar gyfer dyfeisiau sianel N (P), mae sianel dargludol dim ond pan fydd y foltedd giât yn fwy na (llai na) sero, a MOSFET pŵer yn bennaf N math gwella sianel.

Mae'r prif wahaniaethau rhwng MOS a thriawd yn cynnwys y pwyntiau canlynol, ond heb fod yn gyfyngedig iddynt:

-Mae triawdau yn ddyfeisiadau deubegwn oherwydd bod cludwyr mwyafrifol a lleiafrifol yn cymryd rhan mewn dargludiad ar yr un pryd; tra bod MOS ond yn dargludo trydan trwy gludwyr mwyafrifol mewn lled-ddargludyddion, ac fe'i gelwir hefyd yn transistor unipolar.

-Mae triawdau yn ddyfeisiadau a reolir gan gyfredol gyda defnydd pŵer cymharol uchel; tra bod MOSFETs yn ddyfeisiau a reolir gan foltedd gyda defnydd pŵer isel.

-Mae gan driawdau ar-wrthiant mawr, tra bod gan diwbiau MOS ar-ymwrthedd bach, dim ond ychydig gannoedd o filiohms. Mewn dyfeisiau trydanol presennol, defnyddir tiwbiau MOS yn gyffredinol fel switshis, yn bennaf oherwydd bod effeithlonrwydd MOS yn gymharol uchel o'i gymharu â thriawdau.

-Mae gan driawdau gost gymharol fanteisiol, ac mae tiwbiau MOS yn gymharol ddrud.

-Y dyddiau hyn, tiwbiau MOS yn cael eu defnyddio i gymryd lle triodes yn y rhan fwyaf o senarios. Dim ond mewn rhai senarios pŵer isel neu bŵer-ansensitif, byddwn yn defnyddio triawdau gan ystyried y fantais pris.

3. CMOS

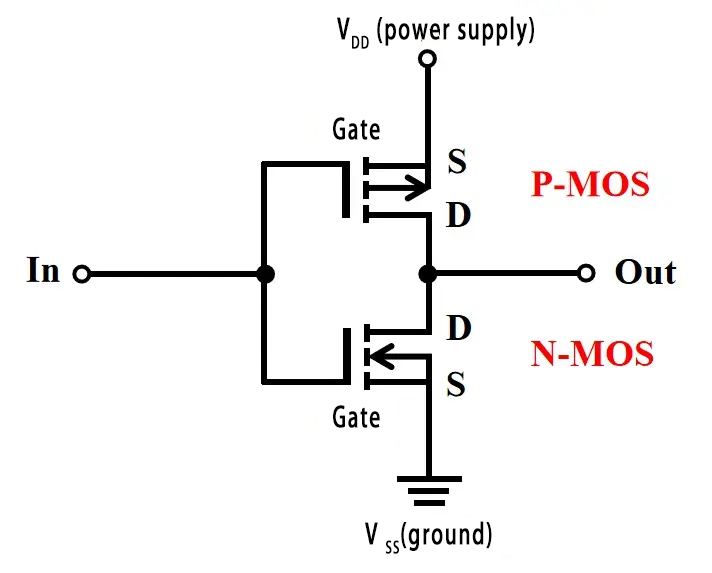

Lled-ddargludyddion Metel Ocsid Cyflenwol: Mae technoleg CMOS yn defnyddio transistorau lled-ddargludyddion lled-ddargludyddion metel ocsid math-p a n-math (MOSFETs) i adeiladu dyfeisiau electronig a chylchedau rhesymeg. Mae'r ffigur canlynol yn dangos gwrthdröydd CMOS cyffredin, a ddefnyddir ar gyfer trosi "1→0" neu "0→1".

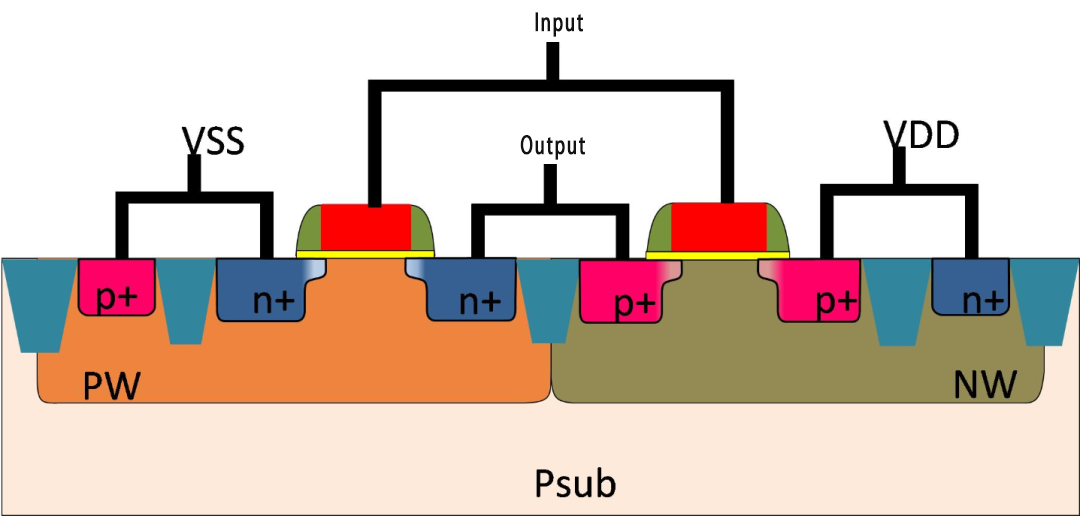

Mae'r ffigur canlynol yn groestoriad CMOS nodweddiadol. NMS yw'r ochr chwith, a'r ochr dde yw PMOS. Mae polion G y ddau MOS wedi'u cysylltu â'i gilydd fel mewnbwn giât cyffredin, ac mae'r polion D wedi'u cysylltu â'i gilydd fel allbwn draen cyffredin. Mae VDD wedi'i gysylltu â ffynhonnell PMOS, ac mae VSS wedi'i gysylltu â ffynhonnell NMOS.

Ym 1963, dyfeisiodd Wanlass a Sah o Fairchild Semiconductor y gylched CMOS. Ym 1968, datblygodd Corfforaeth Radio America (RCA) y cynnyrch cylched integredig CMOS cyntaf, ac ers hynny, mae cylched CMOS wedi cyflawni datblygiad gwych. Ei fanteision yw defnydd pŵer isel ac integreiddio uchel (gall proses STI / LOCOS wella integreiddio ymhellach); ei anfantais yw bodolaeth effaith clo (defnyddir gogwydd gwrthdro cyffordd PN fel ynysu rhwng tiwbiau MOS, a gall ymyrraeth ffurfio dolen well yn hawdd a llosgi'r cylched).

4. DMOS

Lled-ddargludydd Metel Ocsid Gwasgaredig Dwbl: Yn debyg i strwythur dyfeisiau MOSFET cyffredin, mae ganddo hefyd ffynhonnell, draen, giât ac electrodau eraill, ond mae foltedd dadelfennu pen y draen yn uchel. Defnyddir proses tryledu dwbl.

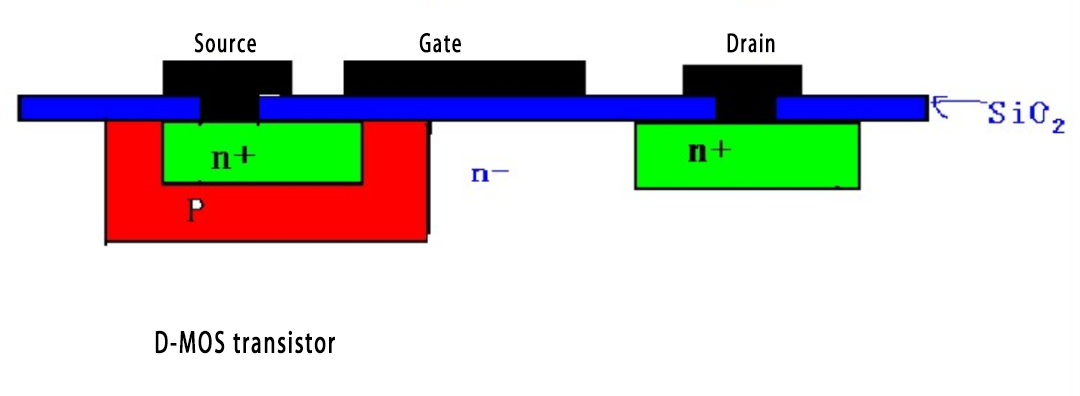

Mae'r ffigur isod yn dangos y trawstoriad o DMOS sianel N safonol. Defnyddir y math hwn o ddyfais DMOS fel arfer mewn cymwysiadau newid ochr isel, lle mae ffynhonnell y MOSFET wedi'i gysylltu â'r ddaear. Yn ogystal, mae DMOS P-sianel. Defnyddir y math hwn o ddyfais DMOS fel arfer mewn cymwysiadau newid ochr uchel, lle mae ffynhonnell y MOSFET wedi'i gysylltu â foltedd positif. Yn debyg i CMOS, mae dyfeisiau DMOS cyflenwol yn defnyddio MOSFETs N-sianel a P-sianel ar yr un sglodyn i ddarparu swyddogaethau newid cyflenwol.

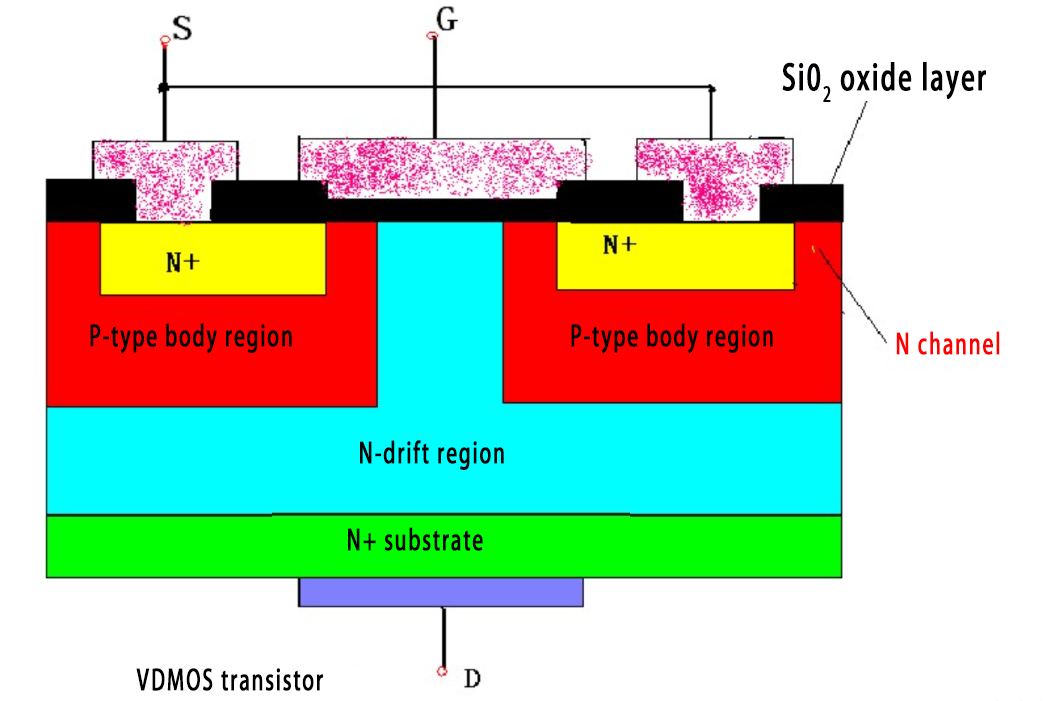

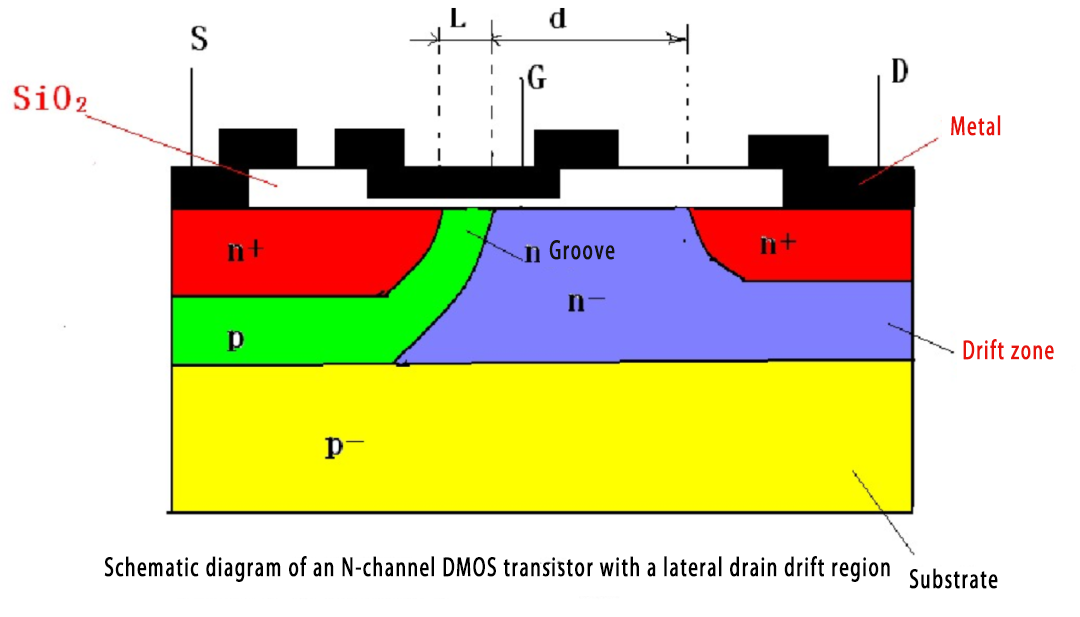

Yn dibynnu ar gyfeiriad y sianel, gellir rhannu DMOS yn ddau fath, sef effaith cae lled-ddargludyddion metel ocsid dwbl-tryledol fertigol transistor VDMOS (MOSFET Dwbl-Gwledol Fertigol) ac effaith maes lled-ddargludyddion metel ocsid gwasgaredig dwbl ochrol transistor LDMOS (Lateral Double -MOSFET gwasgaredig).

Mae dyfeisiau VDMOS wedi'u cynllunio gyda sianel fertigol. O'u cymharu â dyfeisiau DMOS ochrol, mae ganddyn nhw foltedd chwalu uwch a galluoedd trin cyfredol, ond mae'r ar-ymwrthedd yn dal yn gymharol fawr.

Mae dyfeisiau LDMOS wedi'u cynllunio gyda sianel ochrol ac maent yn ddyfeisiau MOSFET pŵer anghymesur. O'u cymharu â dyfeisiau DMOS fertigol, maent yn caniatáu ar-ymwrthedd is a chyflymder newid cyflymach.

O'i gymharu â MOSFETs traddodiadol, mae gan DMOS gynhwysedd uwch a gwrthiant is, felly fe'i defnyddir yn helaeth mewn dyfeisiau electronig pŵer uchel fel switshis pŵer, offer pŵer a gyriannau cerbydau trydan.

5. BiCMOS

Mae CMOS deubegwn yn dechnoleg sy'n integreiddio CMOS a dyfeisiau deubegwn ar yr un sglodyn ar yr un pryd. Ei syniad sylfaenol yw defnyddio dyfeisiau CMOS fel y brif gylched uned, ac ychwanegu dyfeisiau neu gylchedau deubegwn lle mae angen gyrru llwythi capacitive mawr. Felly, mae gan gylchedau BiCMOS fanteision integreiddio uchel a defnydd pŵer isel o gylchedau CMOS, a manteision cyflymder uchel a galluoedd gyrru cyfredol cryf cylchedau BJT.

Mae technoleg BiCMOS SiGe (silicon germanium) STMicroelectronics yn integreiddio rhannau RF, analog a digidol ar un sglodyn, a all leihau nifer y cydrannau allanol yn sylweddol a gwneud y defnydd gorau o bŵer.

6. BCD

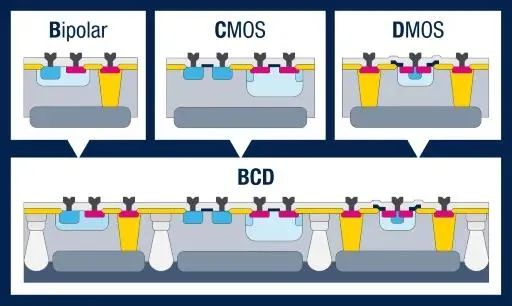

Deubegwn-CMOS-DMOS, gall y dechnoleg hon wneud dyfeisiau deubegwn, CMOS a DMOS ar yr un sglodyn, a elwir yn broses BCD, a ddatblygwyd yn llwyddiannus gyntaf gan STMicroelectronics (ST) ym 1986.

Mae deubegwn yn addas ar gyfer cylchedau analog, mae CMOS yn addas ar gyfer cylchedau digidol a rhesymeg, ac mae DMOS yn addas ar gyfer dyfeisiau pŵer a foltedd uchel. Mae BCD yn cyfuno manteision y tri. Ar ôl gwelliant parhaus, defnyddir BCD yn eang mewn cynhyrchion ym meysydd rheoli pŵer, caffael data analog a actiwadyddion pŵer. Yn ôl gwefan swyddogol ST, mae'r broses aeddfed ar gyfer BCD yn dal i fod tua 100nm, mae 90nm yn dal i fod mewn dyluniad prototeip, ac mae technoleg 40nmbCD yn perthyn i'w gynhyrchion cenhedlaeth nesaf sy'n cael eu datblygu.

Amser postio: Medi-10-2024