A ostiyakinahanglan nga moagi sa tulo ka mga pagbag-o aron mahimong usa ka tinuod nga semiconductor chip: una, ang block-shaped ingot giputol ngadto sa mga manipis; sa ikaduhang proseso, ang mga transistor gikulit sa atubangan sa wafer pinaagi sa miaging proseso; katapusan, packaging gihimo, nga mao, pinaagi sa cutting proseso, angostiyanahimong kompleto nga semiconductor chip. Makita nga ang proseso sa pagputos nahisakop sa proseso sa back-end. Niini nga proseso, ang wafer pagaputlon ngadto sa daghang mga hexahedron nga indibidwal nga mga chip. Kini nga proseso sa pagkuha og independent chips gitawag nga "Singulation", ug ang proseso sa paggabas sa wafer board ngadto sa independent cuboids gitawag nga "wafer cutting (Die Sawing)". Bag-ohay lang, uban sa pagpalambo sa semiconductor integration, ang gibag-on samga ostiyanahimo nga nipis ug nipis, nga siyempre nagdala og daghang kalisud sa proseso sa "singulation".

Ang ebolusyon sa wafer dicing

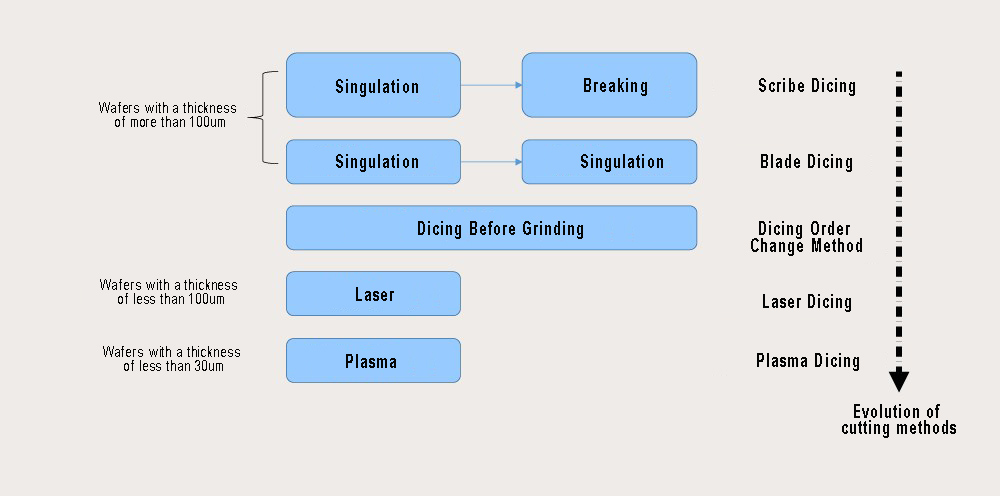

Ang mga proseso sa front-end ug back-end nag-uswag pinaagi sa interaksyon sa lainlaing mga paagi: ang ebolusyon sa mga proseso sa back-end makatino sa istruktura ug posisyon sa hexahedron nga gagmay nga mga chip nga nahimulag gikan sa die saostiya, ingon man ang istruktura ug posisyon sa mga pad (mga agianan sa koneksyon sa kuryente) sa wafer; sa sukwahi, ang ebolusyon sa front-end nga mga proseso nakapausab sa proseso ug pamaagi saostiyapagpanipis sa likod ug "die dicing" sa proseso sa back-end. Busa, ang labi ka sopistikado nga hitsura sa pakete adunay daghang epekto sa proseso sa back-end. Dugang pa, ang numero, pamaagi ug tipo sa dicing mausab usab sumala sa pagbag-o sa hitsura sa pakete.

Screber Dicing

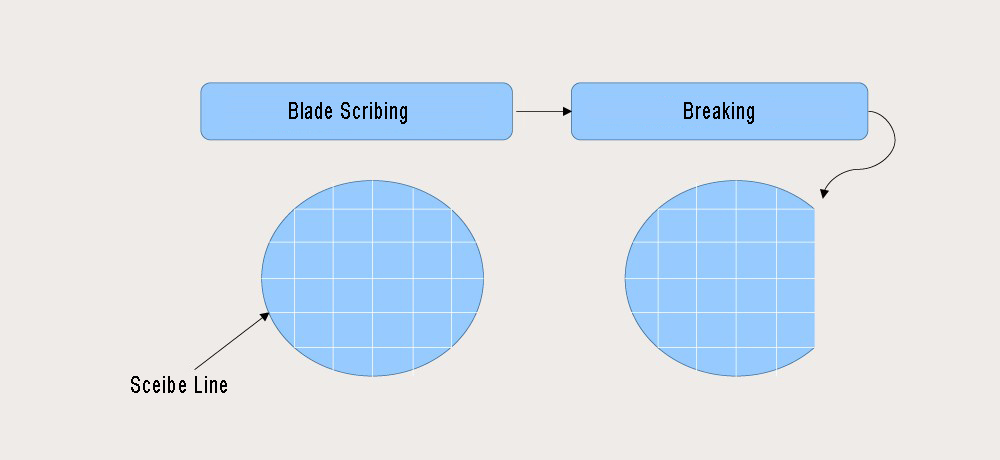

Sa unang mga adlaw, ang "pagbungkag" pinaagi sa paggamit sa eksternal nga pwersa mao lamang ang paagi sa dicing nga makabahin saostiyangadto sa hexahedron mamatay. Bisan pa, kini nga pamaagi adunay mga disbentaha sa pag-chipping o pag-crack sa ngilit sa gamay nga chip. Dugang pa, tungod kay ang mga burr sa metal nga nawong dili hingpit nga makuha, ang giputol nga nawong usab kaayo bagis.

Aron masulbad kini nga problema, ang pamaagi sa pagputol sa "Scribing" nahimo, nga mao, sa wala pa "pagbungkag", ang nawong saostiyagiputol sa halos katunga sa giladmon. Ang "pagsulat", ingon sa gisugyot sa ngalan, nagtumong sa paggamit sa usa ka impeller aron makita (katunga nga giputol) ang atubangan nga bahin sa wafer nga abante. Sa unang mga adlaw, kadaghanan sa mga manipis nga ubos sa 6 ka pulgada migamit niini nga paagi sa pagputol sa una nga "pagputol" tali sa mga chips ug dayon "pagbungkag".

Blade Dicing o Blade Sawing

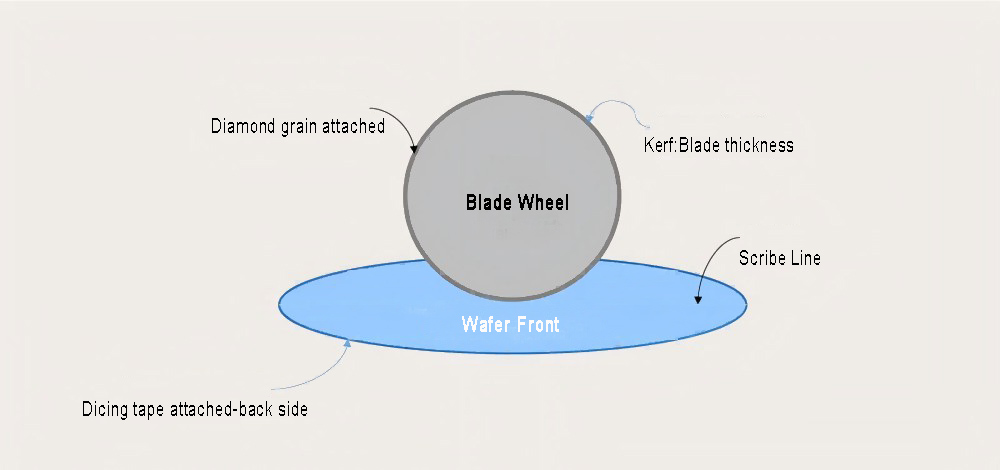

Ang "Scribing" cutting method anam-anam nga naugmad ngadto sa "Blade dicing" cutting (o sawing) nga pamaagi, nga usa ka paagi sa pagputol gamit ang blade duha o tulo ka beses sa usa ka laray. Ang "Blade" nga pamaagi sa pagputol mahimo’g makabawi sa panghitabo sa gagmay nga mga chips nga nagpanit kung "nabuak" pagkahuman sa "pagsulat", ug makapanalipod sa gagmay nga mga chips sa panahon sa proseso sa "singulation". Ang pagputol sa "blade" lahi sa nauna nga pagputol sa "dicing", nga mao, pagkahuman sa pagputol sa "blade", dili kini "pagguba", apan pagputol pag-usab gamit ang usa ka blade. Busa, gitawag usab kini nga "step dicing" nga pamaagi.

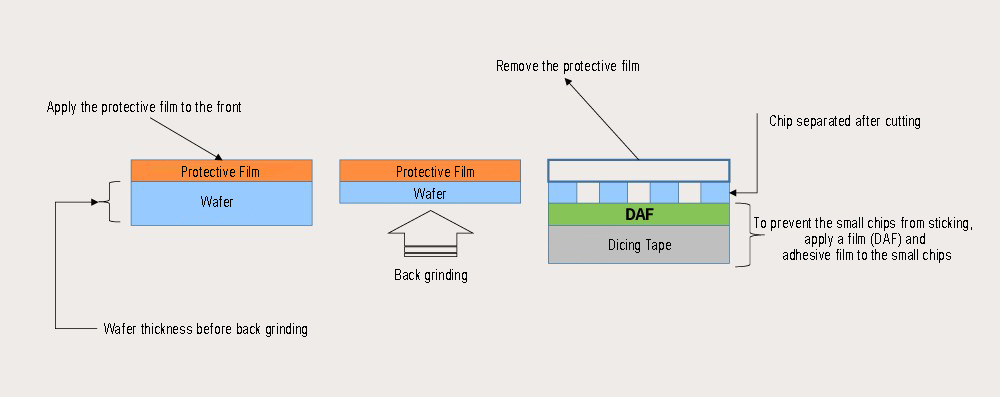

Aron mapanalipdan ang ostiya gikan sa kadaot sa gawas sa panahon sa proseso sa pagputol, usa ka pelikula ang ipadapat sa wafer daan aron maseguro ang mas luwas nga "singling". Atol sa proseso sa "back grinding", ang pelikula itaod sa atubangan sa wafer. Apan sa kasukwahi, sa pagputol sa "blade", ang pelikula kinahanglan nga gilakip sa likod sa wafer. Atol sa eutectic die bonding (die bonding, pag-ayo sa gibulag nga mga chips sa PCB o fixed frame), ang pelikula nga gilakip sa likod awtomatik nga mahulog. Tungod sa taas nga friction sa panahon sa pagputol, ang tubig sa DI kinahanglan nga i-spray nga padayon gikan sa tanan nga direksyon. Dugang pa, ang impeller kinahanglan nga gilakip sa mga partikulo sa diamante aron ang mga hiwa mas maayo nga maputol. Niining panahona, ang giputol (blade gibag-on: gilapdon sa groove) kinahanglan nga uniporme ug dili molapas sa gilapdon sa dicing groove.

Sa dugay nga panahon, ang paggabas mao ang labing kaylap nga gigamit nga tradisyonal nga pamaagi sa pagputol. Ang pinakadako nga bentaha niini mao nga kini makaputol sa daghang gidaghanon sa mga ostiya sa mubo nga panahon. Bisan pa, kung ang katulin sa pagpakaon sa hiwa labi nga nadugangan, ang posibilidad sa pagpanit sa sulud sa chiplet modaghan. Busa, ang gidaghanon sa mga rotation sa impeller kinahanglan nga kontrolon sa mga 30,000 ka beses kada minuto. Makita nga ang teknolohiya sa proseso sa semiconductor kasagaran usa ka sekreto nga hinayhinay nga natipon pinaagi sa taas nga panahon sa pagtigum ug pagsulay ug kasaypanan (sa sunod nga seksyon sa eutectic bonding, atong hisgutan ang sulod mahitungod sa pagputol ug DAF).

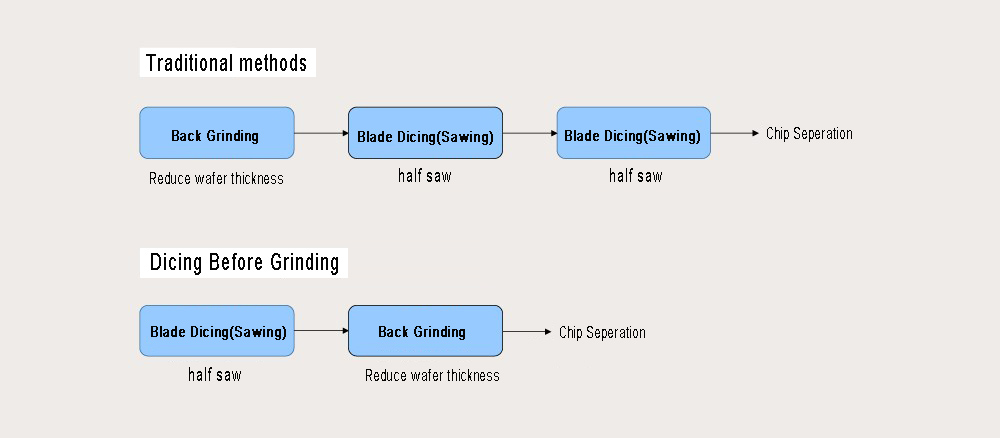

Dicing before grinding (DBG): ang cutting sequence nakapausab sa pamaagi

Kung ang pagputol sa blade gihimo sa usa ka 8-pulgada nga diametro nga wafer, wala’y kinahanglan nga mabalaka bahin sa pagpanit o pag-crack sa sulud sa chiplet. Apan samtang ang diametro sa wafer mosaka ngadto sa 21 ka pulgada ug ang gibag-on nahimong hilabihan ka nipis, ang pagpanit ug pag-crack nga mga panghitabo nagsugod pag-usab. Aron makunhuran pag-ayo ang pisikal nga epekto sa ostiya sa panahon sa proseso sa pagputol, ang pamaagi sa DBG sa "pag-dicing sa wala pa paggaling" gipuli ang tradisyonal nga pagkasunod-sunod sa pagputol. Dili sama sa tradisyonal nga "blade" nga paagi sa pagputol nga padayon nga nagputol, ang DBG una nga naghimo sa usa ka "blade" nga pagputol, ug dayon anam-anam nga gipanipis ang gibag-on nga wafer pinaagi sa padayon nga pagnipis sa likod nga bahin hangtod nga nabahin ang chip. Mahimong giingon nga ang DBG usa ka gi-upgrade nga bersyon sa miaging "blade" nga pamaagi sa pagputol. Tungod kay kini makapakunhod sa epekto sa ikaduha nga pagputol, ang DBG nga pamaagi paspas nga napopular sa "wafer-level packaging".

Laser Dicing

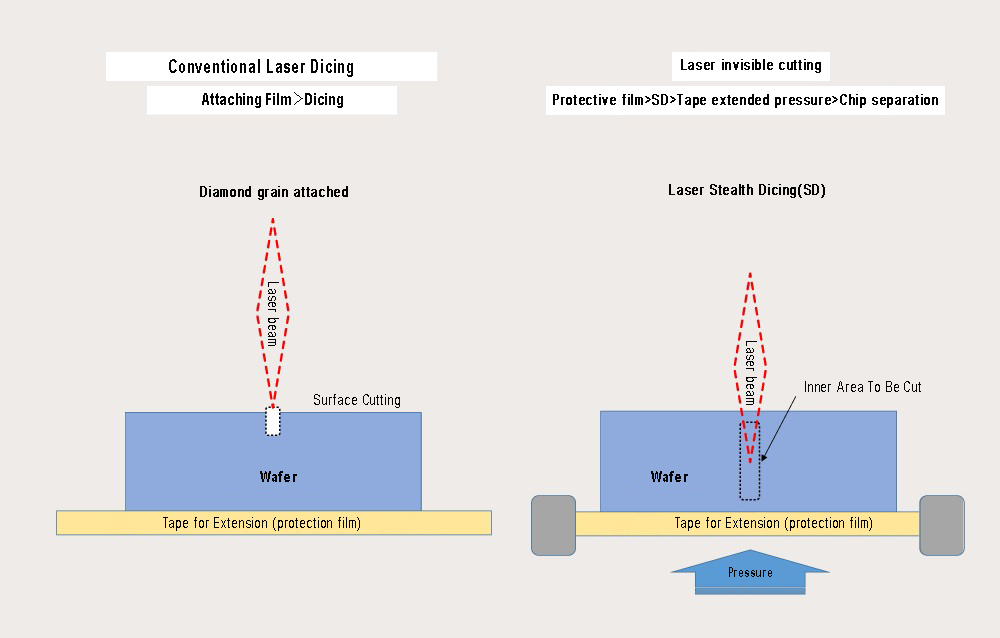

Ang proseso sa wafer-level chip scale package (WLCSP) nag-una naggamit sa pagputol sa laser. Ang pagputol sa laser makapakunhod sa mga panghitabo sama sa pagpanit ug pag-crack, sa ingon makakuha og mas maayo nga kalidad nga mga chips, apan kung ang gibag-on sa wafer labaw pa sa 100μm, ang produktibo mokunhod pag-ayo. Busa, kasagaran kini gigamit sa mga ostiya nga adunay gibag-on nga ubos sa 100μm (medyo nipis). Ang pagputol sa laser nagputol sa silicon pinaagi sa pagpadapat sa high-energy nga laser sa uka sa tigsulat sa wafer. Bisan pa, kung gigamit ang naandan nga pamaagi sa pagputol sa laser (Conventional Laser), usa ka panalipod nga pelikula kinahanglan nga i-apply sa wafer nga abante. Tungod kay ang pagpainit o pag-irradiate sa nawong sa wafer gamit ang laser, kini nga mga pisikal nga kontak maghimo mga grooves sa nawong sa wafer, ug ang mga giputol nga mga tipik sa silicon motapot usab sa nawong. Makita nga ang tradisyonal nga pamaagi sa pagputol sa laser direkta usab nga nagputol sa nawong sa ostiya, ug niining bahina, kini susama sa paagi sa pagputol sa "blade".

Ang Stealth Dicing (SD) usa ka pamaagi sa una nga pagputol sa sulod sa wafer gamit ang enerhiya sa laser, ug dayon pag-apply sa eksternal nga pressure sa tape nga gitaod sa likod aron mabuak kini, sa ingon mabulag ang chip. Kung ang presyur gipadapat sa tape sa likod, ang wafer ipataas dayon pataas tungod sa pag-inat sa tape, sa ingon nagbulag ang chip. Ang mga bentaha sa SD sa tradisyonal nga pamaagi sa pagputol sa laser mao ang: una, walay silicon debris; ikaduha, ang kerf (Kerf: ang gilapdon sa scribe groove) pig-ot, aron mas daghang chips ang makuha. Dugang pa, ang pagpanit ug pag-crack nga panghitabo makunhuran pag-ayo gamit ang SD nga pamaagi, nga hinungdanon sa kinatibuk-ang kalidad sa pagputol. Busa, ang pamaagi sa SD lagmit nga mahimong labing inila nga teknolohiya sa umaabot.

Plasma Dicing

Ang pagputol sa plasma usa ka bag-o nga naugmad nga teknolohiya nga naggamit sa plasma etching aron maputol sa panahon sa proseso sa paghimo (Fab). Ang pagputol sa plasma naggamit sa mga semi-gas nga materyales imbes nga mga likido, mao nga gamay ra ang epekto sa palibot. Ug ang pamaagi sa pagputol sa tibuok nga wafer sa usa ka higayon gisagop, mao nga ang "pagputol" nga gikusgon medyo paspas. Bisan pa, ang pamaagi sa plasma naggamit sa kemikal nga reaksyon nga gas ingon hilaw nga materyal, ug ang proseso sa pag-ukit labi ka komplikado, mao nga ang pag-agos sa proseso niini medyo lisud. Apan kung itandi sa pagputol sa "blade" ug pagputol sa laser, ang pagputol sa plasma dili hinungdan sa kadaot sa wafer nga nawong, sa ingon makunhuran ang rate sa depekto ug makakuha daghang mga chips.

Bag-ohay lang, tungod kay ang gibag-on sa wafer mikunhod ngadto sa 30μm, ug daghang tumbaga (Cu) o ubos nga dielectric nga kanunay nga mga materyales (Low-k) ang gigamit. Busa, aron mapugngan ang mga burr (Burr), ang mga pamaagi sa pagputol sa plasma pabor usab. Siyempre, ang teknolohiya sa pagputol sa plasma kanunay usab nga nag-uswag. Nagtuo ako nga sa umaabot nga umaabot, usa ka adlaw dili kinahanglan nga magsul-ob og espesyal nga maskara kung mag-etching, tungod kay kini usa ka panguna nga direksyon sa pag-uswag sa pagputol sa plasma.

Ingon nga ang gibag-on sa mga wafer padayon nga pagkunhod gikan sa 100μm hangtod sa 50μm ug dayon sa 30μm, ang mga pamaagi sa pagputol alang sa pagkuha sa mga independente nga chips usab nagbag-o ug nag-uswag gikan sa "pagguba" ug "blade" nga pagputol sa pagputol sa laser ug pagputol sa plasma. Bisan kung ang labi ka hamtong nga mga pamaagi sa pagputol nagdugang sa gasto sa produksiyon sa proseso sa pagputol mismo, sa laing bahin, pinaagi sa kamahinungdanon nga pagkunhod sa dili gusto nga mga panghitabo sama sa pagpanit ug pag-crack nga sagad mahitabo sa pagputol sa semiconductor chip ug pagdugang sa gidaghanon sa mga chips nga nakuha matag yunit nga wafer, ang gasto sa produksiyon sa usa ka chip nagpakita sa usa ka ubos nga uso. Siyempre, ang pagtaas sa gidaghanon sa mga chips nga nakuha kada unit area sa wafer suod nga nalangkit sa pagkunhod sa gilapdon sa dicing street. Gamit ang pagputol sa plasma, hapit 20% nga dugang nga mga chip ang makuha kung itandi sa paggamit sa "blade" nga pamaagi sa pagputol, nga usa usab ka hinungdan nga hinungdan ngano nga gipili sa mga tawo ang pagputol sa plasma. Uban sa pag-uswag ug mga pagbag-o sa mga wafer, hitsura sa chip ug mga pamaagi sa pagputos, ang lainlaing mga proseso sa pagputol sama sa teknolohiya sa pagproseso sa wafer ug DBG mitumaw usab.

Oras sa pag-post: Okt-10-2024