This 6 Inch N Type SiC Wafer is engineered for enhanced performance in extreme conditions, making it an ideal choice for applications requiring high power and temperature resistance. Key products associated with this wafer include Si Wafer, SiC Substrate, SOI Wafer, and SiN Substrate. These materials ensure optimal performance in a variety of semiconductor manufacturing processes, enabling devices that are both energy-efficient and durable.

For companies working with Epi Wafer, Gallium Oxide Ga2O3, Cassette, or AlN Wafer, VET Energy’s 6 Inch N Type SiC Wafer provides the necessary foundation for innovative product development. Whether it’s in high-power electronics or the latest in RF technology, these wafers ensure excellent conductivity and minimal thermal resistance, pushing the boundaries of efficiency and performance.

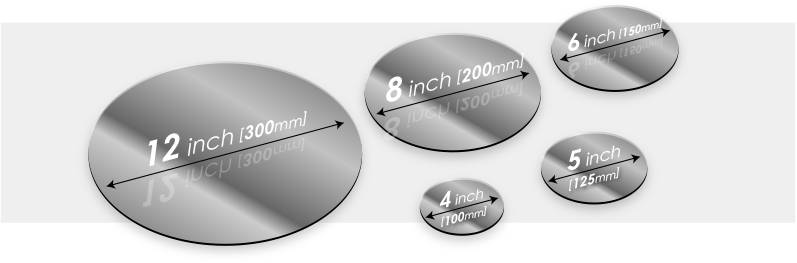

WAFERING SPECIFICATIONS

*n-Pm=n-type Pm-Grade,n-Ps=n-type Ps-Grade,Sl=Semi-lnsulating

|

Item |

8-Inch |

6-Inch |

4-Inch |

||

|

n-P |

n-Pm |

n-Ps |

SI |

SI |

|

|

TTV(GBIR) |

≤6um |

≤6um |

|||

|

Bow(GF3YFCD)-Absolute Value |

≤15μm |

≤15μm |

≤25μm |

≤15μm |

|

|

Warp(GF3YFER) |

≤25μm |

≤25μm |

≤40μm |

≤25μm |

|

|

LTV(SBIR)-10mmx10mm |

<2μm |

||||

|

Wafer Edge |

Beveling |

||||

SURFACE FINISH

*n-Pm=n-type Pm-Grade,n-Ps=n-type Ps-Grade,Sl=Semi-lnsulating

|

Item |

8-Inch |

6-Inch |

4-Inch |

||

|

n-P |

n-Pm |

n-Ps |

SI |

SI |

|

|

Surface Finish |

Double side Optical Polish,Si- Face CMP |

||||

|

SurfaceRoughness |

(10um x 10um) Si-FaceRa≤0.2nm |

(5umx5um) Si-Face Ra≤0.2nm |

|||

|

Edge Chips |

None Permitted (length and width≥0.5mm) |

||||

|

Indents |

None Permitted |

||||

|

Scratches(Si-Face) |

Qty.≤5,Cumulative |

Qty.≤5,Cumulative |

Qty.≤5,Cumulative |

||

|

Cracks |

None Permitted |

||||

|

Edge Exclusion |

3mm |

||||