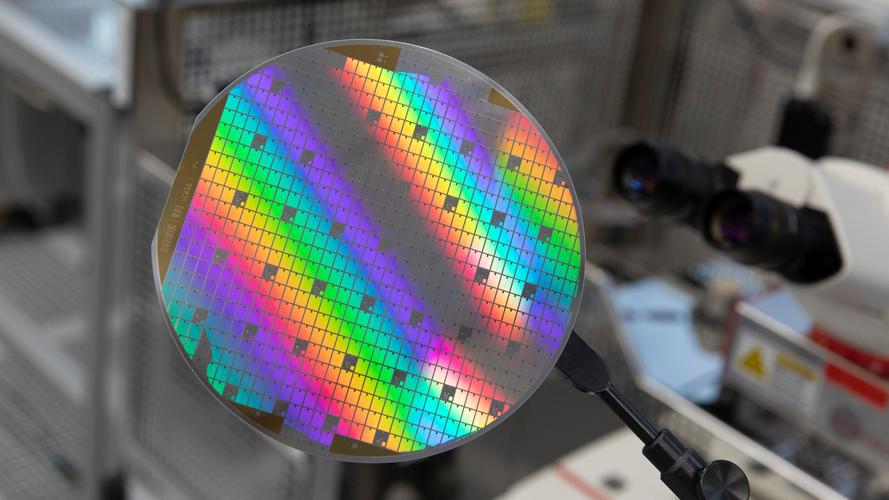

Tấm wafer epitaxial silicon carbide (SiC) của VET Energy là vật liệu bán dẫn có khoảng cách dải rộng hiệu suất cao với khả năng chịu nhiệt độ cao, đặc tính tần số cao và công suất cao tuyệt vời. Đây là chất nền lý tưởng cho thế hệ thiết bị điện tử công suất mới. VET Energy sử dụng công nghệ epitaxial MOCVD tiên tiến để phát triển các lớp epitaxial SiC chất lượng cao trên chất nền SiC, đảm bảo hiệu suất và tính nhất quán tuyệt vời của tấm wafer.

Tấm wafer epitaxial silicon carbide (SiC) của chúng tôi có khả năng tương thích tuyệt vời với nhiều loại vật liệu bán dẫn bao gồm tấm wafer Si, chất nền SiC, tấm wafer SOI và chất nền SiN. Với lớp epitaxial chắc chắn, nó hỗ trợ các quy trình tiên tiến như phát triển và tích hợp tấm wafer Epi với các vật liệu như tấm wafer Gallium Oxide Ga2O3 và tấm wafer AlN, đảm bảo sử dụng linh hoạt trên nhiều công nghệ khác nhau. Được thiết kế để tương thích với các hệ thống xử lý băng cassette tiêu chuẩn công nghiệp, nó đảm bảo hoạt động hiệu quả và hợp lý trong môi trường chế tạo chất bán dẫn.

Dòng sản phẩm của VET Energy không chỉ giới hạn ở wafer epitaxial SiC. Chúng tôi còn cung cấp nhiều loại vật liệu nền bán dẫn, bao gồm wafer Si, chất nền SiC, wafer SOI, chất nền SiN, wafer Epi, v.v. Ngoài ra, chúng tôi cũng đang tích cực phát triển các vật liệu bán dẫn có khoảng cách băng thông rộng mới, chẳng hạn như gallium oxide Ga2O3 và wafer AlN, để đáp ứng nhu cầu về các thiết bị hiệu suất cao hơn trong tương lai của ngành công nghiệp điện tử công suất.

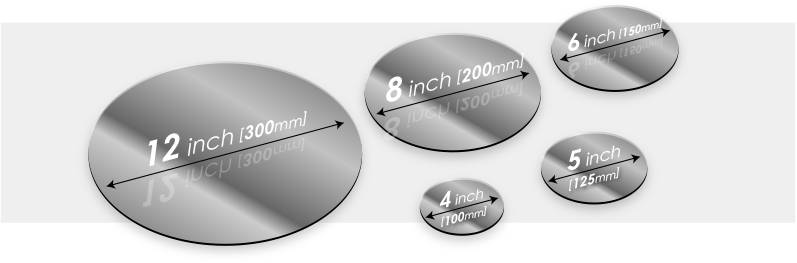

THÔNG SỐ KỸ THUẬT WAFERING

*n-Pm=n-loại Pm-Cấp,n-Ps=n-loại Ps-Cấp,Sl=Bán cách điện

| Mục | 8 inch | 6 inch | 4 inch | ||

| không có | n-Chiều | n-Ps | SI | SI | |

| TTV (GBIR) | ≤6um | ≤6um | |||

| Bow(GF3YFCD)-Giá trị tuyệt đối | ≤15μm | ≤15μm | ≤25μm | ≤15μm | |

| Cong vênh (GF3YFER) | ≤25μm | ≤25μm | ≤40μm | ≤25μm | |

| LTV (SBIR)-10mmx10mm | <2μm | ||||

| Cạnh wafer | Vát mép | ||||

HOÀN THIỆN BỀ MẶT

*n-Pm=n-loại Pm-Cấp,n-Ps=n-loại Ps-Cấp,Sl=Bán cách điện

| Mục | 8 inch | 6 inch | 4 inch | ||

| không có | n-Chiều | n-Ps | SI | SI | |

| Hoàn thiện bề mặt | Đánh bóng quang học hai mặt, Si- Face CMP | ||||

| Độ nhám bề mặt | (10um x 10um) Si-FaceRa≤0.2nm | (5umx5um) Si-Face Ra≤0.2nm | |||

| Chip cạnh | Không được phép (chiều dài và chiều rộng ≥0,5mm) | ||||

| thụt lề | Không được phép | ||||

| Trầy xước (Si-Face) | Số lượng ≤5,Tích lũy | Số lượng ≤5,Tích lũy | Số lượng ≤5,Tích lũy | ||

| Các vết nứt | Không được phép | ||||

| Loại trừ cạnh | 3mm | ||||

-

Pin nhiên liệu 1000w 24v Bộ pin nhiên liệu hydro cho máy bay không người lái

-

Vật tư tiêu hao cho thiết bị bán dẫn alumina cer...

-

Vòng bi đẩy tẩm nhựa Graphite Plug...

-

Dây thừng sợi carbon/than chì cường độ cao cho Se...

-

Pin nhiên liệu Pemfc 1000w cho UAV Pemfc...

-

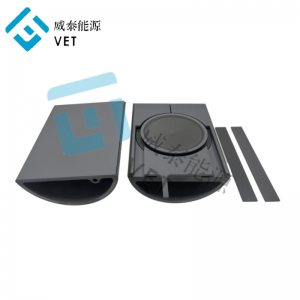

Phần hình bán nguyệt bằng than chì ở trên và dưới cho Si...