Công nghệ cốt lõi cho sự phát triển củaSiC epitaxyVật liệu trước hết là công nghệ kiểm soát khuyết tật, đặc biệt đối với công nghệ kiểm soát khuyết tật dễ bị hỏng thiết bị hoặc suy giảm độ tin cậy. Nghiên cứu cơ chế khuyết tật nền mở rộng vào lớp epitaxial trong quá trình phát triển epitaxial, các quy luật truyền và biến đổi khuyết tật tại giao diện giữa nền và lớp epitaxial, và cơ chế hình thành khuyết tật là cơ sở để làm rõ mối tương quan giữa khuyết tật nền và khuyết tật cấu trúc epitaxial, có thể hướng dẫn hiệu quả sàng lọc nền và tối ưu hóa quy trình epitaxial.

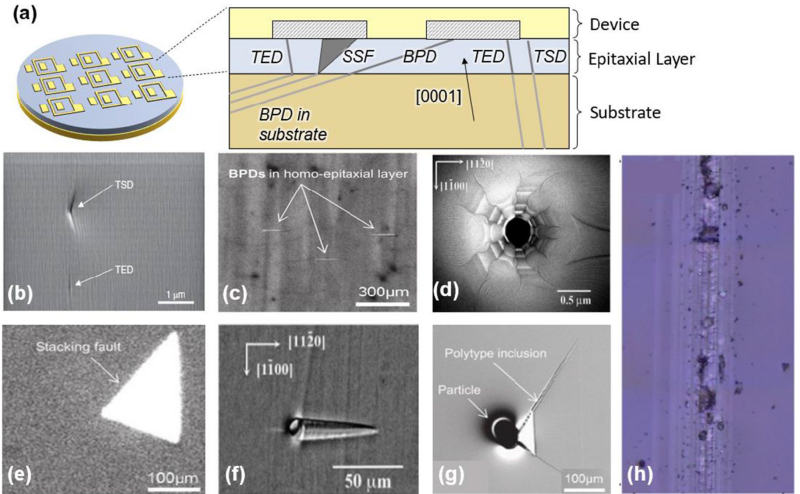

Những khiếm khuyết củalớp epitaxy silicon carbidechủ yếu được chia thành hai loại: khuyết tật tinh thể và khuyết tật hình thái bề mặt. Các khuyết tật tinh thể, bao gồm khuyết tật điểm, trật khớp vít, khuyết tật vi ống, trật khớp cạnh, v.v., chủ yếu bắt nguồn từ các khuyết tật trên nền SiC và khuếch tán vào lớp epitaxial. Các khuyết tật hình thái bề mặt có thể được quan sát trực tiếp bằng mắt thường khi sử dụng kính hiển vi và có các đặc điểm hình thái điển hình. Các khuyết tật hình thái bề mặt chủ yếu bao gồm: Vết xước, khuyết tật hình tam giác, khuyết tật hình cà rốt, sụp đổ và hạt, như thể hiện trong Hình 4. Trong quá trình epitaxial, các hạt lạ, khuyết tật nền, hư hỏng bề mặt và độ lệch quá trình epitaxial đều có thể ảnh hưởng đến chế độ tăng trưởng dòng chảy bậc cục bộ, dẫn đến các khuyết tật hình thái bề mặt.

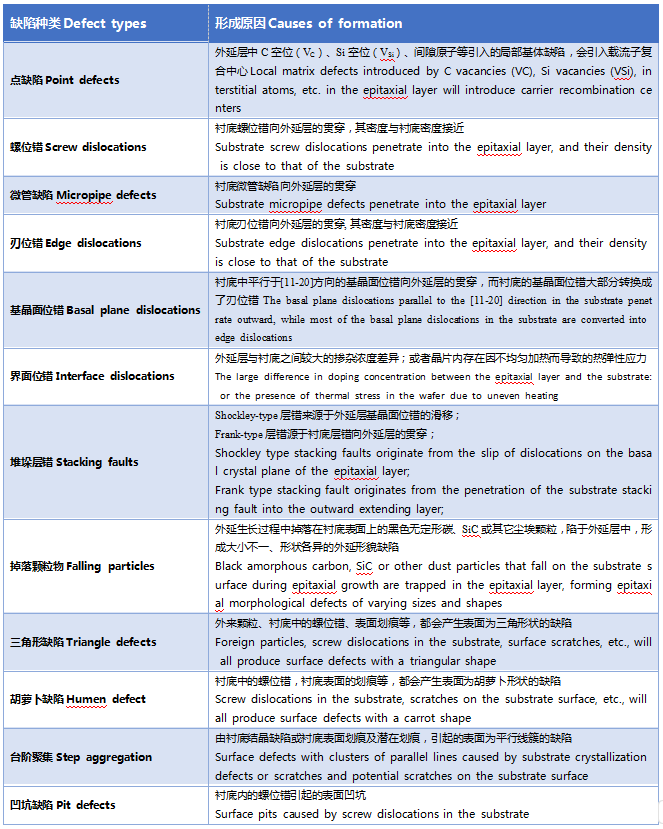

Bảng 1. Nguyên nhân hình thành các khuyết tật ma trận phổ biến và khuyết tật hình thái bề mặt trong các lớp epitaxial SiC

Điểm khuyết

Khuyết điểm điểm được hình thành bởi các chỗ trống hoặc khoảng trống tại một điểm mạng đơn lẻ hoặc nhiều điểm mạng, và chúng không có sự mở rộng về mặt không gian. Khuyết điểm điểm có thể xảy ra trong mọi quy trình sản xuất, đặc biệt là trong quá trình cấy ion. Tuy nhiên, chúng rất khó phát hiện và mối quan hệ giữa sự biến đổi của khuyết điểm điểm và các khuyết điểm khác cũng khá phức tạp.

Ống vi mô (MP)

Micropipes là các vị trí trục vít rỗng lan truyền dọc theo trục tăng trưởng, với vectơ Burgers <0001>. Đường kính của microtube dao động từ một phần nhỏ của micron đến hàng chục micron. Microtube cho thấy các đặc điểm bề mặt giống như hố lớn trên bề mặt của các tấm wafer SiC. Thông thường, mật độ của microtube là khoảng 0,1~1cm-2 và tiếp tục giảm trong quá trình giám sát chất lượng sản xuất wafer thương mại.

Trật khớp vít (TSD) và trật khớp cạnh (TED)

Sự sai lệch trong SiC là nguồn chính gây ra sự xuống cấp và hỏng hóc của thiết bị. Cả sự sai lệch vít (TSD) và sự sai lệch cạnh (TED) đều chạy dọc theo trục tăng trưởng, với các vectơ Burgers lần lượt là <0001> và 1/3<11–20>.

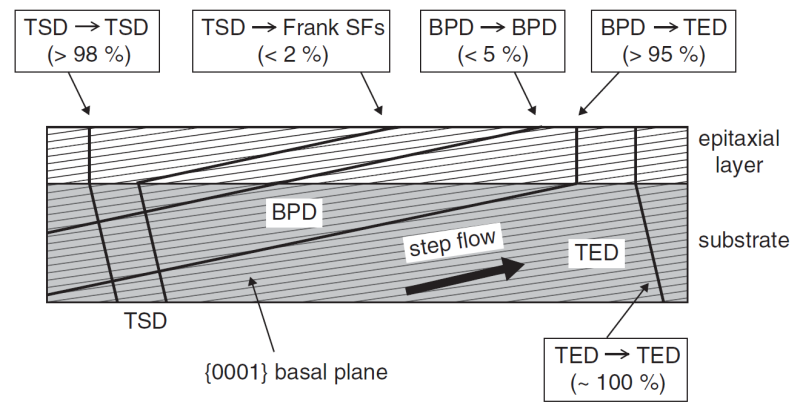

Cả lệch trục vít (TSD) và lệch cạnh (TED) đều có thể kéo dài từ chất nền đến bề mặt wafer và mang lại các đặc điểm bề mặt giống như hố nhỏ (Hình 4b). Thông thường, mật độ lệch cạnh gấp khoảng 10 lần so với lệch trục vít. Lệch trục vít mở rộng, tức là kéo dài từ chất nền đến lớp biểu bì, cũng có thể biến đổi thành các khuyết tật khác và lan truyền dọc theo trục tăng trưởng. TrongSiC epitaxytăng trưởng, các sai lệch vít được chuyển đổi thành các lỗi xếp chồng (SF) hoặc khuyết tật cà rốt, trong khi các sai lệch cạnh trong lớp biểu bì được chứng minh là được chuyển đổi từ các sai lệch mặt phẳng đáy (BPD) được thừa hưởng từ chất nền trong quá trình tăng trưởng biểu bì.

Sự lệch mặt phẳng cơ bản (BPD)

Nằm trên mặt phẳng cơ sở SiC, với vectơ Burgers là 1/3 <11–20>. BPD hiếm khi xuất hiện trên bề mặt của các tấm wafer SiC. Chúng thường tập trung trên chất nền với mật độ 1500 cm-2, trong khi mật độ của chúng trong lớp biểu bì chỉ khoảng 10 cm-2. Phát hiện BPD bằng phát quang quang (PL) cho thấy các đặc điểm tuyến tính, như thể hiện trong Hình 4c. TrongSiC epitaxytăng trưởng, BPD mở rộng có thể được chuyển đổi thành đứt gãy xếp chồng (SF) hoặc trật khớp cạnh (TED).

Lỗi xếp chồng (SF)

Các khiếm khuyết trong trình tự xếp chồng của mặt phẳng cơ sở SiC. Các đứt gãy xếp chồng có thể xuất hiện trong lớp epitaxial bằng cách kế thừa SF trong chất nền, hoặc liên quan đến sự mở rộng và biến đổi của các sai lệch mặt phẳng cơ sở (BPD) và các sai lệch vít ren (TSD). Nhìn chung, mật độ của SF nhỏ hơn 1 cm-2 và chúng thể hiện một đặc điểm hình tam giác khi được phát hiện bằng PL, như thể hiện trong Hình 4e. Tuy nhiên, nhiều loại đứt gãy xếp chồng có thể được hình thành trong SiC, chẳng hạn như loại Shockley và loại Frank, vì ngay cả một lượng nhỏ rối loạn năng lượng xếp chồng giữa các mặt phẳng cũng có thể dẫn đến sự bất thường đáng kể trong trình tự xếp chồng.

Sự sụp đổ

Lỗi rơi vỡ chủ yếu xuất phát từ hiện tượng hạt rơi xuống thành trên và thành bên của buồng phản ứng trong quá trình phát triển, có thể tối ưu hóa bằng cách tối ưu hóa quy trình bảo dưỡng định kỳ vật tư tiêu hao than chì của buồng phản ứng.

Khuyết tật hình tam giác

Đây là tạp chất polytype 3C-SiC kéo dài đến bề mặt của lớp biểu bì SiC theo hướng mặt phẳng cơ sở, như thể hiện trong Hình 4g. Nó có thể được tạo ra bởi các hạt rơi trên bề mặt của lớp biểu bì SiC trong quá trình phát triển epitaxial. Các hạt được nhúng trong lớp biểu bì và cản trở quá trình phát triển, tạo ra các tạp chất polytype 3C-SiC, cho thấy các đặc điểm bề mặt hình tam giác góc nhọn với các hạt nằm ở các đỉnh của vùng tam giác. Nhiều nghiên cứu cũng cho rằng nguồn gốc của các tạp chất polytype là do các vết xước bề mặt, các ống siêu nhỏ và các thông số không phù hợp của quá trình phát triển.

khuyết tật cà rốt

Khuyết tật cà rốt là một phức hợp đứt gãy xếp chồng với hai đầu nằm ở mặt phẳng tinh thể cơ sở TSD và SF, kết thúc bằng một sai lệch kiểu Frank, và kích thước của khuyết tật cà rốt liên quan đến đứt gãy xếp chồng hình lăng trụ. Sự kết hợp của các đặc điểm này tạo thành hình thái bề mặt của khuyết tật cà rốt, trông giống như hình củ cà rốt với mật độ nhỏ hơn 1 cm-2, như thể hiện trong Hình 4f. Các khuyết tật cà rốt dễ hình thành tại các vết xước đánh bóng, TSD hoặc các khuyết tật nền.

Vết xước

Vết xước là hư hỏng cơ học trên bề mặt của các tấm wafer SiC hình thành trong quá trình sản xuất, như thể hiện trong Hình 4h. Các vết xước trên chất nền SiC có thể cản trở sự phát triển của lớp biểu bì, tạo ra một hàng các vị trí sai lệch mật độ cao bên trong lớp biểu bì hoặc các vết xước có thể trở thành cơ sở cho sự hình thành các khuyết tật hình cà rốt. Do đó, việc đánh bóng đúng cách các tấm wafer SiC là rất quan trọng vì những vết xước này có thể ảnh hưởng đáng kể đến hiệu suất của thiết bị khi chúng xuất hiện ở vùng hoạt động của thiết bị.

Các khiếm khuyết hình thái bề mặt khác

Sự tập hợp từng bước là một khuyết tật bề mặt được hình thành trong quá trình phát triển epitaxial SiC, tạo ra các hình tam giác tù hoặc các đặc điểm hình thang trên bề mặt của lớp epilayer SiC. Có nhiều khuyết tật bề mặt khác, chẳng hạn như các hố bề mặt, vết lồi và vết bẩn. Những khuyết tật này thường do các quá trình phát triển không được tối ưu hóa và việc loại bỏ không hoàn toàn hư hỏng do đánh bóng, ảnh hưởng xấu đến hiệu suất của thiết bị.

Thời gian đăng: 05-06-2024