2 Kết quả thực nghiệm và thảo luận

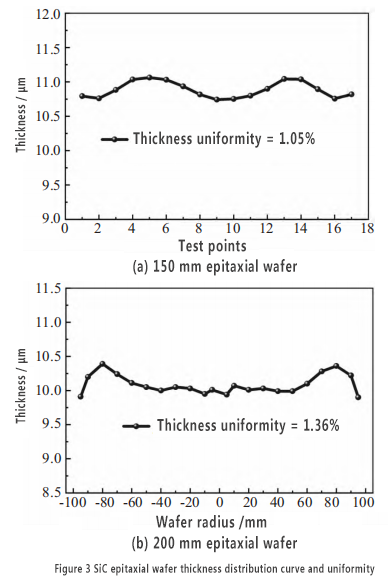

2.1Lớp epitaxyđộ dày và tính đồng nhất

Độ dày lớp epitaxial, nồng độ pha tạp và tính đồng nhất là một trong những chỉ số cốt lõi để đánh giá chất lượng của wafer epitaxial. Độ dày có thể kiểm soát chính xác, nồng độ pha tạp và tính đồng nhất trong wafer là chìa khóa để đảm bảo hiệu suất và tính nhất quán củaThiết bị nguồn SiCvà độ dày lớp epitaxial và độ đồng đều nồng độ pha tạp cũng là những cơ sở quan trọng để đo khả năng xử lý của thiết bị epitaxial.

Hình 3 cho thấy độ đồng đều về độ dày và đường cong phân bố của 150 mm và 200 mmTấm wafer epitaxial SiC. Có thể thấy từ hình vẽ rằng đường cong phân bố độ dày lớp epitaxial đối xứng quanh điểm chính giữa của wafer. Thời gian xử lý epitaxial là 600 giây, độ dày lớp epitaxial trung bình của wafer epitaxial 150mm là 10,89 um và độ đồng đều độ dày là 1,05%. Theo tính toán, tốc độ tăng trưởng epitaxial là 65,3 um/h, đây là mức độ xử lý epitaxial nhanh điển hình. Trong cùng thời gian xử lý epitaxial, độ dày lớp epitaxial của wafer epitaxial 200mm là 10,10 um, độ đồng đều độ dày nằm trong khoảng 1,36% và tốc độ tăng trưởng chung là 60,60 um/h, thấp hơn một chút so với tốc độ tăng trưởng epitaxial 150mm. Điều này là do có sự mất mát rõ ràng trên đường đi khi nguồn silicon và nguồn carbon chảy từ thượng nguồn của buồng phản ứng qua bề mặt wafer đến hạ nguồn của buồng phản ứng và diện tích wafer 200 mm lớn hơn 150 mm. Khí chảy qua bề mặt của wafer 200 mm trong một khoảng cách dài hơn và khí nguồn tiêu thụ trên đường đi nhiều hơn. Trong điều kiện wafer tiếp tục quay, độ dày tổng thể của lớp epitaxial mỏng hơn, do đó tốc độ tăng trưởng chậm hơn. Nhìn chung, độ đồng đều về độ dày của wafer epitaxial 150 mm và 200 mm là tuyệt vời và khả năng xử lý của thiết bị có thể đáp ứng các yêu cầu của các thiết bị chất lượng cao.

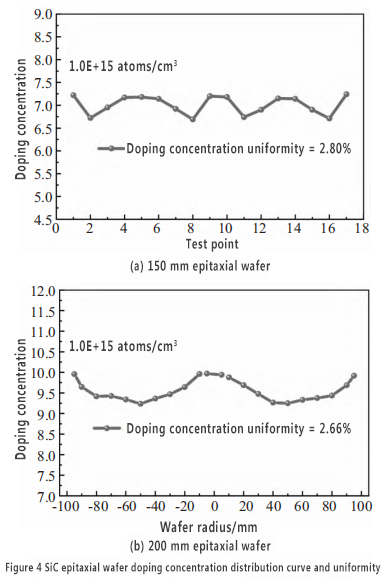

2.2 Nồng độ pha tạp lớp epitaxial và độ đồng đều

Hình 4 cho thấy sự đồng đều nồng độ pha tạp và phân bố đường cong của 150 mm và 200 mmTấm wafer epitaxial SiC. Như có thể thấy từ hình, đường cong phân bố nồng độ trên tấm epitaxial có tính đối xứng rõ ràng so với tâm của tấm wafer. Độ đồng đều nồng độ pha tạp của các lớp epitaxial 150 mm và 200 mm lần lượt là 2,80% và 2,66%, có thể kiểm soát trong phạm vi 3%, đây là mức tuyệt vời đối với các thiết bị quốc tế tương tự. Đường cong nồng độ pha tạp của lớp epitaxial được phân bố theo hình chữ "W" theo hướng đường kính, chủ yếu được xác định bởi trường dòng chảy của lò epitaxial tường nóng nằm ngang, vì hướng luồng khí của lò tăng trưởng epitaxial luồng khí nằm ngang là từ đầu vào không khí (ngược dòng) và chảy ra từ đầu hạ lưu theo kiểu tầng qua bề mặt wafer; do tốc độ "cạn kiệt dọc đường" của nguồn cacbon (C2H4) cao hơn tốc độ của nguồn silic (TCS), khi wafer quay, C/Si thực tế trên bề mặt wafer giảm dần từ rìa vào tâm (nguồn cacbon ở tâm ít hơn), theo "lý thuyết vị trí cạnh tranh" của C và N, nồng độ pha tạp ở tâm wafer giảm dần về phía rìa, để đạt được độ đồng đều nồng độ tuyệt vời, cạnh N2 được thêm vào như một sự bù trừ trong quá trình epitaxial để làm chậm quá trình giảm nồng độ pha tạp từ tâm ra rìa, do đó đường cong nồng độ pha tạp cuối cùng có hình chữ "W".

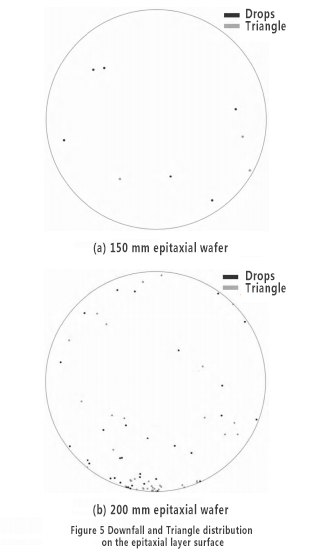

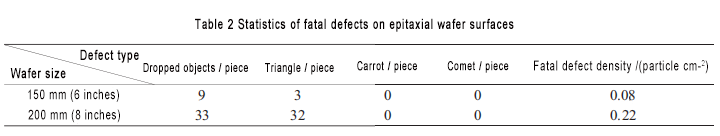

2.3 Các khuyết tật lớp epitaxial

Ngoài độ dày và nồng độ pha tạp, mức độ kiểm soát khuyết tật lớp epitaxial cũng là một thông số cốt lõi để đo chất lượng của wafer epitaxial và là một chỉ số quan trọng về khả năng xử lý của thiết bị epitaxial. Mặc dù SBD và MOSFET có các yêu cầu khác nhau về khuyết tật, nhưng các khuyết tật hình thái bề mặt rõ ràng hơn như khuyết tật giọt, khuyết tật tam giác, khuyết tật cà rốt, khuyết tật sao chổi, v.v. được định nghĩa là khuyết tật chết người của các thiết bị SBD và MOSFET. Xác suất hỏng hóc của các chip chứa các khuyết tật này là cao, vì vậy việc kiểm soát số lượng khuyết tật chết người là cực kỳ quan trọng để cải thiện năng suất chip và giảm chi phí. Hình 5 cho thấy sự phân bố các khuyết tật chết người của wafer epitaxial SiC 150 mm và 200 mm. Trong điều kiện không có sự mất cân bằng rõ ràng trong tỷ lệ C/Si, các khuyết tật cà rốt và khuyết tật sao chổi về cơ bản có thể được loại bỏ, trong khi các khuyết tật giọt và khuyết tật tam giác liên quan đến việc kiểm soát độ sạch trong quá trình vận hành thiết bị epitaxial, mức độ tạp chất của các bộ phận than chì trong buồng phản ứng và chất lượng của chất nền. Từ Bảng 2, có thể thấy rằng mật độ khuyết tật chết người của wafer epitaxial 150 mm và 200 mm có thể được kiểm soát trong phạm vi 0,3 hạt/cm2, đây là mức tuyệt vời cho cùng một loại thiết bị. Mức kiểm soát mật độ khuyết tật chết người của wafer epitaxial 150 mm tốt hơn wafer epitaxial 200 mm. Điều này là do quy trình chuẩn bị chất nền của 150 mm trưởng thành hơn so với 200 mm, chất lượng chất nền tốt hơn và mức kiểm soát tạp chất của buồng phản ứng graphite 150 mm tốt hơn.

2.4 Độ nhám bề mặt wafer epitaxial

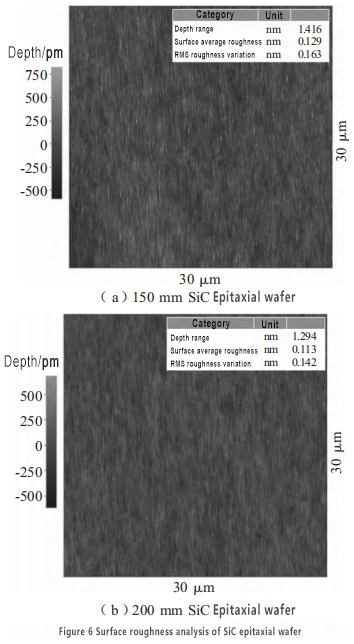

Hình 6 cho thấy hình ảnh AFM của bề mặt của các tấm epitaxial SiC 150 mm và 200 mm. Có thể thấy từ hình ảnh rằng độ nhám bình phương trung bình gốc bề mặt Ra của các tấm epitaxial 150 mm và 200 mm lần lượt là 0,129 nm và 0,113 nm, và bề mặt của lớp epitaxial nhẵn mà không có hiện tượng kết tụ bậc vĩ mô rõ ràng. Hiện tượng này cho thấy sự phát triển của lớp epitaxial luôn duy trì chế độ phát triển dòng chảy bậc trong toàn bộ quá trình epitaxial và không xảy ra hiện tượng kết tụ bậc. Có thể thấy rằng bằng cách sử dụng quá trình phát triển epitaxial được tối ưu hóa, có thể thu được các lớp epitaxial nhẵn trên các đế góc thấp 150 mm và 200 mm.

3 Kết luận

Các tấm wafer epitaxial đồng nhất 4H-SiC 150 mm và 200 mm đã được chế tạo thành công trên các chất nền trong nước bằng cách sử dụng thiết bị tăng trưởng epitaxial SiC 200 mm do chính mình phát triển và quy trình epitaxial đồng nhất phù hợp với 150 mm và 200 mm đã được phát triển. Tốc độ tăng trưởng epitaxial có thể lớn hơn 60 μm/h. Trong khi đáp ứng yêu cầu epitaxy tốc độ cao, chất lượng wafer epitaxial là tuyệt vời. Độ đồng đều về độ dày của các wafer epitaxial SiC 150 mm và 200 mm có thể được kiểm soát trong vòng 1,5%, độ đồng đều về nồng độ nhỏ hơn 3%, mật độ khuyết tật nghiêm trọng nhỏ hơn 0,3 hạt/cm2 và bình phương trung bình độ nhám bề mặt epitaxial Ra nhỏ hơn 0,15 nm. Các chỉ số quy trình cốt lõi của các wafer epitaxial ở cấp độ tiên tiến trong ngành.

Nguồn: Thiết bị đặc biệt của ngành công nghiệp điện tử

Tác giả: Xie Tianle, Li Ping, Yang Yu, Gong Xiaoliang, Ba Sai, Chen Guoqin, Wan Shengqiang

(Viện nghiên cứu số 48 của Tập đoàn công nghệ điện tử Trung Quốc, Trường Sa, Hồ Nam 410111)

Thời gian đăng: 04-09-2024