A ostiyakailangang dumaan sa tatlong pagbabago upang maging isang tunay na semiconductor chip: una, ang hugis-block na ingot ay pinutol sa mga manipis; sa pangalawang proseso, ang mga transistor ay nakaukit sa harap ng wafer sa pamamagitan ng nakaraang proseso; sa wakas, ang packaging ay ginanap, iyon ay, sa pamamagitan ng proseso ng pagputol, angostiyanagiging isang kumpletong semiconductor chip. Makikita na ang proseso ng packaging ay kabilang sa proseso ng back-end. Sa prosesong ito, ang wafer ay hiwain sa ilang mga indibidwal na chip ng hexahedron. Ang prosesong ito ng pagkuha ng mga independiyenteng chips ay tinatawag na "Singulation", at ang proseso ng paglalagari ng wafer board sa mga independiyenteng cuboid ay tinatawag na "wafer cutting (Die Sawing)". Kamakailan lamang, sa pagpapabuti ng semiconductor integration, ang kapal ngmga ostiyaay naging payat at payat, na siyempre ay nagdudulot ng maraming kahirapan sa proseso ng "singulation".

Ang ebolusyon ng wafer dicing

Ang mga proseso sa front-end at back-end ay umunlad sa pamamagitan ng pakikipag-ugnayan sa iba't ibang paraan: ang ebolusyon ng mga back-end na proseso ay maaaring matukoy ang istraktura at posisyon ng hexahedron na maliliit na chip na nakahiwalay mula sa die saostiya, pati na rin ang istraktura at posisyon ng mga pad (mga daanan ng koneksyon sa kuryente) sa wafer; sa kabaligtaran, binago ng ebolusyon ng mga front-end na proseso ang proseso at pamamaraan ngostiyapagnipis ng likod at "die dicing" sa proseso ng back-end. Samakatuwid, ang lalong sopistikadong hitsura ng pakete ay magkakaroon ng malaking epekto sa proseso ng back-end. Bukod dito, ang bilang, pamamaraan at uri ng dicing ay magbabago din ayon sa pagbabago sa hitsura ng pakete.

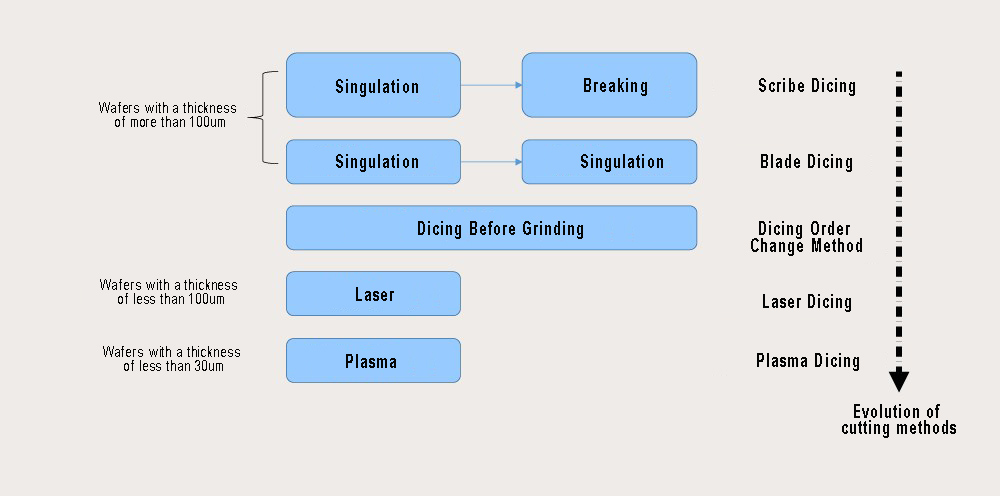

Scribe Dicing

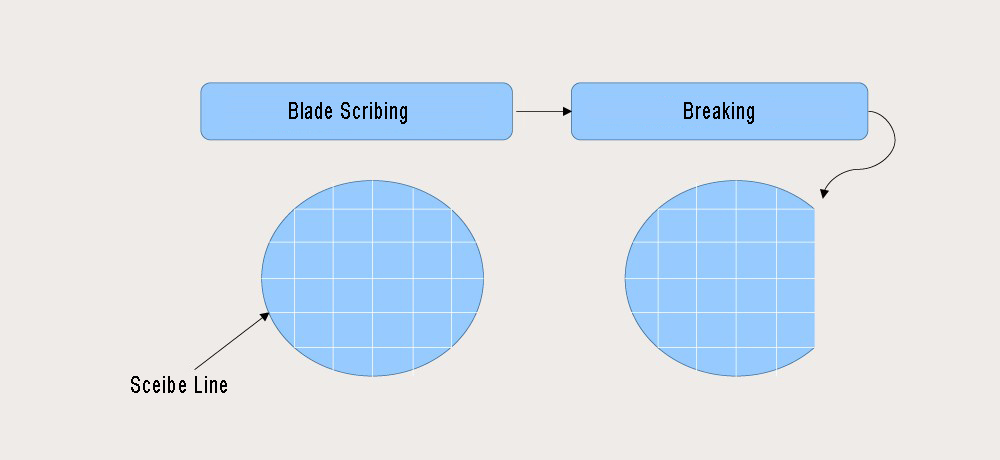

Sa mga unang araw, ang "pagsira" sa pamamagitan ng paggamit ng panlabas na puwersa ay ang tanging paraan ng dicing na maaaring hatiin angostiyasa hexahedron namatay. Gayunpaman, ang pamamaraang ito ay may mga disadvantages ng chipping o pag-crack ng gilid ng maliit na chip. Bilang karagdagan, dahil ang mga burr sa ibabaw ng metal ay hindi ganap na naalis, ang ibabaw ng hiwa ay masyadong magaspang.

Upang malutas ang problemang ito, nabuo ang "Scribing" cutting method, iyon ay, bago ang "pagsira", ang ibabaw ngostiyaay pinutol sa halos kalahati ng lalim. Ang "pagsusulat", gaya ng ipinahihiwatig ng pangalan, ay tumutukoy sa paggamit ng isang impeller upang makita (kalahating hiwa) ang harap na bahagi ng ostiya nang maaga. Noong mga unang araw, karamihan sa mga wafer na wala pang 6 na pulgada ay ginamit ang pamamaraang ito ng pagputol ng unang "paghiwa" sa pagitan ng mga chips at pagkatapos ay "pagsira".

Blade Dicing o Blade Sawing

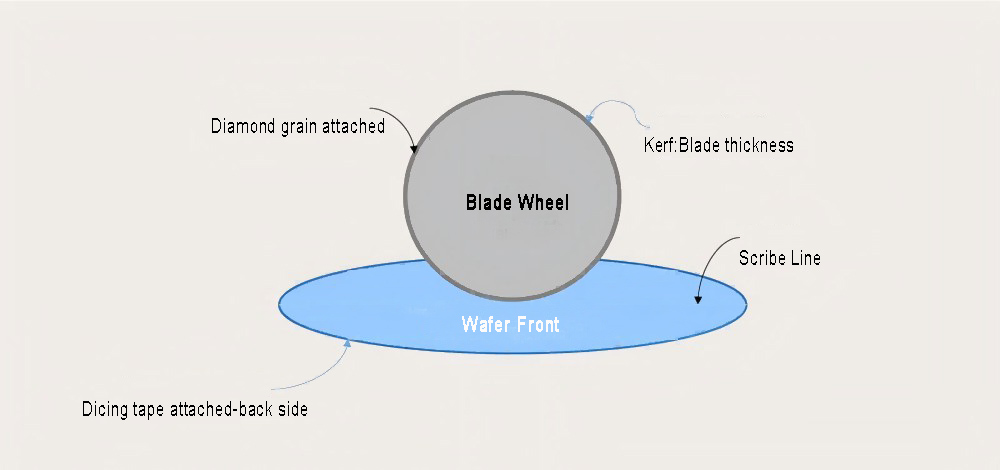

Ang "Scribing" cutting method ay unti-unting nabuo sa "Blade dicing" cutting (o sawing) method, na isang paraan ng pagputol gamit ang blade ng dalawa o tatlong beses na magkasunod. Ang paraan ng pagputol ng "Blade" ay maaaring makabawi para sa hindi pangkaraniwang bagay ng maliliit na chips na pagbabalat kapag "nasira" pagkatapos ng "scribing", at maaaring maprotektahan ang maliliit na chips sa panahon ng proseso ng "singulation". Ang pagputol ng "blade" ay iba mula sa nakaraang pagputol ng "dicing", iyon ay, pagkatapos ng pagputol ng "blade", hindi ito "pagsira", ngunit pagputol muli gamit ang isang talim. Samakatuwid, ito ay tinatawag ding "step dicing" na paraan.

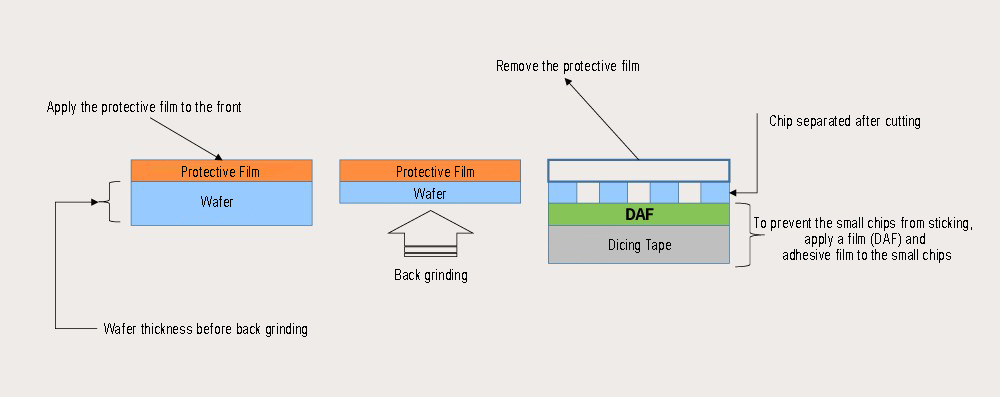

Upang maprotektahan ang ostiya mula sa panlabas na pinsala sa panahon ng proseso ng pagputol, isang pelikula ang ilalapat sa ostiya nang maaga upang matiyak ang mas ligtas na "singling". Sa panahon ng proseso ng "back grinding", ang pelikula ay ikakabit sa harap ng wafer. Ngunit sa kabaligtaran, sa pagputol ng "blade", ang pelikula ay dapat na naka-attach sa likod ng ostiya. Sa panahon ng eutectic die bonding (die bonding, pag-aayos ng mga hiwalay na chips sa PCB o fixed frame), ang film na nakakabit sa likod ay awtomatikong mahuhulog. Dahil sa mataas na alitan sa panahon ng pagputol, ang tubig ng DI ay dapat na patuloy na i-spray mula sa lahat ng direksyon. Bilang karagdagan, ang impeller ay dapat na naka-attach na may mga particle ng brilyante upang ang mga hiwa ay maaaring hiwain nang mas mahusay. Sa oras na ito, ang hiwa (kapal ng talim: lapad ng uka) ay dapat na pare-pareho at hindi dapat lumampas sa lapad ng dicing groove.

Sa loob ng mahabang panahon, ang paglalagari ay ang pinakakaraniwang ginagamit na tradisyonal na paraan ng pagputol. Ang pinakamalaking bentahe nito ay maaari itong mag-cut ng malaking bilang ng mga wafer sa maikling panahon. Gayunpaman, kung ang bilis ng pagpapakain ng slice ay lubos na nadagdagan, ang posibilidad ng pagbabalat sa gilid ng chiplet ay tataas. Samakatuwid, ang bilang ng mga pag-ikot ng impeller ay dapat na kontrolin sa halos 30,000 beses bawat minuto. Makikita na ang teknolohiya ng proseso ng semiconductor ay kadalasang isang lihim na naipon nang dahan-dahan sa pamamagitan ng mahabang panahon ng akumulasyon at pagsubok at pagkakamali (sa susunod na seksyon sa eutectic bonding, tatalakayin natin ang nilalaman tungkol sa pagputol at DAF).

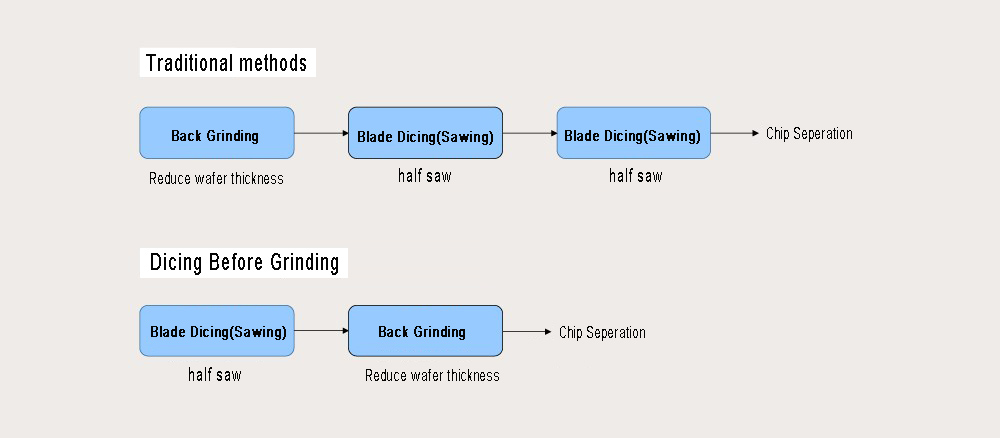

Dicing before grinding (DBG): binago ng cutting sequence ang paraan

Kapag isinagawa ang pagputol ng talim sa isang 8-pulgadang lapad na wafer, hindi na kailangang mag-alala tungkol sa pagbabalat o pag-crack ng gilid ng chiplet. Ngunit habang ang diameter ng wafer ay tumataas sa 21 pulgada at ang kapal ay nagiging lubhang manipis, ang pagbabalat at pag-crack na phenomena ay nagsisimulang lumitaw muli. Upang makabuluhang bawasan ang pisikal na epekto sa ostiya sa panahon ng proseso ng paggupit, ang pamamaraan ng DBG na "pagdidisko bago paggiling" ay pinapalitan ang tradisyonal na pagkakasunud-sunod ng pagputol. Hindi tulad ng tradisyunal na paraan ng pagputol ng "blade" na patuloy na pumuputol, nagsasagawa muna ang DBG ng "blade" cut, at pagkatapos ay unti-unting pinapanipis ang kapal ng wafer sa pamamagitan ng patuloy na pagnipis sa likurang bahagi hanggang sa mahati ang chip. Masasabing ang DBG ay isang na-upgrade na bersyon ng nakaraang "blade" na paraan ng pagputol. Dahil maaari nitong bawasan ang epekto ng pangalawang hiwa, ang paraan ng DBG ay mabilis na pinasikat sa "wafer-level packaging".

Laser Dicing

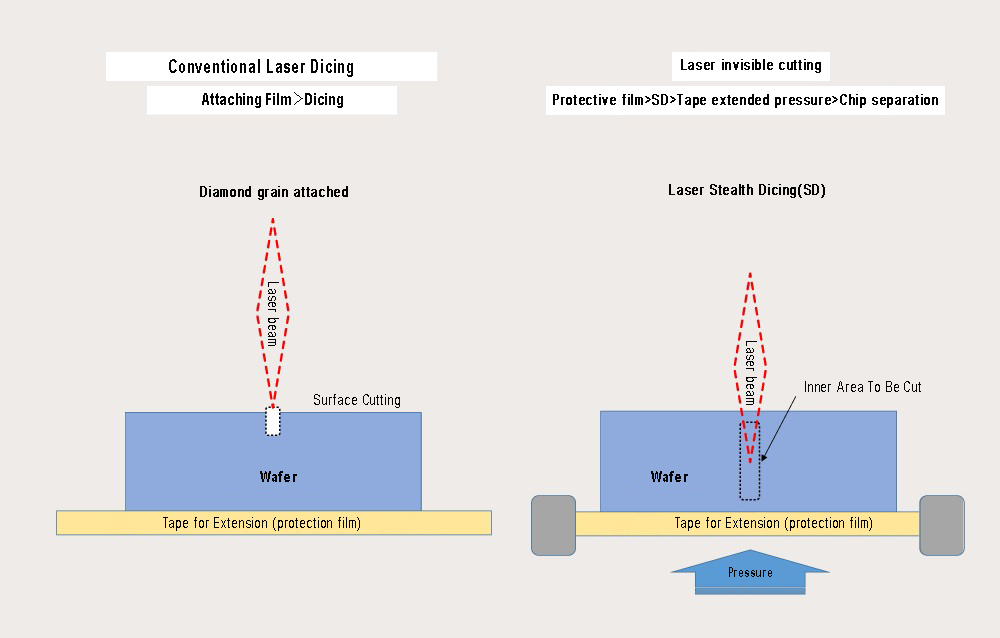

Ang proseso ng wafer-level chip scale package (WLCSP) ay pangunahing gumagamit ng laser cutting. Ang pagputol ng laser ay maaaring mabawasan ang mga phenomena tulad ng pagbabalat at pag-crack, sa gayon ay nakakakuha ng mas mahusay na kalidad ng mga chips, ngunit kapag ang kapal ng wafer ay higit sa 100μm, ang produktibidad ay lubos na mababawasan. Samakatuwid, ito ay kadalasang ginagamit sa mga wafer na may kapal na mas mababa sa 100μm (medyo manipis). Pinutol ng laser cutting ang silicon sa pamamagitan ng paglalagay ng high-energy laser sa scribe groove ng wafer. Gayunpaman, kapag gumagamit ng maginoo na laser (Conventional Laser) na paraan ng pagputol, isang proteksiyon na pelikula ay dapat na ilapat sa ibabaw ng wafer nang maaga. Dahil ang pag-init o pag-irradiate sa ibabaw ng wafer gamit ang laser, ang mga pisikal na contact na ito ay gagawa ng mga grooves sa ibabaw ng wafer, at ang mga cut silicon fragment ay makakadikit din sa ibabaw. Makikita na ang tradisyunal na paraan ng pagputol ng laser ay direktang pinuputol din ang ibabaw ng ostiya, at sa bagay na ito, ito ay katulad ng paraan ng pagputol ng "blade".

Ang Stealth Dicing (SD) ay isang paraan ng paggupit muna sa loob ng wafer gamit ang laser energy, at pagkatapos ay paglalagay ng external pressure sa tape na nakakabit sa likod para masira ito, at sa gayo'y pinaghihiwalay ang chip. Kapag inilapat ang presyon sa tape sa likod, ang wafer ay agad na itataas pataas dahil sa pag-uunat ng tape, sa gayon ay naghihiwalay sa chip. Ang mga bentahe ng SD sa tradisyonal na pamamaraan ng pagputol ng laser ay: una, walang mga labi ng silikon; pangalawa, makitid ang kerf (Kerf: ang lapad ng uka ng tagasulat) kaya mas maraming chips ang makukuha. Bilang karagdagan, ang pagbabalat at pag-crack na kababalaghan ay lubos na mababawasan gamit ang SD method, na mahalaga sa pangkalahatang kalidad ng pagputol. Samakatuwid, ang paraan ng SD ay malamang na maging pinakasikat na teknolohiya sa hinaharap.

Plasma Dicing

Ang plasma cutting ay isang kamakailang binuo na teknolohiya na gumagamit ng plasma etching upang i-cut sa panahon ng proseso ng pagmamanupaktura (Fab). Ang pagputol ng plasma ay gumagamit ng mga semi-gas na materyales sa halip na mga likido, kaya ang epekto sa kapaligiran ay medyo maliit. At ang paraan ng pagputol ng buong wafer sa isang pagkakataon ay pinagtibay, kaya ang bilis ng "pagputol" ay medyo mabilis. Gayunpaman, ang pamamaraan ng plasma ay gumagamit ng kemikal na reaksyon ng gas bilang hilaw na materyal, at ang proseso ng pag-ukit ay napaka-komplikado, kaya ang daloy ng proseso nito ay medyo mahirap. Ngunit kumpara sa pagputol ng "blade" at pagputol ng laser, ang pagputol ng plasma ay hindi nagdudulot ng pinsala sa ibabaw ng wafer, sa gayon ay binabawasan ang rate ng depekto at nakakakuha ng mas maraming chips.

Kamakailan lamang, dahil ang kapal ng wafer ay nabawasan sa 30μm, at maraming tanso (Cu) o mababang dielectric na patuloy na materyales (Low-k) ang ginagamit. Samakatuwid, upang maiwasan ang mga burr (Burr), ang mga pamamaraan ng pagputol ng plasma ay papaboran din. Siyempre, ang teknolohiya ng pagputol ng plasma ay patuloy na umuunlad. Naniniwala ako na sa malapit na hinaharap, isang araw ay hindi na kailangang magsuot ng espesyal na maskara kapag nag-uukit, dahil ito ay isang pangunahing direksyon ng pag-unlad ng pagputol ng plasma.

Dahil ang kapal ng mga wafer ay patuloy na nababawasan mula 100μm hanggang 50μm at pagkatapos ay sa 30μm, ang mga paraan ng pagputol para sa pagkuha ng mga independiyenteng chips ay nagbabago rin at umuunlad mula sa "pagsira" at "blade" na pagputol hanggang sa pagputol ng laser at pagputol ng plasma. Bagama't ang nagiging mature na pamamaraan ng pagputol ay nagpapataas ng gastos sa produksyon ng mismong proseso ng pagputol, sa kabilang banda, sa pamamagitan ng makabuluhang pagbawas sa mga hindi kanais-nais na phenomena tulad ng pagbabalat at pag-crack na kadalasang nangyayari sa pagputol ng semiconductor chip at pagtaas ng bilang ng mga chips na nakuha sa bawat yunit ng wafer, ang halaga ng produksyon ng isang chip ay nagpakita ng isang pababang trend. Siyempre, ang pagtaas sa bilang ng mga chips na nakuha sa bawat unit area ng wafer ay malapit na nauugnay sa pagbawas sa lapad ng dicing street. Gamit ang plasma cutting, halos 20% pang chips ang maaaring makuha kumpara sa paggamit ng "blade" cutting method, na isa ring pangunahing dahilan kung bakit pinipili ng mga tao ang plasma cutting. Sa pagbuo at pagbabago ng mga wafer, hitsura ng chip at mga pamamaraan ng packaging, umuusbong din ang iba't ibang proseso ng pagputol gaya ng teknolohiya sa pagpoproseso ng wafer at DBG.

Oras ng post: Okt-10-2024