A waferစစ်မှန်သော semiconductor ချစ်ပ်တစ်ခုဖြစ်လာရန် အပြောင်းအလဲသုံးခုကို ဖြတ်သန်းရပါမည်- ပထမ၊ တုံးပုံသဏ္ဌာန်ရှိသော ingot ကို wafers များအဖြစ်သို့ဖြတ်ပါ။ ဒုတိယလုပ်ငန်းစဉ်တွင်၊ ယခင်လုပ်ငန်းစဉ်အားဖြင့် wafer ၏အရှေ့ဘက်တွင် ထရန်စစ္စတာများကို ရေးထွင်းထားသည်။ နောက်ဆုံးတွင်၊ ထုပ်ပိုးခြင်းကိုလုပ်ဆောင်သည်၊ ဆိုလိုသည်မှာဖြတ်တောက်ခြင်းလုပ်ငန်းစဉ်အားဖြင့်ဖြစ်သည်။waferပြီးပြည့်စုံသော semiconductor ချစ်ပ်တစ်ခု ဖြစ်လာသည်။ ထုပ်ပိုးခြင်းလုပ်ငန်းစဉ်သည် back-end လုပ်ငန်းစဉ်နှင့်သက်ဆိုင်ကြောင်း ရှုမြင်နိုင်ပါသည်။ ဤလုပ်ငန်းစဉ်တွင်၊ wafer ကို hexahedron တစ်ခုချင်းစီချစ်ပ်များစွာထဲသို့ဖြတ်လိမ့်မည်။ လွတ်လပ်သောချစ်ပ်ပြားများရယူခြင်းလုပ်ငန်းစဉ်ကို "Singulation" ဟုခေါ်ပြီး wafer board ကိုလွတ်လပ်သော cuboid များအဖြစ်သို့လွှချခြင်းလုပ်ငန်းစဉ်ကို "wafer cutting (Die Sawing)" ဟုခေါ်သည်။ မကြာသေးမီက semiconductor ပေါင်းစပ်မှု၏တိုးတက်မှုနှင့်အတူ, ၏အထူwafersပါးလွှာပြီး ပါးလွှာလာသည်၊ ၎င်းသည် "singulation" လုပ်ငန်းစဉ်အတွက် အခက်အခဲများစွာကို ယူဆောင်လာပါသည်။

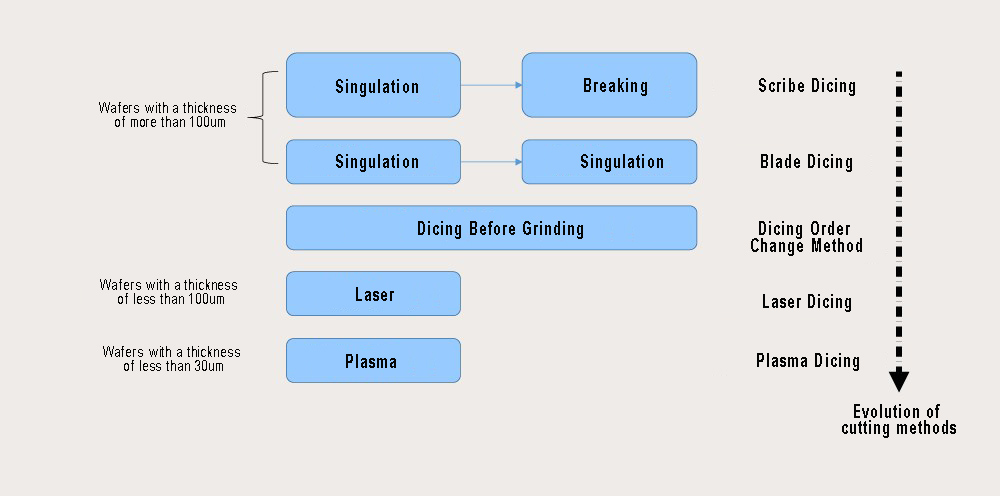

wafer dicing ၏ဆင့်ကဲဖြစ်စဉ်

Front-end နှင့် Back-end လုပ်ငန်းစဉ်များသည် နည်းလမ်းအမျိုးမျိုးဖြင့် အပြန်အလှန်အကျိုးသက်ရောက်မှုများဖြင့် ဆင့်ကဲပြောင်းလဲလာပါသည်- နောက်တန်းလုပ်ငန်းစဉ်များ၏ ဆင့်ကဲပြောင်းလဲမှုသည် အသေခံမှခွဲထုတ်ထားသော hexahedron အသေးစားချစ်ပ်များ၏ဖွဲ့စည်းပုံနှင့် အနေအထားကို ဆုံးဖြတ်ပေးနိုင်ပါသည်။waferwafer ပေါ်ရှိ pads (လျှပ်စစ်ဆက်သွယ်မှုလမ်းကြောင်းများ) ၏ဖွဲ့စည်းပုံနှင့်အနေအထား၊ ဆန့်ကျင်ဘက်တွင်၊ ရှေ့ဆုံးလုပ်ငန်းစဉ်များ၏ ဆင့်ကဲဖြစ်စဉ်သည် လုပ်ငန်းစဉ်နှင့် နည်းလမ်းကို ပြောင်းလဲစေခဲ့သည်။waferback-end လုပ်ငန်းစဉ်တွင် ပါးလွှာခြင်းနှင့် "အစာတုံးခြင်း"။ ထို့ကြောင့်၊ ပက်ကေ့ဂျ်၏ ပိုမိုဆန်းပြားသော အသွင်အပြင်သည် back-end လုပ်ငန်းစဉ်အပေါ် ကြီးမားသော အကျိုးသက်ရောက်မှုရှိမည်ဖြစ်သည်။ ထို့အပြင်၊ အရေအတွက်၊ လုပ်ထုံးလုပ်နည်းနှင့် အန်စာတုံး အမျိုးအစားသည်လည်း ပက်ကေ့ခ်ျ၏ အသွင်အပြင် ပြောင်းလဲမှုအလိုက် ပြောင်းလဲသွားမည်ဖြစ်သည်။

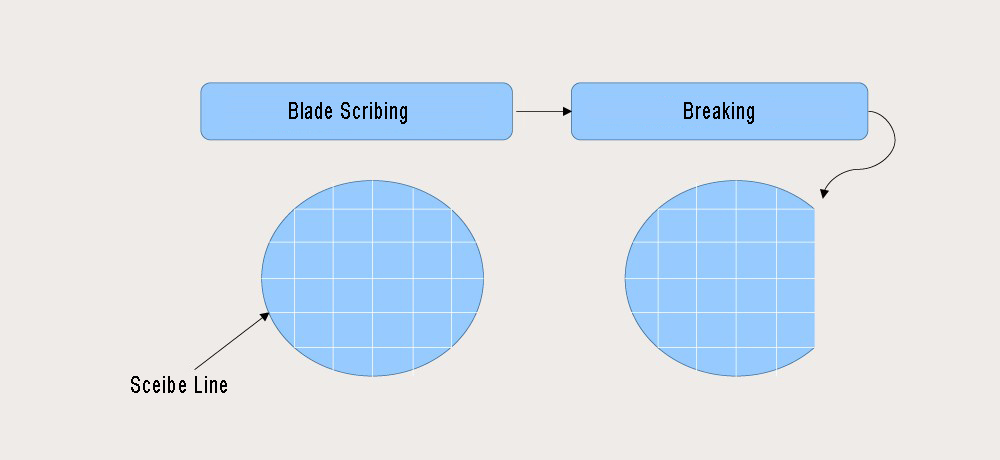

Scribe Dicing

အစောပိုင်းကာလတွင်၊ ပြင်ပအင်အားကိုအသုံးပြုခြင်းဖြင့် "ချိုးဖျက်ခြင်း" သည်၎င်းကိုခွဲခြမ်းပေးနိုင်သည့်တစ်ခုတည်းသောအတုံးလိုက်နည်းလမ်းဖြစ်သည်။waferhexahedron ထဲသို့သေသွားသည်။ သို့သော်၊ ဤနည်းလမ်းသည် ချစ်ပ်ငယ်၏အစွန်းကို ခြစ်ခြင်း သို့မဟုတ် ကွဲအက်ခြင်း၏ အားနည်းချက်များရှိသည်။ ထို့အပြင်၊ သတ္တုမျက်နှာပြင်ပေါ်ရှိ burrs များကိုလုံးဝဖယ်ရှားမပေးသောကြောင့်, ဖြတ်မျက်နှာပြင်သည်အလွန်ကြမ်းတမ်းသည်။

ဤပြဿနာကိုဖြေရှင်းရန်အတွက် "စာရေးခြင်း" ဖြတ်တောက်ခြင်းနည်းလမ်းသည် "မချိုးဖျက်မီ" ၏မျက်နှာပြင်ဖြစ်လာခဲ့သည်။waferအနက်တစ်ဝက်ခန့်ဖြတ်သည်။ “စာရေးခြင်း” သည် wafer ၏ ရှေ့ဘက်ခြမ်းကို ကြိုတင်မြင်ရန် (တစ်ဝက်ဖြတ်) ရန် ပန်ကာကို အသုံးပြုခြင်းကို ရည်ညွှန်းသည်။ အစောပိုင်းကာလများတွင်၊ 6 လက်မအောက်ရှိ wafer အများစုသည် chips များကြားတွင်ပထမဆုံး "slicing" လုပ်ပြီး "breaking" ၏ဤဖြတ်တောက်ခြင်းနည်းလမ်းကိုအသုံးပြုခဲ့သည်။

Blade Dicing သို့မဟုတ် Blade Sawing

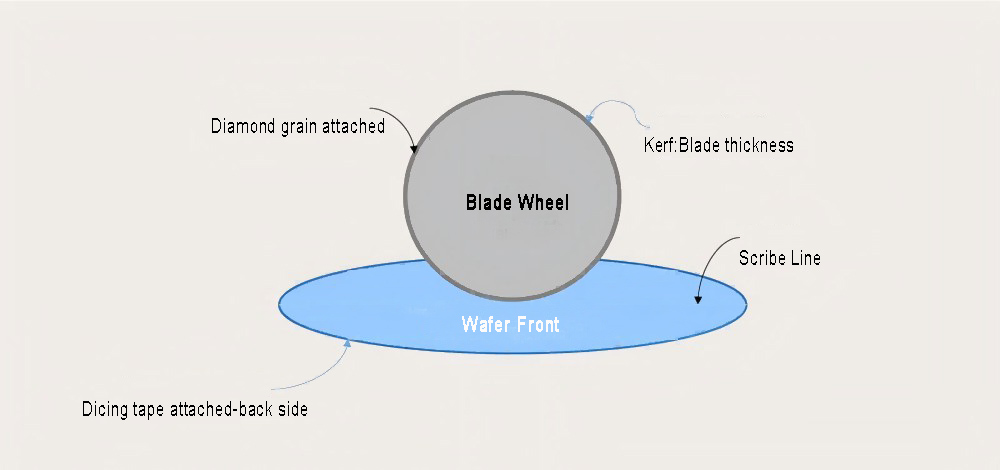

“စာခြစ်” ဖြတ်တောက်ခြင်းနည်းလမ်းသည် ဓါးကို နှစ်ကြိမ် သို့မဟုတ် သုံးကြိမ်ဆက်တိုက် ဖြတ်တောက်ခြင်းနည်းလမ်းဖြစ်သည့် “Blade dicing” cutting (သို့မဟုတ် sawing) နည်းလမ်းသို့ တဖြည်းဖြည်း ဖွံ့ဖြိုးလာခဲ့သည်။ "Blade" ဖြတ်တောက်ခြင်းနည်းလမ်းသည် "scribing" ပြီးနောက် "ကွဲ" သောအခါတွင် သေးငယ်သော ချစ်ပ်ပြားများ ကွဲထွက်ခြင်းဖြစ်စဉ်အတွက် ဖန်တီးနိုင်ပြီး၊ "singulation" လုပ်ငန်းစဉ်အတွင်း သေးငယ်သော ချစ်ပ်ပြားများကို ကာကွယ်နိုင်သည်။ "ဓါး" ဖြတ်တောက်ခြင်းမှာ ယခင် "အတုံးလိုက်" ဖြတ်တောက်ခြင်းနှင့် ကွဲပြားသည်၊ ဆိုလိုသည်မှာ "ဓါး" ဖြတ်တောက်ပြီးနောက်၊ ၎င်းသည် "ကွဲခြင်း" မဟုတ်ဘဲ ဓါးဖြင့် ထပ်မံဖြတ်တောက်ခြင်း ဖြစ်သည်။ ထို့ကြောင့် ၎င်းကို "step dicing" method ဟုခေါ်သည်။

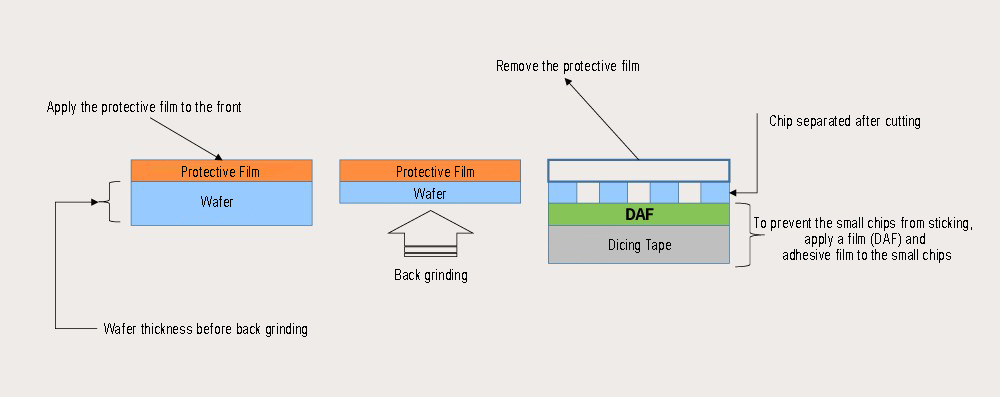

ဖြတ်တောက်ခြင်းလုပ်ငန်းစဉ်အတွင်း wafer ပြင်ပပျက်စီးခြင်းမှကာကွယ်ရန်အတွက် ပိုမိုလုံခြုံစိတ်ချရသော "singling" ကိုသေချာစေရန်အတွက် ဖလင်တစ်ခုအား wafer သို့ကြိုတင်အသုံးပြုမည်ဖြစ်သည်။ "ပြန်ကြိတ်ခြင်း" လုပ်ငန်းစဉ်အတွင်း၊ ရုပ်ရှင်သည် wafer ၏ရှေ့တွင်တွဲနေလိမ့်မည်။ သို့သော်ဆန့်ကျင်ဘက်တွင်၊ "ဓါးခုတ်ခြင်း" တွင်ရုပ်ရှင်ကို wafer ၏နောက်ကျောတွင်တွဲထားသင့်သည်။ eutectic die bonding (die bonding၊ PCB သို့မဟုတ် fixed frame ပေါ်ရှိ သီးခြားချစ်ပ်များကို ပြုပြင်ခြင်း)၊ ကျောဘက်တွင် ချိတ်ထားသော ဖလင်သည် အလိုအလျောက် ပြုတ်ကျသွားမည်ဖြစ်သည်။ ဖြတ်တောက်စဉ်အတွင်း ပွတ်တိုက်မှုမြင့်မားသောကြောင့် DI ရေကို လမ်းကြောင်းအားလုံးမှ အဆက်မပြတ် ဖြန်းပေးသင့်သည်။ ထို့အပြင် အချပ်များကို ပိုမိုကောင်းမွန်စွာ လှီးဖြတ်နိုင်စေရန်အတွက် impeller ကို စိန်မှုန်များဖြင့် တွဲထားသင့်သည်။ ဤအချိန်တွင် ဖြတ်တောက်ခြင်း (ဓါးအထူ- groove width) သည် တစ်ပြေးညီဖြစ်ရမည် ဖြစ်ပြီး dicing groove ၏ အကျယ်ထက် မကျော်လွန်ရပါ။

ကာလအတော်ကြာအောင် လွှဖြတ်ခြင်းသည် အသုံးအများဆုံး သမားရိုးကျ ဖြတ်တောက်ခြင်းနည်းလမ်းဖြစ်သည်။ ၎င်း၏အကြီးမားဆုံးအားသာချက်မှာ wafer အများအပြားကိုအချိန်တိုအတွင်းဖြတ်တောက်နိုင်ခြင်းဖြစ်သည်။ သို့သော် အချပ်၏ အစာစားနှုန်းသည် အလွန်တိုးလာပါက၊ အချပ်လိုက်အစွန်းများ ပေါက်ထွက်နိုင်ခြေ တိုးလာမည်ဖြစ်သည်။ ထို့ကြောင့်၊ impeller ၏လှည့်ပတ်မှုအရေအတွက်ကိုတစ်မိနစ်လျှင်အကြိမ် 30,000 ခန့်ဖြင့်ထိန်းချုပ်သင့်သည်။ ဆီမီးကွန်ဒတ်တာ လုပ်ငန်းစဉ်၏ နည်းပညာသည် စုဆောင်းခြင်းနှင့် အစမ်းသုံးခြင်းနှင့် အမှားအယွင်းများ ကြာရှည်စွာ ဖြည်းညှင်းစွာ စုဆောင်းမိခြင်းဖြစ်သည် (eutectic bonding ဆိုင်ရာ နောက်အပိုင်းတွင်၊ ဖြတ်တောက်ခြင်းနှင့် DAF ဆိုင်ရာ အကြောင်းအရာကို ဆွေးနွေးပါမည်)။

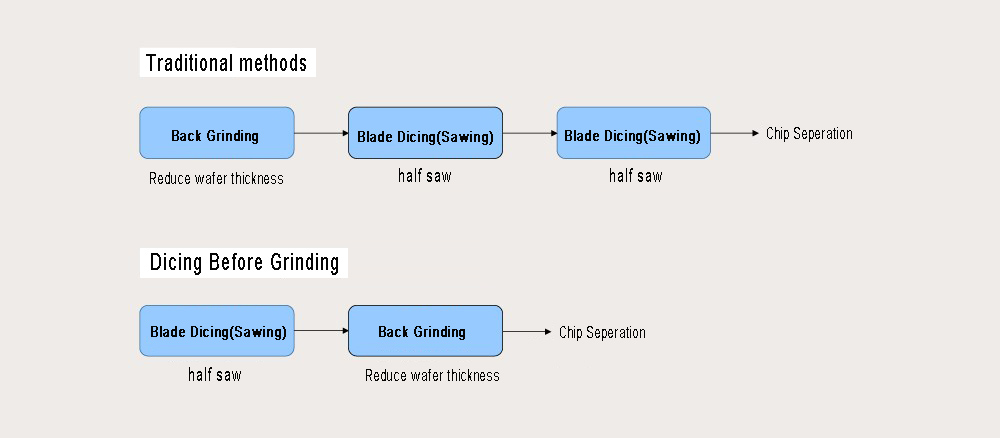

မကြိတ်မီ အတုံးလိုက်အတုံးလိုက် (DBG)- ဖြတ်တောက်ခြင်း အစီအစဉ်သည် နည်းလမ်းကို ပြောင်းလဲသွားခဲ့သည်။

8-လက်မအချင်း wafer ပေါ်တွင် ဓါးဖြတ်ခြင်းကို လုပ်ဆောင်သောအခါ၊ chiplet edge များ ပေါက်ထွက်ခြင်း သို့မဟုတ် ကွဲအက်ခြင်းအတွက် စိုးရိမ်စရာ မလိုအပ်ပါ။ သို့သော် wafer အချင်း 21 လက်မအထိတိုးလာပြီး အထူသည် အလွန်ပါးလွှာလာသည်နှင့်အမျှ အခွံခွာခြင်းနှင့် ကွဲအက်ခြင်းဖြစ်စဉ်များ ထပ်မံပေါ်လာပါသည်။ ဖြတ်တောက်ခြင်း လုပ်ငန်းစဉ်အတွင်း wafer အပေါ် ရုပ်ပိုင်းဆိုင်ရာ အကျိုးသက်ရောက်မှုကို သိသိသာသာ လျှော့ချရန်အတွက် DBG နည်းလမ်းသည် "မကြိတ်မီ လှီးဖြတ်ခြင်း" ၏ ရိုးရာ ဖြတ်တောက်ခြင်း အစီအစဥ်ကို အစားထိုးပါသည်။ အဆက်မပြတ်ဖြတ်သည့် သမားရိုးကျ “ဓါး” ဖြတ်တောက်ခြင်းနည်းလမ်းနှင့် မတူဘဲ၊ DBG သည် ဦးစွာ “ဓါး” ဖြတ်ခြင်းကို လုပ်ဆောင်ပြီး ချစ်ပ်ကွဲသွားသည်အထိ အနောက်ဘက်ခြမ်းကို အဆက်မပြတ် ပါးလွှာစေခြင်းဖြင့် wafer အထူကို တဖြည်းဖြည်း ပါးစေသည်။ DBG သည် ယခင် "blade" ဖြတ်တောက်ခြင်းနည်းလမ်း၏ အဆင့်မြှင့်ထားသော ဗားရှင်းတစ်ခုဟု ဆိုနိုင်ပါသည်။ ဒုတိယဖြတ်တောက်ခြင်း၏အကျိုးသက်ရောက်မှုကိုလျှော့ချနိုင်သောကြောင့် DBG နည်းလမ်းသည် "wafer-level packaging" တွင် လျင်မြန်စွာရေပန်းစားလာခဲ့သည်။

လေဆာဒိုင်းရှင်း

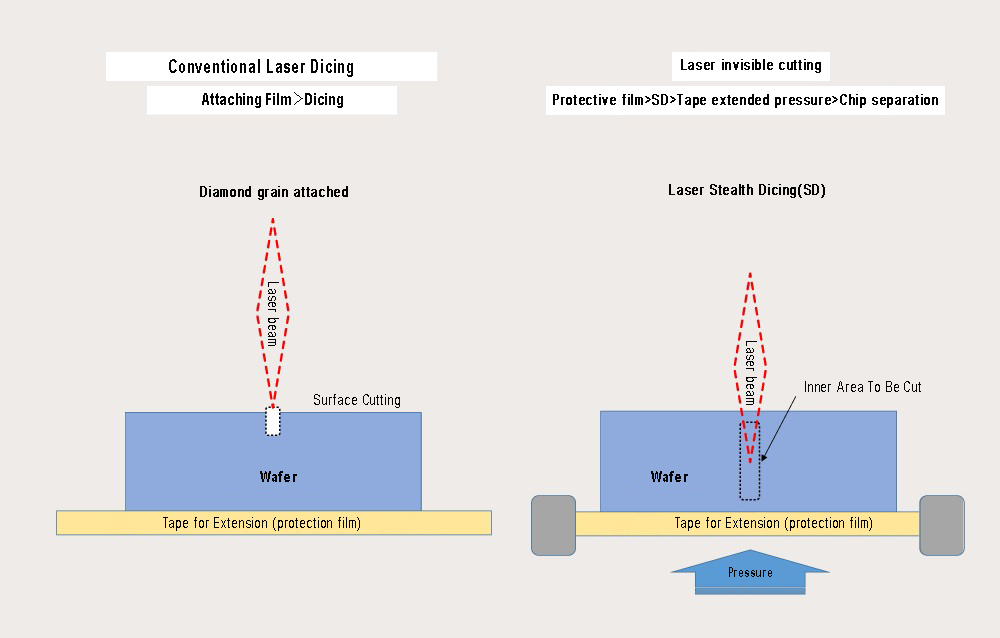

wafer-level chip scale package (WLCSP) လုပ်ငန်းစဉ်သည် လေဆာဖြတ်တောက်ခြင်းကို အဓိကအားဖြင့် အသုံးပြုသည်။ လေဆာဖြတ်တောက်ခြင်းသည် အခွံခွာခြင်းနှင့် ကွဲအက်ခြင်းကဲ့သို့သော ဖြစ်စဉ်များကို လျှော့ချနိုင်ပြီး အရည်အသွေးပိုကောင်းသော ချစ်ပ်ပြားများကို ရရှိစေသော်လည်း wafer အထူသည် 100μm ထက်ပိုသောအခါတွင် ထုတ်လုပ်မှုစွမ်းအားကို များစွာလျော့ကျသွားမည်ဖြစ်ပါသည်။ ထို့ကြောင့်၊ ၎င်းကို 100μm (အတော်လေးပါးသော) ထက်နည်းသော အထူရှိသော wafer များတွင် အများဆုံးအသုံးပြုကြသည်။ လေဆာဖြတ်တောက်ခြင်းသည် wafer's script groove တွင် စွမ်းအင်မြင့်လေဆာဖြင့် ဆီလီကွန်ကို ဖြတ်တောက်ပေးသည်။ သို့သော်၊ သမားရိုးကျလေဆာ (Conventional Laser) ဖြတ်တောက်ခြင်းနည်းလမ်းကို အသုံးပြုသည့်အခါ၊ အကာအကွယ်ဖလင်ပြားကို wafer မျက်နှာပြင်သို့ ကြိုတင်အသုံးပြုရပါမည်။ wafer ၏ မျက်နှာပြင်ကို လေဆာဖြင့် အပူပေးခြင်း သို့မဟုတ် ဓာတ်ရောင်ခြည်ပေးခြင်းကြောင့်၊ အဆိုပါ ရုပ်ပိုင်းဆိုင်ရာ အဆက်အသွယ်များသည် wafer ၏ မျက်နှာပြင်ပေါ်တွင် grooves များထွက်ရှိပြီး ဖြတ်ထားသော ဆီလီကွန်အပိုင်းအစများသည် မျက်နှာပြင်နှင့် ကပ်နေမည်ဖြစ်ပါသည်။ သမားရိုးကျလေဆာဖြတ်တောက်ခြင်းနည်းလမ်းသည် wafer ၏မျက်နှာပြင်ကိုတိုက်ရိုက်ဖြတ်တောက်ကြောင်းတွေ့မြင်နိုင်ပြီး၊ ၎င်းသည် "blade" ဖြတ်တောက်ခြင်းနည်းလမ်းနှင့်ဆင်တူသည်။

Stealth Dicing (SD) သည် wafer အတွင်းပိုင်းကို လေဆာစွမ်းအင်ဖြင့် ဦးစွာ ဖြတ်တောက်ပြီးနောက် ၎င်းကို ကွဲစေရန် နောက်ကျောတွင် ကပ်ထားသော တိပ်ကို ပြင်ပဖိအားကို သက်ရောက်စေပြီး ချစ်ပ်ကို ခွဲထုတ်သည့် နည်းလမ်းဖြစ်သည်။ နောက်ကျောရှိ တိပ်ကို ဖိအားသက်ရောက်သောအခါ၊ တိပ်ကို ဆန့်ထုတ်ခြင်းဖြင့် ချစ်ပ်ကို ပိုင်းခြားနိုင်သောကြောင့် wafer သည် ချက်ချင်းအပေါ်သို့ မြှင့်တက်လာမည်ဖြစ်သည်။ သမားရိုးကျ လေဆာဖြတ်တောက်ခြင်းနည်းလမ်းထက် SD ၏ အားသာချက်များမှာ- ပထမ၊ ဆီလီကွန် အပျက်အစီးများ မရှိပါ။ ဒုတိယ၊ kerf (Kerf: စာရေးဆရာ groove ၏အကျယ်) သည် ကျဉ်းသောကြောင့် ချစ်ပ်များပိုမိုရရှိနိုင်ပါသည်။ ထို့အပြင်၊ ဖြတ်တောက်ခြင်း၏ အလုံးစုံအရည်အသွေးအတွက် အရေးကြီးသော SD နည်းလမ်းကို အသုံးပြု၍ အခွံခွာခြင်းနှင့် ကွဲအက်ခြင်းဖြစ်စဉ်ကို သိသိသာသာ လျှော့ချပါမည်။ ထို့ကြောင့် SD နည်းလမ်းသည် အနာဂတ်တွင် ရေပန်းအစားဆုံး နည်းပညာဖြစ်လာဖွယ်ရှိသည်။

Plasma Dicing

ပလာစမာဖြတ်တောက်ခြင်းသည် ထုတ်လုပ်မှု (Fab) လုပ်ငန်းစဉ်အတွင်း ဖြတ်ရန် ပလာစမာ ခြစ်ခြင်းကို အသုံးပြုသည့် မကြာသေးမီက တီထွင်ထားသော နည်းပညာတစ်ခုဖြစ်သည်။ ပလာစမာဖြတ်တောက်ခြင်းသည် အရည်များအစား ဓာတ်ငွေ့တစ်ပိုင်း ဓာတ်ငွေ့သုံးပစ္စည်းများကို အသုံးပြုသောကြောင့် ပတ်ဝန်းကျင်အပေါ် သက်ရောက်မှုမှာ အနည်းငယ်သာရှိသည်။ ပြီးတော့ wafer တစ်ခုလုံးကို တစ်ကြိမ်တည်းဖြတ်တဲ့နည်းလမ်းကို လက်ခံကျင့်သုံးတဲ့အတွက် "ဖြတ်တောက်ခြင်း" မြန်နှုန်းဟာ အတော်လေးမြန်ပါတယ်။ သို့သော်၊ ပလာစမာနည်းလမ်းသည် ဓာတုတုံ့ပြန်မှုဓာတ်ငွေ့ကို ကုန်ကြမ်းအဖြစ်အသုံးပြုကာ etching လုပ်ငန်းစဉ်သည် အလွန်ရှုပ်ထွေးသောကြောင့် ၎င်း၏လုပ်ငန်းစဉ်စီးဆင်းမှုသည် အတော်လေးခက်ခဲသည်။ သို့သော် "ဓါး" ဖြတ်တောက်ခြင်းနှင့် လေဆာဖြတ်တောက်ခြင်းများနှင့် နှိုင်းယှဉ်ပါက ပလာစမာဖြတ်တောက်ခြင်းသည် wafer မျက်နှာပြင်ကို ထိခိုက်မှုမဖြစ်စေဘဲ ချွတ်ယွင်းမှုနှုန်းကို လျှော့ချပေးပြီး ချစ်ပ်များပိုမိုရရှိစေသည်။

မကြာသေးမီက၊ wafer အထူကို 30μm သို့လျှော့ချလိုက်သောကြောင့်၊ ကြေးနီ (Cu) သို့မဟုတ် low dielectric constant material (Low-k) အများအပြားကို အသုံးပြုကြသည်။ ထို့ကြောင့် burrs (Burr) ကို တားဆီးရန်အတွက် ပလာစမာဖြတ်တောက်ခြင်းနည်းလမ်းများကိုလည်း နှစ်သက်လာမည်ဖြစ်သည်။ ပလာစမာဖြတ်တောက်ခြင်းနည်းပညာသည်လည်း အမြဲတစေ တိုးတက်နေပါသည်။ မဝေးတော့သောအနာဂတ်တွင်၊ ဤအရာသည် ပလာစမာဖြတ်တောက်ခြင်း၏ အဓိက ဦးတည်ချက်ဖြစ်သောကြောင့် ထွင်းထုရာတွင် အထူးမျက်နှာဖုံးကို ဝတ်ဆင်ရန် မလိုအပ်တော့ဟု ကျွန်ုပ်ယုံကြည်ပါသည်။

wafers များ၏အထူသည် 100μm မှ 50μm မှ 30μm သို့ စဉ်ဆက်မပြတ် လျှော့ချလိုက်သောကြောင့် လွတ်လပ်သော ချစ်ပ်ပြားများရယူခြင်းအတွက် ဖြတ်တောက်ခြင်းနည်းလမ်းများသည် "breaking" နှင့် "blade" cutting မှ laser cutting နှင့် plasma cutting သို့ ပြောင်းလဲတိုးတက်နေပါသည်။ ပိုမိုရင့်ကျက်သော ဖြတ်တောက်ခြင်းနည်းလမ်းများသည် ဖြတ်တောက်ခြင်းလုပ်ငန်းစဉ်ကိုယ်တိုင်၏ ထုတ်လုပ်မှုကုန်ကျစရိတ်ကို တိုးမြင့်စေသော်လည်း၊ အခြားတစ်ဖက်တွင်၊ semiconductor ချစ်ပ်ဖြတ်တောက်ခြင်းတွင် ဖြစ်ပေါ်လေ့ရှိသော အခွံခွာခြင်းနှင့် ကွဲအက်ခြင်းကဲ့သို့သော မလိုလားအပ်သော ဖြစ်စဉ်များကို သိသိသာသာ လျှော့ချခြင်းဖြင့် တစ်ယူနစ် wafer ရရှိသော ချစ်ပ်အရေအတွက် တိုးလာသော်လည်း chip တစ်ခုတည်း၏ ထုတ်လုပ်မှုကုန်ကျစရိတ်သည် ကျဆင်းသွားပါသည်။ ဟုတ်ပါတယ်၊ wafer ၏ယူနစ်ဧရိယာတစ်ခုလျှင်ရရှိသောချစ်ပ်အရေအတွက်တိုးလာခြင်းသည် dicing street ၏အကျယ်ကိုလျှော့ချခြင်းနှင့်နီးကပ်စွာဆက်စပ်နေသည်။ ပလာစမာဖြတ်တောက်ခြင်းကိုအသုံးပြုခြင်းဖြင့်၊ လူများသည် ပလာစမာဖြတ်တောက်ခြင်းကိုရွေးချယ်ရသည့် အဓိကအကြောင်းရင်းတစ်ခုဖြစ်သည့် “ဓါး” ဖြတ်တောက်ခြင်းနည်းလမ်းကိုအသုံးပြုခြင်းထက် 20% ပိုမိုချစ်ပ်ပြားများရရှိနိုင်ပါသည်။ wafers များ၊ ချစ်ပ်ပုံပန်းသဏ္ဍာန်နှင့် ထုပ်ပိုးမှုနည်းလမ်းများ၏ ဖွံ့ဖြိုးတိုးတက်မှုနှင့် ပြောင်းလဲမှုများနှင့်အတူ၊ wafer processing technology နှင့် DBG ကဲ့သို့သော အမျိုးမျိုးသော ဖြတ်တောက်ခြင်းလုပ်ငန်းစဉ်များလည်း ပေါ်ထွက်လာပါသည်။

စာတိုက်အချိန်- အောက်တိုဘာ-၁၀-၂၀၂၄