A waferຕ້ອງຜ່ານສາມການປ່ຽນແປງເພື່ອກາຍເປັນຊິບ semiconductor ທີ່ແທ້ຈິງ: ທໍາອິດ, ແຜ່ນຮູບຊົງຕັນຖືກຕັດເຂົ້າໄປໃນ wafers; ໃນຂະບວນການທີສອງ, transistors ແມ່ນ engraved ຢູ່ດ້ານຫນ້າຂອງ wafer ໂດຍຜ່ານຂະບວນການທີ່ຜ່ານມາ; ສຸດທ້າຍ, ການຫຸ້ມຫໍ່ແມ່ນປະຕິບັດ, ນັ້ນແມ່ນ, ໂດຍຜ່ານຂະບວນການຕັດwaferກາຍເປັນຊິບ semiconductor ສົມບູນ. ມັນສາມາດເຫັນໄດ້ວ່າຂະບວນການຫຸ້ມຫໍ່ເປັນຂອງຂະບວນການ back-end. ໃນຂະບວນການນີ້, wafer ຈະຖືກຕັດອອກເປັນ chip hexahedron ສ່ວນບຸກຄົນຫຼາຍ. ຂະບວນການຂອງການໄດ້ຮັບຊິບເອກະລາດນີ້ເອີ້ນວ່າ "Singulation", ແລະຂະບວນການຂອງການເລື່ອຍກະດານ wafer ເຂົ້າໄປໃນ cuboids ເອກະລາດແມ່ນເອີ້ນວ່າ "ການຕັດ wafer (Die Sawing)". ບໍ່ດົນມານີ້, ດ້ວຍການປັບປຸງການເຊື່ອມໂຍງ semiconductor, ຄວາມຫນາຂອງwafersໄດ້ກາຍເປັນບາງແລະບາງກວ່າ, ເຊິ່ງແນ່ນອນວ່າມັນນໍາເອົາຄວາມຫຍຸ້ງຍາກຫຼາຍໃນຂະບວນການ "singulation".

ການພັດທະນາຂອງ dicing wafer ໄດ້

ຂະບວນການດ້ານຫນ້າແລະດ້ານຫລັງໄດ້ພັດທະນາໂດຍຜ່ານການປະຕິສໍາພັນໃນລັກສະນະຕ່າງໆ: ການວິວັດທະນາການຂອງຂະບວນການດ້ານຫລັງສາມາດກໍານົດໂຄງສ້າງແລະຕໍາແຫນ່ງຂອງ chip hexahedron ຂະຫນາດນ້ອຍທີ່ແຍກອອກຈາກຕາຍເທິງ.wafer, ເຊັ່ນດຽວກັນກັບໂຄງສ້າງແລະຕໍາແຫນ່ງຂອງ pads (ເສັ້ນທາງເຊື່ອມຕໍ່ໄຟຟ້າ) ໃນ wafer ໄດ້; ໃນທາງກົງກັນຂ້າມ, ການວິວັດທະນາການຂອງຂະບວນການທາງຫນ້າໄດ້ປ່ຽນແປງຂະບວນການແລະວິທີການwaferກັບຄືນໄປບ່ອນ thinning ແລະ "ຕາຍ dicing" ໃນຂະບວນການ back-end. ດັ່ງນັ້ນ, ຮູບລັກສະນະທີ່ມີຄວາມຊັບຊ້ອນເພີ່ມຂຶ້ນຂອງຊຸດຈະມີຜົນກະທົບຢ່າງຫຼວງຫຼາຍຕໍ່ຂະບວນການດ້ານຫລັງ. ຍິ່ງໄປກວ່ານັ້ນ, ຈໍານວນ, ຂັ້ນຕອນແລະປະເພດຂອງ dicing ຍັງຈະມີການປ່ຽນແປງຕາມຄວາມເຫມາະສົມຂອງການປ່ຽນແປງໃນຮູບລັກສະນະຂອງຊຸດ.

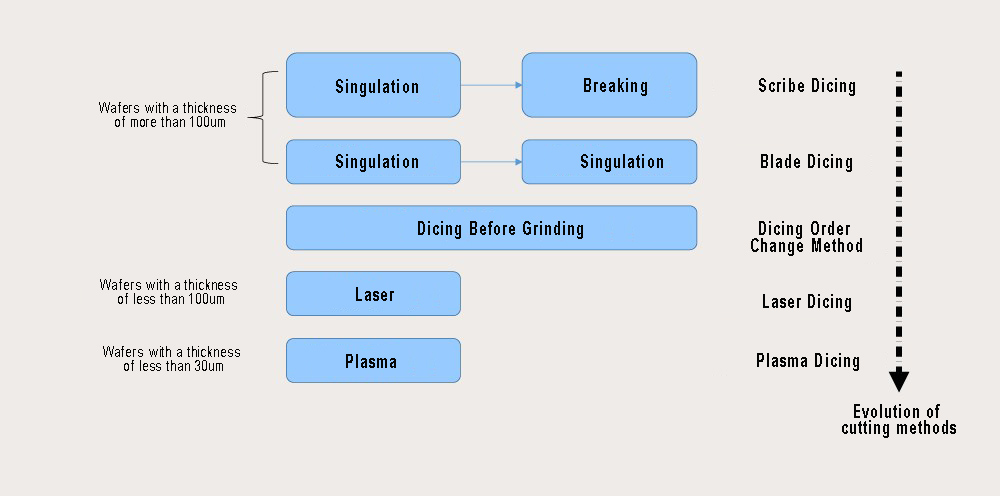

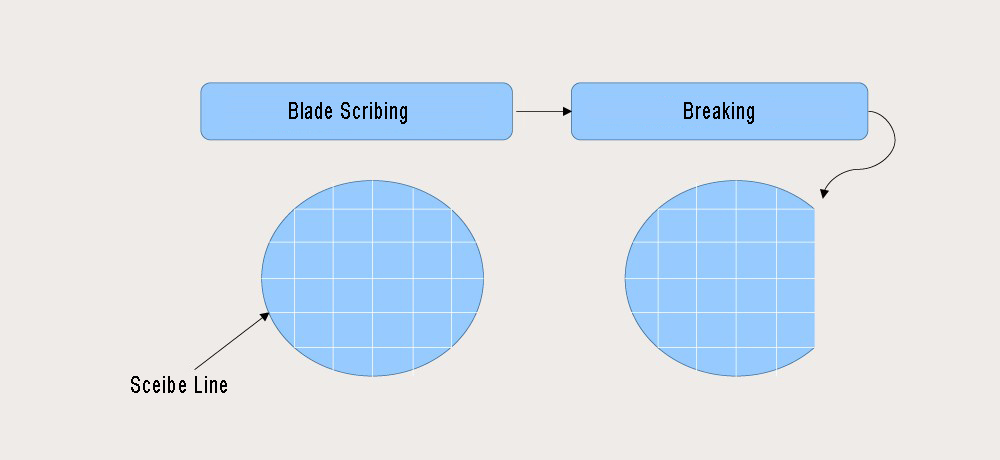

Scribe Dicing

ໃນຕອນຕົ້ນ, "ການທໍາລາຍ" ໂດຍການນໍາໃຊ້ຜົນບັງຄັບໃຊ້ພາຍນອກແມ່ນວິທີດຽວທີ່ສາມາດແບ່ງອອກໄດ້waferເຂົ້າໄປໃນ hexahedron ຕາຍ. ຢ່າງໃດກໍຕາມ, ວິທີການນີ້ມີຂໍ້ເສຍຂອງ chipping ຫຼື cracking ຂອງຂອບຂອງ chip ຂະຫນາດນ້ອຍ. ນອກຈາກນັ້ນ, ນັບຕັ້ງແຕ່ burrs ເທິງຫນ້າໂລຫະບໍ່ໄດ້ຖືກໂຍກຍ້າຍອອກຫມົດ, ດ້ານຕັດຍັງ rough ຫຼາຍ.

ເພື່ອແກ້ໄຂບັນຫານີ້, ວິທີການຕັດ "Scribing" ໄດ້ກາຍເປັນ, ນັ້ນແມ່ນ, ກ່ອນທີ່ຈະ "ແຕກ", ດ້ານຂອງ.waferຖືກຕັດອອກປະມານເຄິ່ງຫນຶ່ງຂອງຄວາມເລິກ. "scribing", ຕາມຊື່ແນະນໍາ, ຫມາຍເຖິງການໃຊ້ impeller ເພື່ອ saw (ຕັດເຄິ່ງຫນຶ່ງ) ດ້ານຫນ້າຂອງ wafer ລ່ວງຫນ້າ. ໃນຕອນຕົ້ນ, wafers ສ່ວນໃຫຍ່ຕ່ໍາກວ່າ 6 ນິ້ວໄດ້ໃຊ້ວິທີການຕັດນີ້ຄັ້ງທໍາອິດ "ຕັດ" ລະຫວ່າງຊິບແລະຫຼັງຈາກນັ້ນ "ແຕກ".

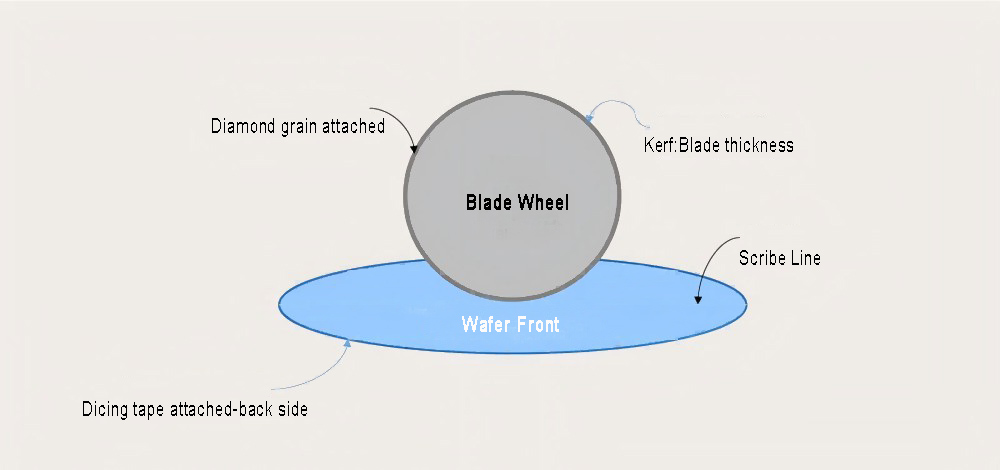

ໃບມີດຕັດ ຫຼື ຕັດແຜ່ນໃບ

ວິທີການຕັດ "Sccribing" ຄ່ອຍໆພັດທະນາໄປສູ່ວິທີການຕັດ (ຫຼື sawing) "ແຜ່ນໃບຄ້າຍຄື", ເຊິ່ງເປັນວິທີການຕັດໂດຍໃຊ້ແຜ່ນໃບສອງຫຼືສາມເທື່ອຕິດຕໍ່ກັນ. ວິທີການຕັດ "ແຜ່ນໃບ" ສາມາດເຮັດໃຫ້ປະກົດການຂອງ chip ຂະຫນາດນ້ອຍປອກເປືອກອອກໃນເວລາທີ່ "ແຕກ" ຫຼັງຈາກ "scribing", ແລະສາມາດປົກປ້ອງ chip ຂະຫນາດນ້ອຍໃນລະຫວ່າງການຂະບວນການ "singulation". ການຕັດ "ແຜ່ນໃບ" ແມ່ນແຕກຕ່າງຈາກການຕັດ "dicing" ທີ່ຜ່ານມາ, ນັ້ນແມ່ນ, ຫຼັງຈາກການຕັດ "ແຜ່ນໃບ", ມັນບໍ່ແມ່ນ "ແຕກ", ແຕ່ຕັດອີກເທື່ອຫນຶ່ງດ້ວຍແຜ່ນໃບ. ເພາະສະນັ້ນ, ມັນຖືກເອີ້ນວ່າ "ຂັ້ນຕອນ dicing".

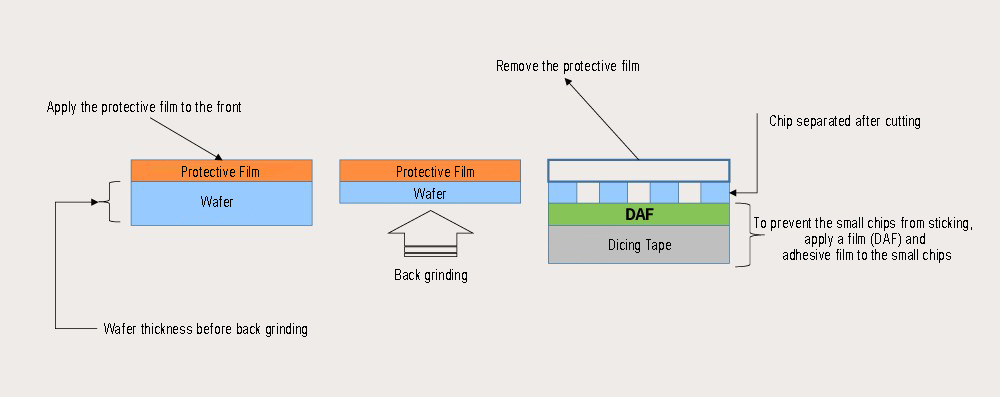

ເພື່ອປົກປ້ອງ wafer ຈາກຄວາມເສຍຫາຍພາຍນອກໃນລະຫວ່າງຂະບວນການຕັດ, ຮູບເງົາຈະຖືກນໍາໄປໃຊ້ກັບ wafer ລ່ວງຫນ້າເພື່ອຮັບປະກັນ "singling" ທີ່ປອດໄພກວ່າ. ໃນລະຫວ່າງຂະບວນການ "ປີ້ງຫລັງ", ຮູບເງົາຈະຖືກຕິດຢູ່ດ້ານຫນ້າຂອງ wafer. ແຕ່ໃນທາງກົງກັນຂ້າມ, ໃນການຕັດ "ແຜ່ນໃບ", ຮູບເງົາຄວນຈະຕິດກັບດ້ານຫລັງຂອງ wafer. ໃນລະຫວ່າງການຜູກມັດຕາຍ eutectic (ການຜູກມັດຕາຍ, ການສ້ອມແຊມຊິບທີ່ແຍກຢູ່ໃນ PCB ຫຼືກອບຄົງທີ່), ຮູບເງົາທີ່ຕິດກັບດ້ານຫລັງຈະຫຼຸດລົງໂດຍອັດຕະໂນມັດ. ເນື່ອງຈາກມີ friction ສູງໃນລະຫວ່າງການຕັດ, ນ້ໍາ DI ຄວນໄດ້ຮັບການສີດຢ່າງຕໍ່ເນື່ອງຈາກທຸກທິດທາງ. ນອກຈາກນັ້ນ, impeller ຄວນຖືກຕິດດ້ວຍ particles ເພັດເພື່ອໃຫ້ຫຼັງຈາກນັ້ນນໍາຫຼັງຈາກນັ້ນນໍາໄດ້ດີກວ່າ. ໃນເວລານີ້, ການຕັດ (ຄວາມຫນາຂອງແຜ່ນໃບຄ້າຍຄື: ຄວາມກວ້າງຂອງຮ່ອງ) ຕ້ອງມີຄວາມເປັນເອກະພາບແລະບໍ່ຄວນເກີນຄວາມກວ້າງຂອງຮ່ອງ dicing.

ສໍາລັບເວລາດົນນານ, sawing ໄດ້ຖືກນໍາໃຊ້ຢ່າງກວ້າງຂວາງທີ່ສຸດວິທີການຕັດພື້ນເມືອງ. ປະໂຫຍດທີ່ໃຫຍ່ທີ່ສຸດຂອງມັນແມ່ນວ່າມັນສາມາດຕັດ wafers ຈໍານວນຫລາຍໃນເວລາສັ້ນໆ. ຢ່າງໃດກໍຕາມ, ຖ້າຄວາມໄວການໃຫ້ອາຫານຂອງຊິ້ນແມ່ນເພີ່ມຂຶ້ນຢ່າງຫຼວງຫຼາຍ, ຄວາມເປັນໄປໄດ້ຂອງການປອກເປືອກ chiplet ຈະເພີ່ມຂຶ້ນ. ດັ່ງນັ້ນ, ຈໍານວນຂອງການຫມຸນຂອງ impeller ຄວນໄດ້ຮັບການຄວບຄຸມປະມານ 30,000 ເທື່ອຕໍ່ນາທີ. ມັນສາມາດເຫັນໄດ້ວ່າເທກໂນໂລຍີຂອງຂະບວນການ semiconductor ມັກຈະເປັນຄວາມລັບທີ່ສະສົມຢ່າງຊ້າໆໂດຍຜ່ານໄລຍະເວລາທີ່ຍາວນານຂອງການສະສົມແລະການທົດລອງແລະຄວາມຜິດພາດ (ໃນພາກຕໍ່ໄປກ່ຽວກັບການຜູກມັດ eutectic, ພວກເຮົາຈະປຶກສາຫາລືກ່ຽວກັບເນື້ອໃນກ່ຽວກັບການຕັດແລະ DAF).

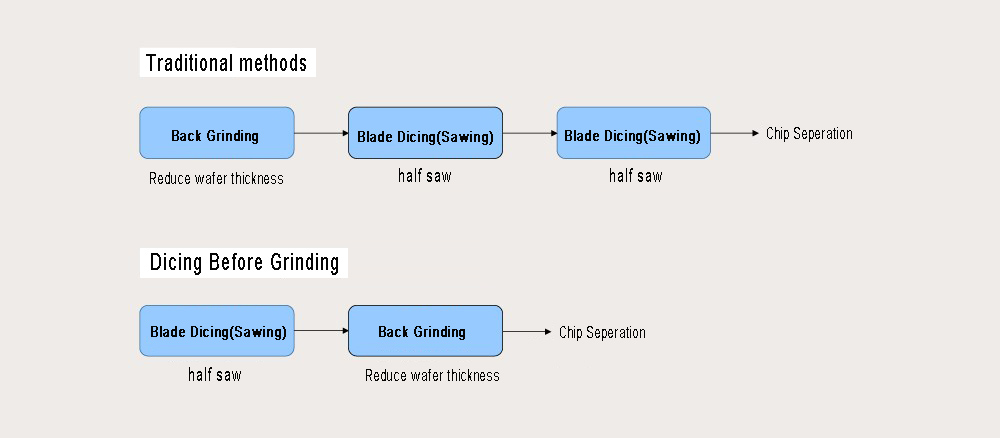

Dicing ກ່ອນ grinding (DBG): ລໍາດັບການຕັດໄດ້ມີການປ່ຽນແປງວິທີການ

ໃນເວລາທີ່ການຕັດແຜ່ນໃບແມ່ນດໍາເນີນຢູ່ໃນ wafer ເສັ້ນຜ່າກາງ 8 ນິ້ວ, ບໍ່ຈໍາເປັນຕ້ອງກັງວົນກ່ຽວກັບການປອກເປືອກຫຼືຮອຍແຕກຂອງແຜ່ນໃບ. ແຕ່ຍ້ອນວ່າເສັ້ນຜ່າສູນກາງຂອງ wafer ເພີ່ມຂຶ້ນເຖິງ 21 ນິ້ວແລະຄວາມຫນາຈະກາຍເປັນບາງທີ່ສຸດ, ປະກົດການປອກເປືອກແລະຮອຍແຕກເລີ່ມປາກົດອີກເທື່ອຫນຶ່ງ. ເພື່ອຫຼຸດຜ່ອນຜົນກະທົບທາງດ້ານຮ່າງກາຍຢ່າງຫຼວງຫຼາຍຕໍ່ wafer ໃນຂະບວນການຕັດ, ວິທີການ DBG ຂອງ "dicing ກ່ອນ grinding" ແທນລໍາດັບການຕັດແບບດັ້ງເດີມ. ບໍ່ເຫມືອນກັບວິທີການຕັດ "ແຜ່ນໃບ" ແບບດັ້ງເດີມທີ່ຕັດຢ່າງຕໍ່ເນື່ອງ, DBG ທໍາອິດດໍາເນີນການຕັດ "ແຜ່ນໃບ", ແລະຫຼັງຈາກນັ້ນຄ່ອຍໆເຮັດໃຫ້ຄວາມຫນາຂອງ wafer ຄ່ອຍໆບາງໆດ້ານຫລັງຈົນກ່ວາຊິບແຕກ. ມັນສາມາດເວົ້າໄດ້ວ່າ DBG ແມ່ນສະບັບປັບປຸງຂອງວິທີການຕັດ "ແຜ່ນໃບ" ທີ່ຜ່ານມາ. ເນື່ອງຈາກວ່າມັນສາມາດຫຼຸດຜ່ອນຜົນກະທົບຂອງການຕັດທີສອງ, ວິທີການ DBG ໄດ້ຮັບຄວາມນິຍົມຢ່າງໄວວາໃນ "ການຫຸ້ມຫໍ່ລະດັບ wafer".

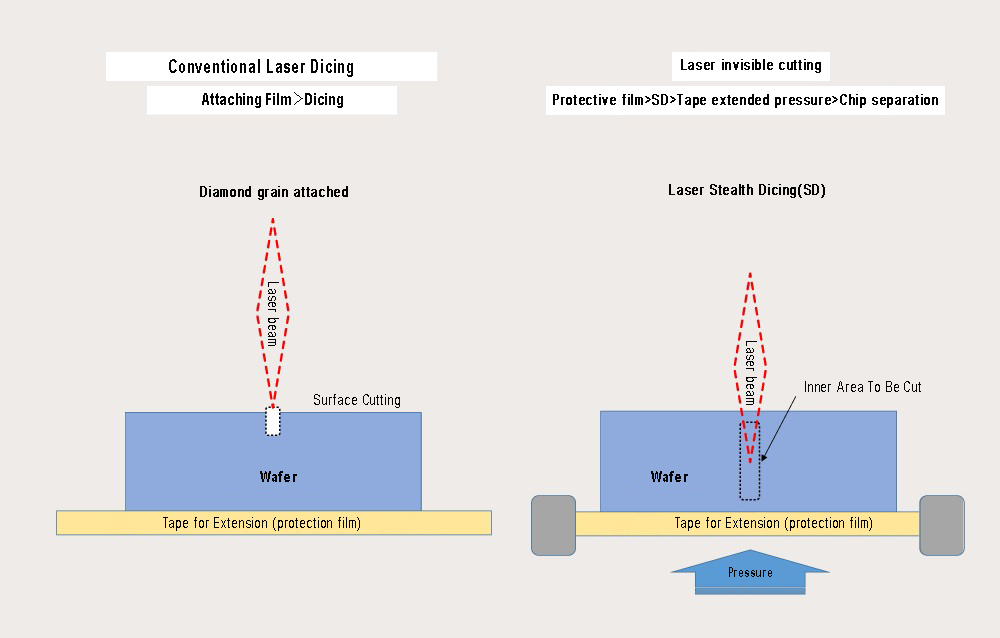

Laser Dicing

ຂະບວນການຂະຫນາດຊິບລະດັບ wafer (WLCSP) ສ່ວນໃຫຍ່ແມ່ນໃຊ້ການຕັດເລເຊີ. ການຕັດດ້ວຍເລເຊີສາມາດຫຼຸດຜ່ອນປະກົດການຕ່າງໆເຊັ່ນການປອກເປືອກແລະຮອຍແຕກ, ດັ່ງນັ້ນຈຶ່ງໄດ້ຮັບຊິບທີ່ມີຄຸນນະພາບດີກວ່າ, ແຕ່ເມື່ອຄວາມຫນາຂອງ wafer ແມ່ນຫຼາຍກ່ວາ 100μm, ຜົນຜະລິດຈະຫຼຸດລົງຢ່າງຫຼວງຫຼາຍ. ດັ່ງນັ້ນ, ສ່ວນຫຼາຍແມ່ນໃຊ້ໃນ wafers ທີ່ມີຄວາມຫນາຫນ້ອຍກວ່າ 100μm (ຂ້ອນຂ້າງບາງ). ການຕັດດ້ວຍເລເຊີຕັດຊິລິໂຄນໂດຍການໃຊ້ເລເຊີທີ່ມີພະລັງງານສູງໃສ່ຮ່ອງຮອຍຂອງ wafer. ຢ່າງໃດກໍຕາມ, ເມື່ອນໍາໃຊ້ວິທີການຕັດ laser ທໍາມະດາ (ເລເຊີທໍາມະດາ), ຮູບເງົາປ້ອງກັນຕ້ອງຖືກນໍາໃຊ້ກັບຫນ້າດິນ wafer ລ່ວງຫນ້າ. ເນື່ອງຈາກວ່າການໃຫ້ຄວາມຮ້ອນຫຼື irradiating ດ້ານຂອງ wafer ດ້ວຍເລເຊີ, ການຕິດຕໍ່ທາງກາຍະພາບເຫຼົ່ານີ້ຈະຜະລິດ grooves ເທິງຫນ້າດິນຂອງ wafer ໄດ້, ແລະ fragments silicon ຕັດຍັງຈະຕິດກັບຫນ້າດິນ. ມັນສາມາດເຫັນໄດ້ວ່າວິທີການຕັດເລເຊີແບບດັ້ງເດີມຍັງຕັດພື້ນຜິວຂອງ wafer ໂດຍກົງ, ແລະໃນເລື່ອງນີ້, ມັນຄ້າຍຄືກັບວິທີການຕັດ "ແຜ່ນໃບ".

Stealth Dicing (SD) ແມ່ນວິທີການທໍາອິດຕັດພາຍໃນຂອງ wafer ດ້ວຍພະລັງງານ laser, ແລະຫຼັງຈາກນັ້ນນໍາໃຊ້ຄວາມກົດດັນພາຍນອກກັບ tape ທີ່ຕິດກັບກັບຄືນໄປບ່ອນເພື່ອທໍາລາຍມັນ, ດັ່ງນັ້ນການແຍກ chip ໄດ້. ເມື່ອຄວາມກົດດັນຖືກນໍາໃຊ້ກັບ tape ຢູ່ດ້ານຫລັງ, wafer ຈະຖືກຍົກຂຶ້ນທັນທີເນື່ອງຈາກການຍືດຂອງ tape, ດັ່ງນັ້ນຈຶ່ງແຍກ chip. ຂໍ້ດີຂອງ SD ໃນໄລຍະວິທີການຕັດ laser ແບບດັ້ງເດີມແມ່ນ: ທໍາອິດ, ບໍ່ມີ silicon debris; ອັນທີສອງ, kerf (Kerf: width ຂອງ scribe groove) ແມ່ນແຄບ, ດັ່ງນັ້ນ chip ຫຼາຍສາມາດໄດ້ຮັບ. ນອກຈາກນັ້ນ, ປະກົດການປອກເປືອກແລະຮອຍແຕກຈະຫຼຸດລົງຢ່າງຫຼວງຫຼາຍໂດຍໃຊ້ວິທີການ SD, ເຊິ່ງເປັນສິ່ງສໍາຄັນຕໍ່ຄຸນນະພາບໂດຍລວມຂອງການຕັດ. ດັ່ງນັ້ນ, ວິທີການ SD ມີແນວໂນ້ມທີ່ຈະກາຍເປັນເຕັກໂນໂລຢີທີ່ນິຍົມທີ່ສຸດໃນອະນາຄົດ.

Plasma Dicing

ການຕັດ plasma ແມ່ນເຕັກໂນໂລຢີທີ່ພັດທະນາເມື່ອໄວໆມານີ້ທີ່ໃຊ້ plasma etching ເພື່ອຕັດໃນລະຫວ່າງຂະບວນການຜະລິດ (Fab). ການຕັດ plasma ໃຊ້ວັດສະດຸເຄິ່ງອາຍແກັສແທນທີ່ຈະເປັນຂອງແຫຼວ, ດັ່ງນັ້ນຜົນກະທົບຕໍ່ສິ່ງແວດລ້ອມແມ່ນຂ້ອນຂ້າງນ້ອຍ. ແລະວິທີການຕັດ wafer ທັງຫມົດໃນເວລາດຽວໄດ້ຖືກຮັບຮອງເອົາ, ດັ່ງນັ້ນຄວາມໄວ "ຕັດ" ແມ່ນຂ້ອນຂ້າງໄວ. ຢ່າງໃດກໍຕາມ, ວິທີການ plasma ໃຊ້ອາຍແກັສຕິກິຣິຍາເຄມີເປັນວັດຖຸດິບ, ແລະຂະບວນການ etching ແມ່ນສັບສົນຫຼາຍ, ສະນັ້ນການໄຫຼຂອງຂະບວນການຂອງມັນແມ່ນຂ້ອນຂ້າງ cumbersome. ແຕ່ເມື່ອປຽບທຽບກັບການຕັດ "ແຜ່ນໃບ" ແລະການຕັດດ້ວຍເລເຊີ, ການຕັດ plasma ບໍ່ໄດ້ເຮັດໃຫ້ເກີດຄວາມເສຍຫາຍຕໍ່ຫນ້າ wafer, ດັ່ງນັ້ນການຫຼຸດຜ່ອນອັດຕາການຜິດປົກກະຕິແລະໄດ້ຮັບ chip ຫຼາຍ.

ບໍ່ດົນມານີ້, ນັບຕັ້ງແຕ່ຄວາມຫນາຂອງ wafer ໄດ້ຖືກຫຼຸດລົງເປັນ30μm, ແລະຫຼາຍຂອງທອງແດງ (Cu) ຫຼືວັດສະດຸຄົງທີ່ dielectric ຕ່ໍາ (Low-k) ໄດ້ຖືກນໍາໃຊ້. ດັ່ງນັ້ນ, ເພື່ອປ້ອງກັນ burrs (Burr), ວິທີການຕັດ plasma ຍັງຈະໄດ້ຮັບການເອື້ອອໍານວຍ. ແນ່ນອນ, ເຕັກໂນໂລຊີການຕັດ plasma ຍັງພັດທະນາຢ່າງຕໍ່ເນື່ອງ. ຂ້າພະເຈົ້າເຊື່ອວ່າໃນອະນາຄົດອັນໃກ້ນີ້, ມື້ຫນຶ່ງຈະບໍ່ຈໍາເປັນຕ້ອງໃສ່ຫນ້າກາກພິເສດໃນເວລາທີ່ etching, ເພາະວ່ານີ້ແມ່ນທິດທາງການພັດທະນາທີ່ສໍາຄັນຂອງການຕັດ plasma.

ເນື່ອງຈາກຄວາມຫນາຂອງ wafers ໄດ້ຖືກຫຼຸດລົງຢ່າງຕໍ່ເນື່ອງຈາກ100μmຫາ50μmແລະຫຼັງຈາກນັ້ນເປັນ30μm, ວິທີການຕັດສໍາລັບການໄດ້ຮັບ chip ເອກະລາດຍັງມີການປ່ຽນແປງແລະພັດທະນາຈາກການຕັດ "ແຕກ" ແລະ "ແຜ່ນໃບຄ້າຍຄື" ໄປສູ່ການຕັດ laser ແລະ plasma. ເຖິງແມ່ນວ່າວິທີການຕັດທີ່ໃຫຍ່ກວ່າໄດ້ເພີ່ມຕົ້ນທຶນການຜະລິດຂອງຂະບວນການຕັດຕົວມັນເອງ, ໃນທາງກົງກັນຂ້າມ, ໂດຍການຫຼຸດຜ່ອນປະກົດການທີ່ບໍ່ຕ້ອງການເຊັ່ນການປອກເປືອກແລະຮອຍແຕກທີ່ມັກຈະເກີດຂື້ນໃນການຕັດຊິບ semiconductor ແລະການເພີ່ມຈໍານວນຊິບທີ່ໄດ້ຮັບຕໍ່ wafer ຫນ່ວຍ, ຄ່າໃຊ້ຈ່າຍໃນການຜະລິດຂອງຊິບດຽວໄດ້ສະແດງໃຫ້ເຫັນທ່າອ່ຽງຫຼຸດລົງ. ແນ່ນອນ, ການເພີ່ມຂຶ້ນຂອງຈໍານວນຊິບທີ່ໄດ້ຮັບຕໍ່ພື້ນທີ່ຫນ່ວຍຂອງ wafer ແມ່ນກ່ຽວຂ້ອງຢ່າງໃກ້ຊິດກັບການຫຼຸດຜ່ອນຄວາມກວ້າງຂອງຖະຫນົນ dicing. ການນໍາໃຊ້ການຕັດ plasma, ເກືອບ 20% ຊິບສາມາດໄດ້ຮັບຫຼາຍກ່ວາການນໍາໃຊ້ວິທີການຕັດ "ແຜ່ນໃບ", ເຊິ່ງຍັງເປັນເຫດຜົນສໍາຄັນທີ່ເຮັດໃຫ້ປະຊາຊົນເລືອກການຕັດ plasma. ດ້ວຍການພັດທະນາແລະການປ່ຽນແປງຂອງ wafers, ຮູບລັກສະນະຂອງຊິບແລະວິທີການຫຸ້ມຫໍ່, ຂະບວນການຕັດຕ່າງໆເຊັ່ນ: ເຕັກໂນໂລຢີການປຸງແຕ່ງ wafer ແລະ DBG ຍັງເກີດຂື້ນ.

ເວລາປະກາດ: ຕຸລາ-10-2024