Grata nostro loco ad informationem productam et consultationem.

Nostra website:https://www.vet-china.com/

Cum processus semiconductor fabricandi ad breakthroughs pergunt, editio illustris "Lex Moore" dicta in industria grassata est. Propositum a Gordon Moore, uno fundatorum Intel, anno 1965. Eius nucleus contentus est: numerus transistorum, qui in ambitu integrali accommodari potest, circa singulos XVIII ad XXIIII menses duplicabit. Haec lex non solum analysis ac praenuntiatio de industria evolutionis inclinatio est, sed etiam vis impulsus ad processuum facientium semiconductorem evolutionem - omnia transistores minore magnitudine ac stabili operatione efficere debent. Ab annis 1950 ad hunc, circiter 70 annos, summa BJT, MOSFET, CMOS, DMOS et technologiae hybridarum BiCMOS et BCD ortae sunt.

1. BJT

Coniunctio bipolaris transistoris (BJT), vulgo triode. Crimen transistoris influunt maxime ob diffusionem et gestantium motum in PN coniunctas. Cum fluxum tam electrons quam foraminum involvit, bipolaris fabrica dicitur.

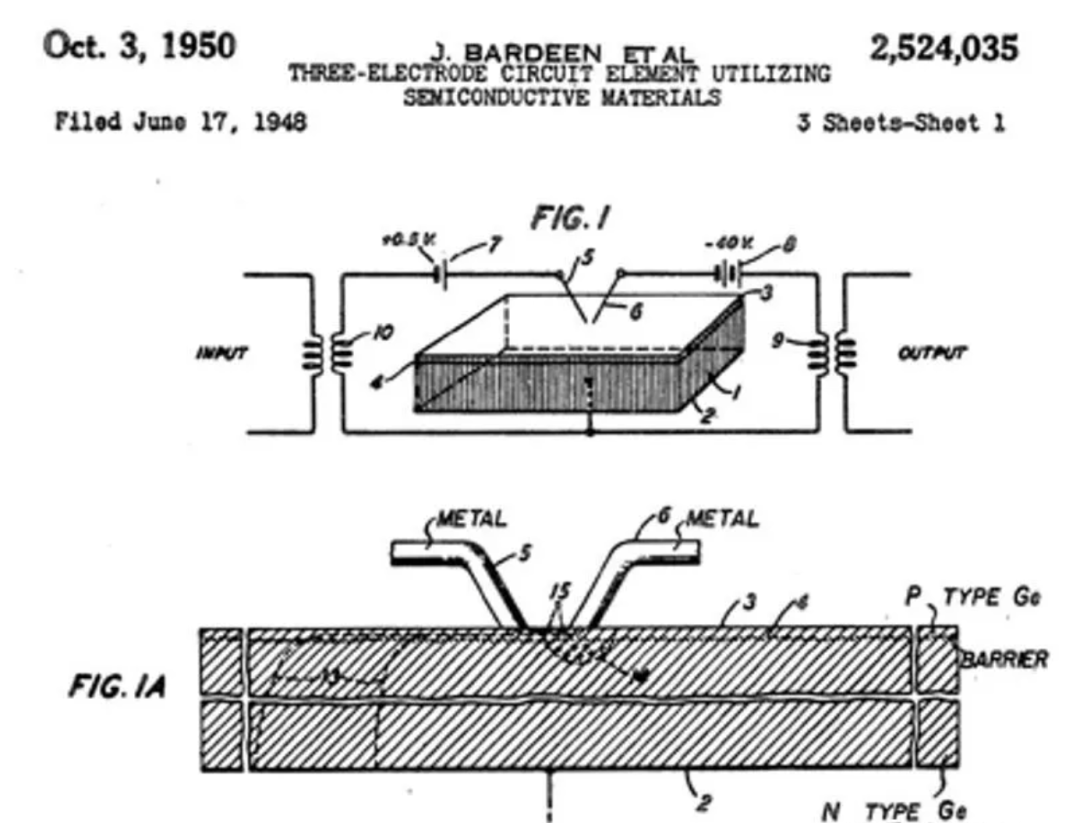

Respiciens ad historiam natiuitatis. Propter ideam de triodis vacuum cum amplificantibus solidis reponendi, Shockley proposuit investigationem fundamentalem de semiconductoribus in aestate anni 1945 perficiendam. In secunda parte anni 1945, Bell Labs solidam publicam inquisitionem physicam coetus a Shockley petens constituit. In hoc coetu non solum physici, sed etiam circuli mechanici et chemici, inter Bardeen, physicus theoricus, et Brattain, physicus experimentalis. Mense Decembri MCMXLVII, eventus qui miliarius a posterioribus generationibus aestimatus est, egregie gestum est - Bardeen et Brattain feliciter primum punctum contactum transistoris germanium mundi cum amplificatione currenti excogitaverunt.

Bardeen et Brattain primus punctum-contactus transistor

Paulo post, Shockley connexionem bipolarem invenisse anno 1948. Proposuit transistorem ex duabus iunctionibus pn iunctionibus, unum deinceps obversitatis et alterum obversis obnixum, et patentes consecutus mense Iunio 1948. Anno 1949 theoriam accuratam edidit. operationis confluentes transistoris. Plus quam duobus annis post, phisici et fabrum apud Bell Labs processum elaboraverunt ad efficiendum transistores massam coniunctionis (millestone anno 1951), novam technologiae electronicae aetatem aperientes. In recognitione contributionum ad transistores inventionis, Shockley, Bardeen et Brattain coniunctim vicit Praemium Nobel 1956 in Physica.

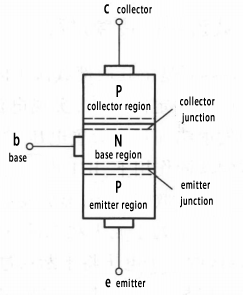

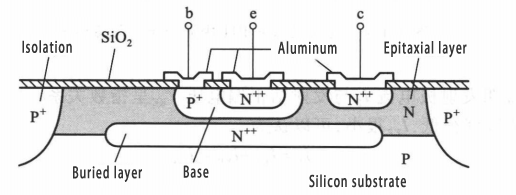

Simplex structural schematis de NPN bipolaris confluentes transistoris

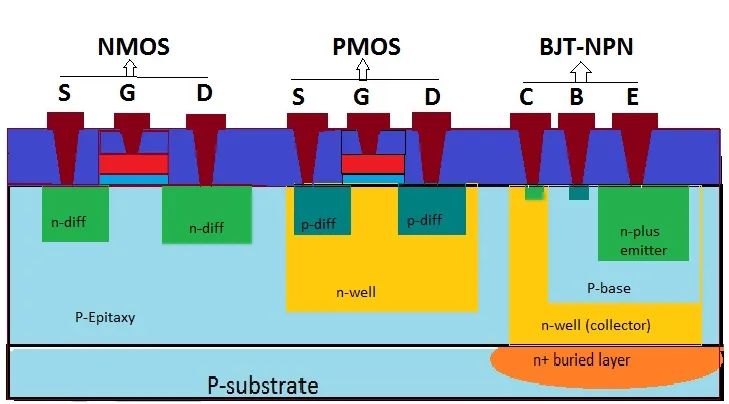

Quoad structuram commissurae bipolaris transistorum, communes BJTs sunt NPN et PNP. Delineatio interna structura in figura infra ostenditur. Impudicitia regio semiconductori emittentei correspondens est regio emittente, quae altam doping conducit; immunditia regionis semiconductoris correspondens basi est regio basi, quae latitudinem tenuissimam et attentionem dopingem ima habet; immunditia regionis semiconductoris respondentis collectori est regio collectoris, quae magnam aream habet et intentionem dopingem nimis humilem habet.

Commoda technologiae BJT altae sunt celeritatis responsionis, altae transconductentiae (input voltages mutationes magnae output mutationes current), strepitus humilis, altae accurationis analogi, et valida vena incessus facultas; incommoda sunt humilia integratio (profunditas verticalis cum magnitudine laterali reduci non potest) et summa potentia consummatio.

2. MOS

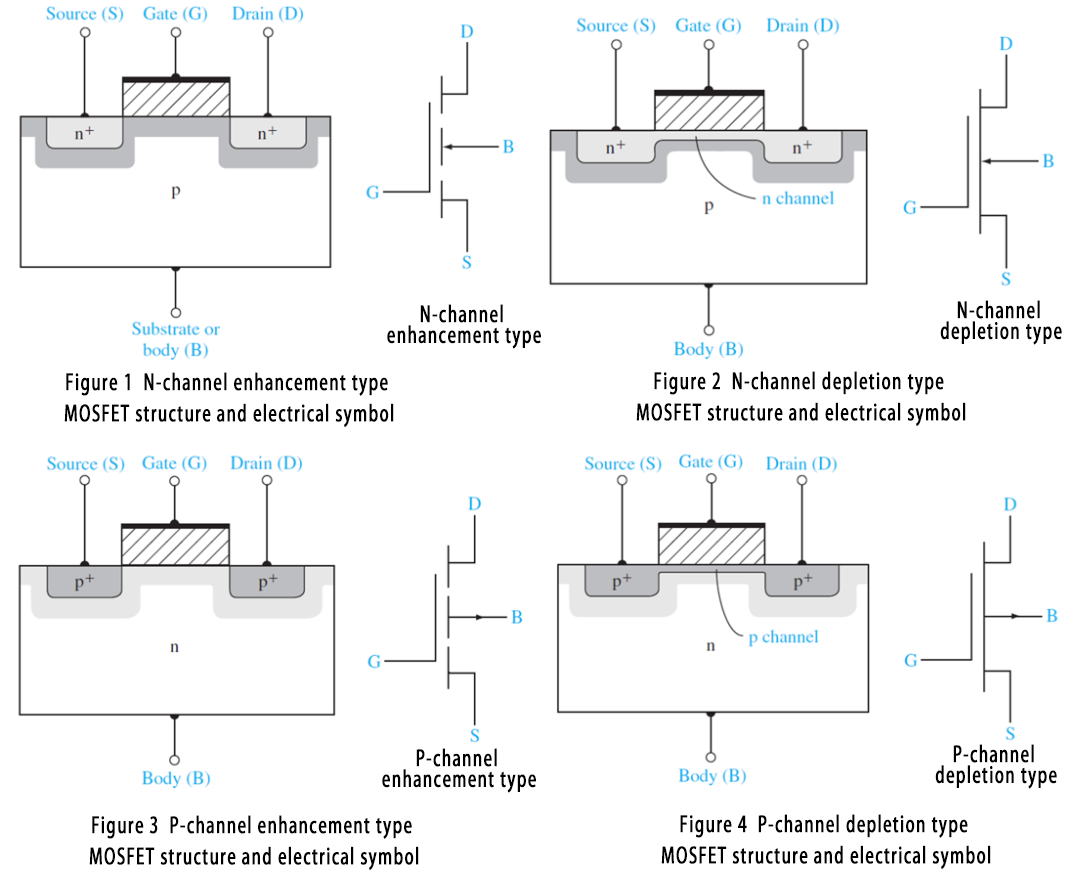

Metallum Oxide Semiconductor ager Transistor (Metal Oxide Semiconductor FET), id est, effectus campi transistoris qui transitum moderantis semiconductoris (S) canalem conductivum applicando intentionem ad portam metallica (M-metal aluminii) et fons per iacum oxydatum (O-stratum SiO insulating) ad effectum campi electrici generandum. Cum porta et fons, et porta et siccatio a SiO2 insulating iacuit, MOSFET etiam porta insulata dicitur effectus ager transistor. Anno 1962, Bell Labs publice prosperum progressum nuntiavit, qui unus ex maximis miliaribus factus est in historia evolutionis semiconductoris et fundamentum technicum directe pro adventu semiconductoris memoriae posuit.

MOSFET dividi potest in canalem P et N iuxta alveum conductivum genus. Iuxta portam amplitudinis voltage, dividi potest in: deperditionem type-cum portae intentione nulla est, canalis conductivus est inter exhaurire et fontem; amplificationem type-pro N (P) canalis machinas, canalis conductivus solum est cum porta intentione maior est quam (minus quam) nulla, et potentia MOSFET maxime N canalis amplificationis genus est.

Differentiae principales inter MOS et triodum includunt sed non limitantur ad sequentia puncta;

-Triodes machinae sunt bipolae, quia et maioritas et minoritas portantes conductionem simul participant; dum MOS solum electricitatem per plures tabellarios in semiconductores agit, et etiam unipolaris transistor appellatur.

-Triodes sunt machinae hodiernae continentes cum potentia consummationis relative alta; MOSFETs autem cogitationes intentione moderatae sunt consummatio virtutis inferioris.

-Triodes magnas habent resistentias, dum MOS fistulae parvae contra resistentiam habent, pauci centum millium. In vigente electrica machinis, MOS fistulae plerumque ut virgas adhibentur, maxime quia efficientia MOS relative alta est ad triodes comparata.

-Triodes secundum commodum sumptus habent, et MOS fistulae inter se carae sunt.

-Nunc in plerisque missionibus MOS fistulae triodes reponere solent. In missionibus quibusdam humilibus potentiae vel potentiae insensibilibus tantum, triodis utemur pro pretii commodo.

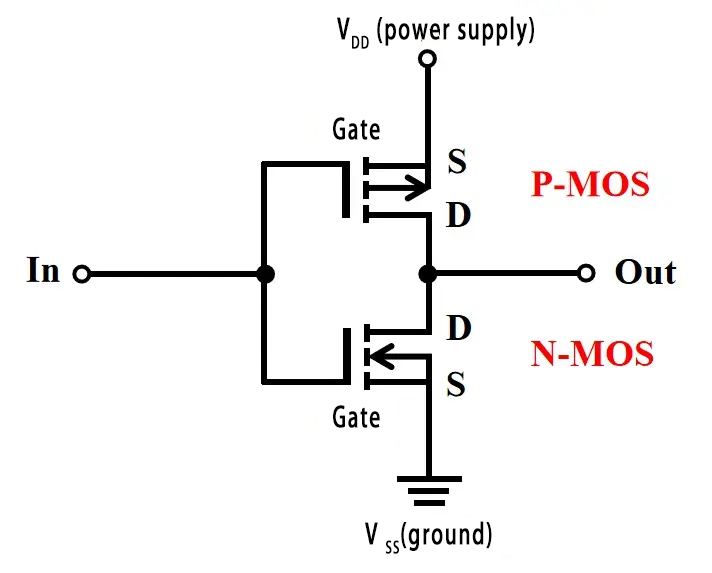

3. CMOS

Metallum oxydatum complementarium semiconductor: CMOS technologia p-typo complementario utitur et n-type oxydi metalli semiconductoris transistores (MOSFETs) ad electronicas cogitationes et circuitus logicas aedificandas. Sequens figura ostendit communem CMOS invertentem, quae ad conversionem "0 → 0" vel "0 →1" adhibetur.

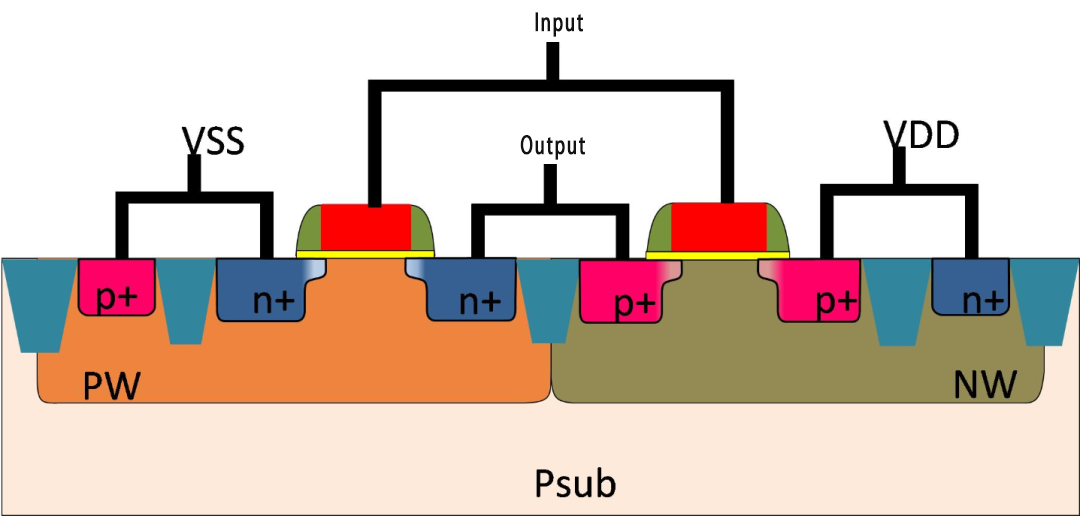

Sequens figura CMOS sectioni crucis typica est. Laevum latus est NMS, dextrum latus est PMOS. G poli duorum MOS ut communi portae input connexae, et D poli ut communis exhauriunt connexae. VDD fonti PMOS iungitur, et VSS cum fonte NMOS coniungitur.

Anno 1963, Wanlass et Sah de Fairchild Semiconductor CMOS ambitum invenerunt. Anno 1968, in American Radio Corporation (RCA) primum CMOS productum ambitus integratus ampliavit, et ex eo ambitu CMOS magnam progressionem consecutus est. Commoda eius sunt humilis potentia consummatio et integratio alta (STI/LOCO processus integrationem amplius emendare potest); incommodum eius est exsistentia effectus cincinnis (PN connexio transversa, bias solitaria inter tubulas MOS adhibenda, et impedimentum facile augeri potest ansam et ambitum urere).

4. DMOS

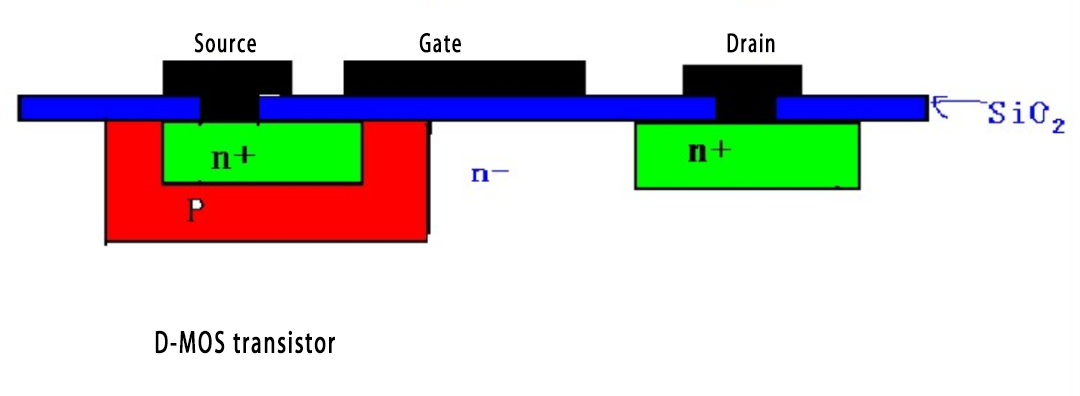

Metallum oxydatum duplicatum semiconductorem: MOSFET instrumentorum vulgarium similis structurae, etiam fontem, exhaurire, portam et alia electrodes habet, sed rupturae intentione exhauriendi finis altus est. Duplex processus diffusio adhibetur.

Figura infra sectionem crucis vexillum N-alvei DMOS ostendit. Hoc genus machinae DMOS in applicationibus mutandi in humili latere solet, ubi fons MOSFET cum terra coniungitur. Est praeterea alveum P DMOS. Hoc genus machinae DMOS in applicationibus mutandi in summo latere solet, ubi fons MOSFET cum positivo intentione coniungitur. Similia cum CMOS, DMOS complementis machinis N-canali et P-alvei MOSFETs in eodem chip utuntur ad functiones commutationes complementarias praebendas.

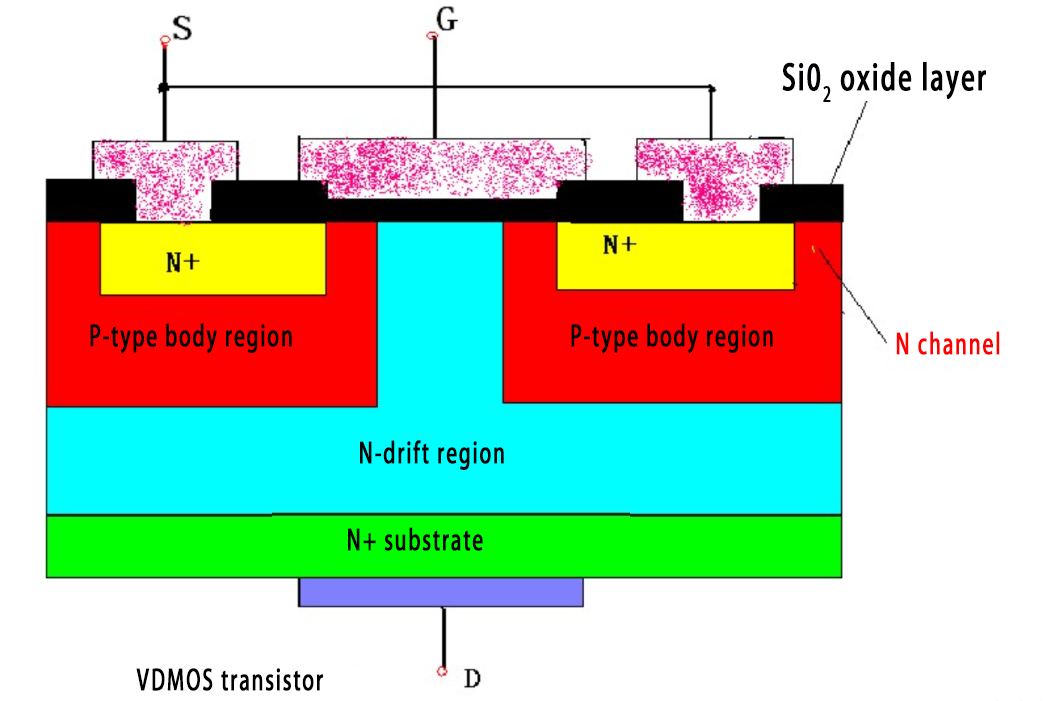

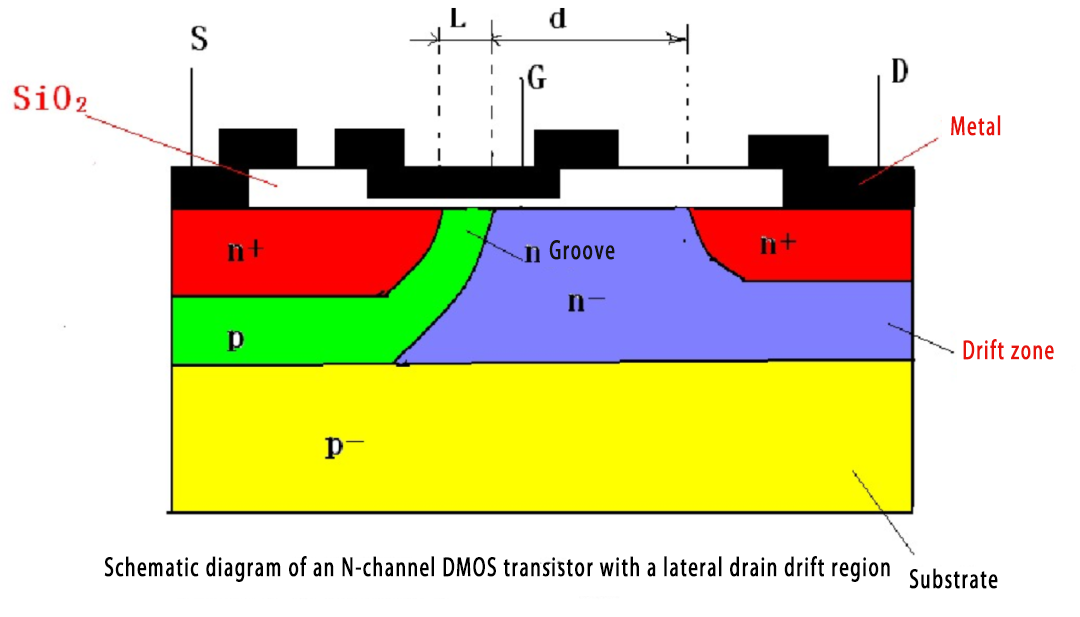

Secundum directionem canalis, DMOS in duo genera dividi potest, nempe verticalis oxydatis metalli duplicati semiconductoris effectus transistoris VDMOS (Dum Diffusi MOSFET verticalis) et oxydatus metallicus lateralis duplicatus effectus semiconductoris campi transistoris LDMOS (Duplex lateralis. -DiFFUSA MOSFET).

VDMOS cogitationes cum canali verticali designantur. Cum lateralibus DMOS machinis comparati, altiora intentione naufragii et venae facultates tractantes habent, sed in-resistentia relative magna adhuc est.

LDMOS cogitationes cum canali laterali designantur et sunt asymmetrica potentia MOSFET machinis. Cum machinis verticalibus DMOS comparati, resistentiam inferiorem et velocitates mutandi velociores permittunt.

Cum MOSFETs traditionalibus comparatus, DMOS in facultatem et inferiorem resistentiam superiorem habet, in electronicis cogitationibus alta potentia ita late adhibetur ut virgas potentiae, instrumenta potentiae et vehiculum electricum impellit.

5. BiCMOS

Bipolar CMOS technicae artis est quae CMOS et bipolaris machinas in eodem chip simul integrat. Eius idea fundamentalis est ut CMOS machinis circa ambitum unitatis principale, et machinas bipolares vel circuitus adiicere, ubi magnae capacitivae onera adigenda requiruntur. Ergo, circuitus BiCMOS utilitates habent altae integrationis et humilis potentiae consumptio circulorum CMOS, et commoda altae celeritatis et validae currentis curriculi facultates incessus BJT.

STMicroelectronics' BiCMOS Sige technologiae (pii germanium) technologiam RF, analogum et digitales partes in unum chippis integrat, quae signanter numerum partium externarum et consummationis potentiae optimize minuere potest.

6. BCD

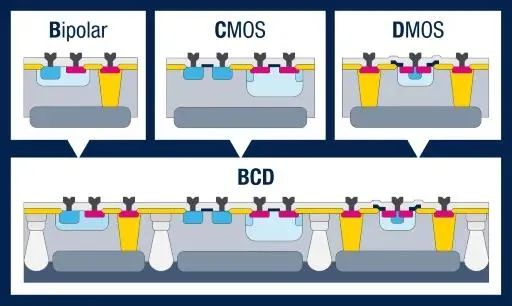

Bipolar-CMOS-DMOS, haec technologia bipolar, CMOS et DMOS machinas in eodem chip facere potest, qui processum BCD appellavit, qui primum a STMicroelectronics (ST) anno 1986 feliciter evolutus est.

Bipolar est aptus circulis analogis, CMOS aptus circulis digitalibus et logicis, et DMOS aptus ad potentiam et altas cogitationes. commoda BCD tria coniungit. Post continuam emendationem, BCD late usus est in productis in agris potentiae administratione, analogia notitia acquisitionis et actuum potentiarum. Secundum ST rutrum, matura processus pro BCD adhuc circa 100nm est, 90nm adhuc in prototypo designatur, et technologia 40nmBCD ad fructus generationis proximos sub evolutione pertinet.

Post tempus: Sep-10-2024