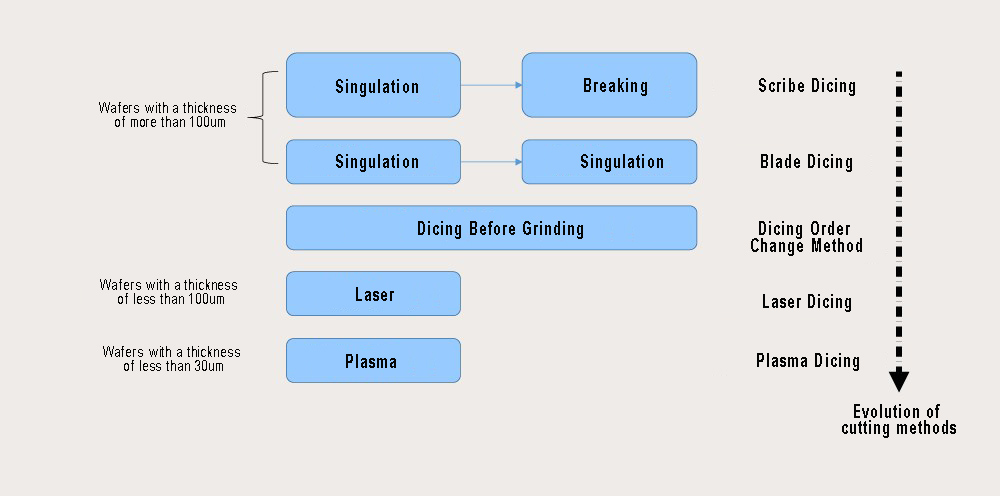

A waferdeve passare attraverso tre cambiamenti per diventare un vero chip semiconduttore: in primo luogo, il lingotto a forma di blocco viene tagliato in wafer; nel secondo processo, i transistor vengono incisi sulla parte anteriore del wafer attraverso il processo precedente; infine, viene eseguito il confezionamento, cioè, attraverso il processo di taglio, ilwaferdiventa un chip semiconduttore completo. Si può osservare che il processo di confezionamento appartiene al processo di back-end. In questo processo, il wafer verrà tagliato in diversi chip individuali a forma di esaedro. Questo processo per ottenere chip indipendenti è chiamato "Singulazione", e il processo di taglio della piastra del wafer in cuboidi indipendenti è chiamato "taglio del wafer (Die Sawing)". Recentemente, con il miglioramento dell'integrazione dei semiconduttori, lo spessore dicialdeè diventato sempre più sottile, il che ovviamente comporta molte difficoltà al processo di "singolazione".

L'evoluzione del taglio a cubetti dei wafer

I processi front-end e back-end si sono evoluti attraverso l'interazione in vari modi: l'evoluzione dei processi back-end può determinare la struttura e la posizione dei piccoli chip esaedrici separati dal dado sulwafer, così come la struttura e la posizione dei pad (percorsi di collegamento elettrico) sul wafer; al contrario, l'evoluzione dei processi front-end ha modificato il processo e il metodo diwaferassottigliamento del dorso e "taglio a dado" nel processo di back-end. Pertanto, l'aspetto sempre più sofisticato della confezione avrà un impatto significativo sul processo di back-end. Inoltre, anche il numero, la procedura e il tipo di taglio a dado cambieranno di conseguenza, in base al cambiamento nell'aspetto della confezione.

Scribe Dicing

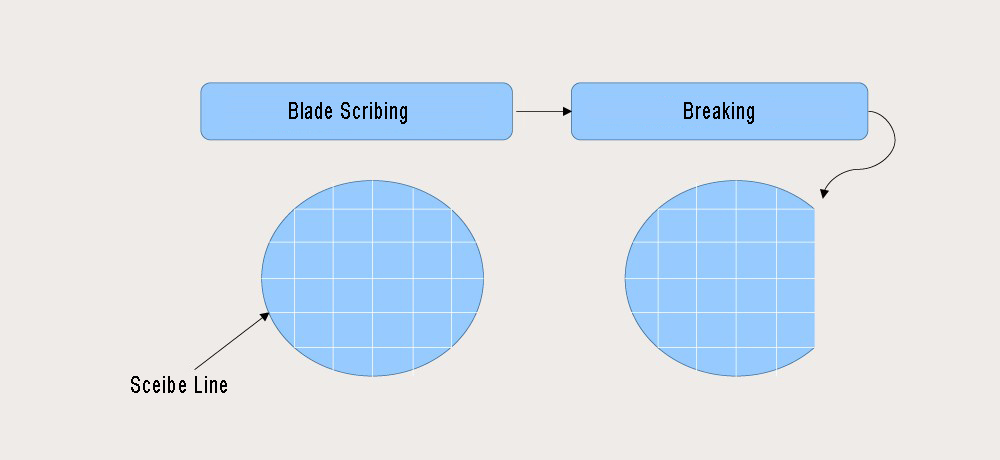

Nei primi tempi, “rompere” applicando una forza esterna era l’unico metodo di taglio che poteva dividere ilwaferin stampi esaedrici. Tuttavia, questo metodo presenta lo svantaggio di scheggiature o crepe sul bordo del piccolo truciolo. Inoltre, poiché le bave sulla superficie metallica non vengono completamente rimosse, la superficie di taglio risulta anche molto ruvida.

Per risolvere questo problema è nato il metodo di taglio “Scribing”, cioè prima di “rompere” la superficie delwaferviene tagliato a circa metà della profondità. "Scribing", come suggerisce il nome, si riferisce all'utilizzo di una girante per segare (tagliare a metà) in anticipo il lato anteriore del wafer. Inizialmente, la maggior parte dei wafer inferiori a 15 cm utilizzava questo metodo di taglio, che consisteva prima nel "tagliare" i chip e poi nel "romperli".

Taglio a cubetti o taglio a sega

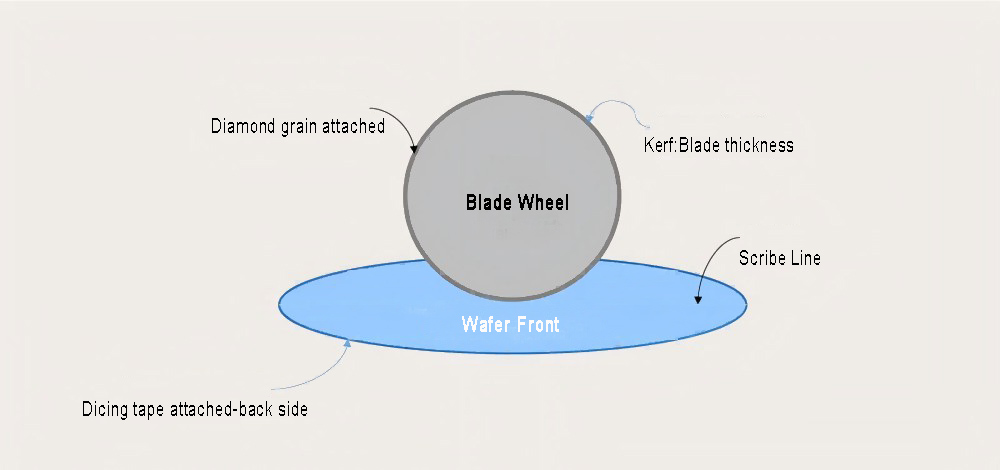

Il metodo di taglio "a incisione" si è gradualmente evoluto nel metodo di taglio "a cubetti" (o segatura), che prevede il taglio con una lama per due o tre volte consecutive. Il metodo di taglio "a cubetti" può compensare il fenomeno del distacco di piccoli trucioli durante la "rottura" dopo la "incisione" e può proteggerli durante il processo di "singolatura". Il taglio "a cubetti" è diverso dal precedente taglio "a cubetti", ovvero dopo un taglio "a cubetti" non si verifica una "rottura", ma un nuovo taglio con una lama. Per questo motivo, viene anche chiamato metodo "a cubetti a gradini".

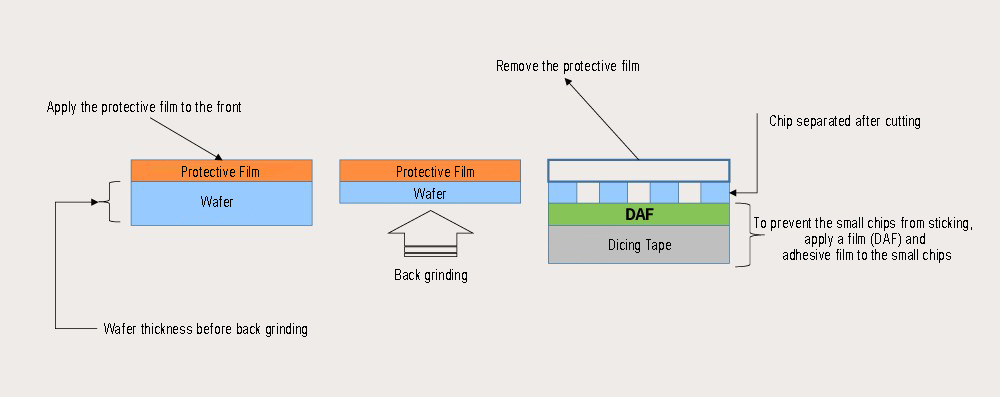

Per proteggere il wafer da danni esterni durante il processo di taglio, verrà applicata una pellicola preliminare per garantire un "singling" più sicuro. Durante il processo di "retro rettifica", la pellicola verrà applicata alla parte anteriore del wafer. Al contrario, nel taglio "a lama", la pellicola dovrebbe essere applicata alla parte posteriore del wafer. Durante il die bonding eutettico (il die bonding, ovvero il fissaggio dei chip separati sul PCB o sul telaio fisso), la pellicola applicata alla parte posteriore cadrà automaticamente. A causa dell'elevato attrito durante il taglio, è necessario spruzzare acqua deionizzata in modo continuo da tutte le direzioni. Inoltre, la girante dovrebbe essere fissata con particelle di diamante per migliorare il taglio delle fette. In questa fase, il taglio (spessore della lama: larghezza della scanalatura) deve essere uniforme e non deve superare la larghezza della scanalatura di taglio.

Per lungo tempo, la segatura è stata il metodo di taglio tradizionale più utilizzato. Il suo principale vantaggio è la possibilità di tagliare un gran numero di wafer in breve tempo. Tuttavia, aumentando notevolmente la velocità di avanzamento della fetta, aumenta anche il rischio di distacco dei bordi dei chip. Pertanto, il numero di rotazioni della girante deve essere controllato a circa 30.000 volte al minuto. Come si può osservare, la tecnologia di processo dei semiconduttori è spesso un segreto accumulato lentamente attraverso un lungo periodo di accumulo e tentativi ed errori (nella prossima sezione sul legame eutettico, discuteremo i contenuti relativi al taglio e al DAF).

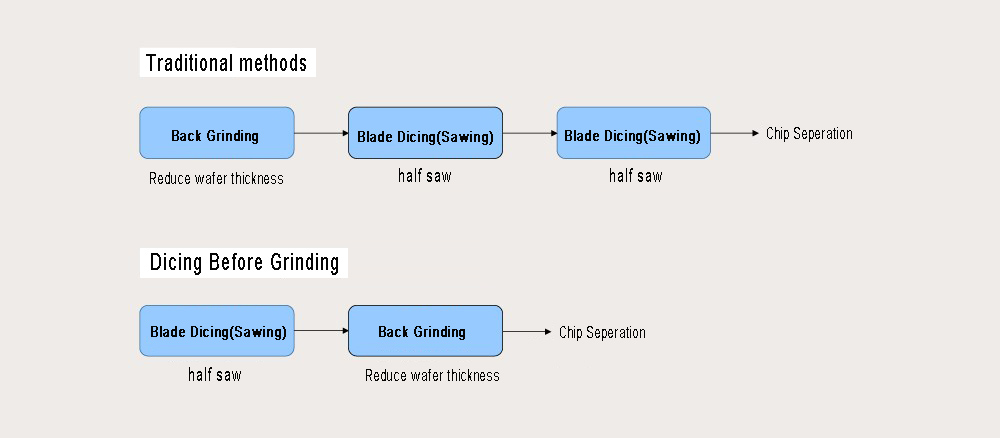

Taglio a cubetti prima della macinazione (DBG): la sequenza di taglio ha cambiato il metodo

Quando si esegue il taglio a lama su un wafer di 8 pollici di diametro, non c'è bisogno di preoccuparsi di sbucciature o crepe sui bordi dei chiplet. Tuttavia, man mano che il diametro del wafer aumenta fino a 21 pollici e lo spessore diventa estremamente sottile, i fenomeni di sbucciatura e crepe ricominciano a manifestarsi. Per ridurre significativamente l'impatto fisico sul wafer durante il processo di taglio, il metodo DBG di "taglio a cubetti prima della macinatura" sostituisce la tradizionale sequenza di taglio. A differenza del tradizionale metodo di taglio a "lama" che taglia in continuo, il DBG esegue prima un taglio a "lama" e poi assottiglia gradualmente lo spessore del wafer assottigliando continuamente il lato posteriore fino a spaccare il chip. Si può affermare che il DBG sia una versione aggiornata del precedente metodo di taglio a "lama". Grazie alla possibilità di ridurre l'impatto del secondo taglio, il metodo DBG si è rapidamente diffuso nel "packaging a livello di wafer".

Taglio laser a dadi

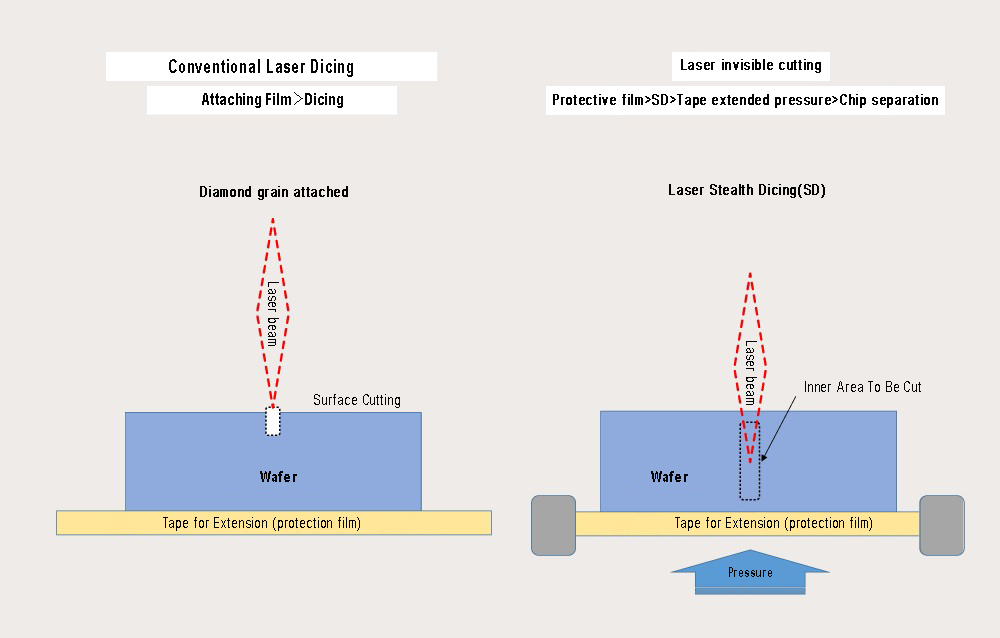

Il processo WLCSP (wafer-level chip scale package) utilizza principalmente il taglio laser. Il taglio laser può ridurre fenomeni come peeling e cracking, ottenendo così chip di migliore qualità, ma quando lo spessore del wafer è superiore a 100 μm, la produttività sarà notevolmente ridotta. Pertanto, viene utilizzato principalmente su wafer con spessore inferiore a 100 μm (relativamente sottili). Il taglio laser taglia il silicio applicando un laser ad alta energia alla scanalatura di incisione del wafer. Tuttavia, quando si utilizza il metodo di taglio laser convenzionale (laser convenzionale), è necessario applicare preventivamente una pellicola protettiva sulla superficie del wafer. Poiché il riscaldamento o l'irradiazione della superficie del wafer con il laser, questi contatti fisici produrranno delle scanalature sulla superficie del wafer e i frammenti di silicio tagliati aderiranno anche alla superficie. Si può osservare che anche il metodo di taglio laser tradizionale taglia direttamente la superficie del wafer e, in questo senso, è simile al metodo di taglio "a lama".

Lo Stealth Dicing (SD) è un metodo che prevede il taglio laser della parte interna del wafer, per poi applicare una pressione esterna al nastro adesivo sul retro del wafer per romperlo e separare il chip. Quando si applica una pressione al nastro adesivo sul retro, il wafer viene immediatamente sollevato verso l'alto a causa dell'allungamento del nastro, separando così il chip. I vantaggi dello Stealth Dicing rispetto al tradizionale metodo di taglio laser sono: in primo luogo, non ci sono detriti di silicio; in secondo luogo, il kerf (la larghezza della scanalatura di incisione) è ridotto, consentendo di ottenere un maggior numero di chip. Inoltre, il metodo SD riduce notevolmente i fenomeni di peeling e cracking, un fattore cruciale per la qualità complessiva del taglio. Pertanto, è molto probabile che il metodo SD diventi la tecnologia più diffusa in futuro.

Taglio al plasma

Il taglio al plasma è una tecnologia di recente sviluppo che utilizza l'incisione al plasma per tagliare durante il processo di produzione (Fab). Il taglio al plasma utilizza materiali semigassosi anziché liquidi, quindi l'impatto ambientale è relativamente ridotto. Inoltre, il metodo di taglio dell'intero wafer in un'unica operazione consente una velocità di "taglio" relativamente elevata. Tuttavia, il metodo al plasma utilizza un gas di reazione chimica come materia prima e il processo di incisione è molto complesso, quindi il flusso di processo risulta relativamente macchinoso. Tuttavia, rispetto al taglio a "lama" e al taglio laser, il taglio al plasma non danneggia la superficie del wafer, riducendo così il tasso di difettosità e ottenendo un maggior numero di trucioli.

Recentemente, poiché lo spessore del wafer è stato ridotto a 30 μm e si utilizza molto rame (Cu) o materiali a bassa costante dielettrica (Low-k), anche i metodi di taglio al plasma saranno favoriti per prevenire la formazione di bave (Burr). Naturalmente, anche la tecnologia del taglio al plasma è in costante sviluppo. Credo che nel prossimo futuro non sarà più necessario indossare una maschera speciale durante l'incisione, perché questa è una delle principali direzioni di sviluppo del taglio al plasma.

Con la continua riduzione dello spessore dei wafer da 100 μm a 50 μm e poi a 30 μm, anche i metodi di taglio per ottenere chip indipendenti sono cambiati e si sono evoluti, passando dal taglio a "rottura" e a "lama" al taglio laser e al taglio al plasma. Sebbene i metodi di taglio sempre più evoluti abbiano aumentato i costi di produzione del processo di taglio stesso, d'altra parte, riducendo significativamente fenomeni indesiderati come peeling e cracking che spesso si verificano nel taglio dei chip dei semiconduttori e aumentando il numero di chip ottenuti per unità di wafer, il costo di produzione di un singolo chip ha mostrato una tendenza al ribasso. Naturalmente, l'aumento del numero di chip ottenuti per unità di area del wafer è strettamente correlato alla riduzione della larghezza della sezione di taglio. Con il taglio al plasma, è possibile ottenere quasi il 20% di chip in più rispetto al taglio a "lama", che è anche uno dei motivi principali per cui le persone scelgono il taglio al plasma. Con lo sviluppo e i cambiamenti dei wafer, dell'aspetto dei chip e dei metodi di confezionamento, stanno emergendo anche vari processi di taglio, come la tecnologia di lavorazione dei wafer e il DBG.

Data di pubblicazione: 10-ott-2024