Kio estas BCD-procezo?

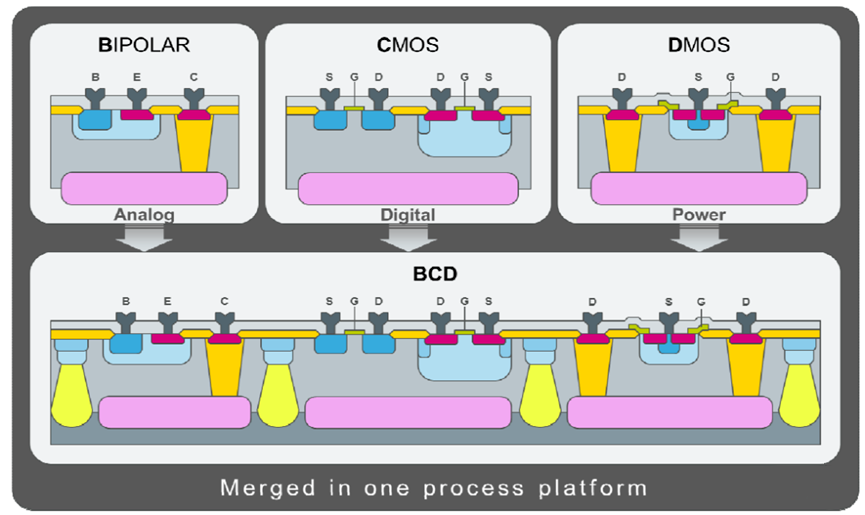

BCD-procezo estas unu-ĉipa integra procezteknologio unue enkondukita de ST en 1986. Ĉi tiu teknologio povas krei dupolusajn, CMOS kaj DMOS aparatojn sur la sama ĉipo. Ĝia aspekto multe reduktas la areon de la ĉipo.

Oni povas diri, ke la BCD-procezo plene utiligas la avantaĝojn de dupolusa stirkapablo, alta integriĝo kaj malalta energikonsumo de CMOS, kaj alta tensio kaj alta kurentfluokapacito de DMOS. Inter ili, DMOS estas la ŝlosilo por plibonigi potencon kaj integriĝon. Kun la plua disvolviĝo de integracirkvita teknologio, la BCD-procezo fariĝis la ĉefa fabrikada teknologio de PMIC.

Transversa diagramo de la BCD-procezo, fontreto, dankon

Avantaĝoj de BCD-procezo

La BCD-procezo kreas dupolusajn aparatojn, CMOS-aparatojn kaj DMOS-potencajn aparatojn sur la sama ĉipo samtempe, integrante la altan transkonduktancon kaj fortan ŝarĝo-stiran kapablon de dupolusaj aparatoj kaj la altan integriĝon kaj malaltan energikonsumon de CMOS, tiel ke ili povas kompletigi unu la alian kaj plene utiligi siajn respektivajn avantaĝojn; samtempe, DMOS povas funkcii en ŝaltilreĝimo kun ekstreme malalta energikonsumo. Mallonge, malalta energikonsumo, alta energiefikeco kaj alta integriĝo estas unu el la ĉefaj avantaĝoj de BCD. La BCD-procezo povas signife redukti energikonsumon, plibonigi sisteman rendimenton kaj havi pli bonan fidindecon. La funkcioj de elektronikaj produktoj kreskas ĉiutage, kaj la postuloj pri tensioŝanĝoj, kondensatora protekto kaj plilongigo de la bateria vivo fariĝas ĉiam pli gravaj. La altrapidaj kaj energiŝparaj karakterizaĵoj de BCD plenumas la procezajn postulojn por alt-efikecaj analogaj/potencadministradaj ĉipoj.

Ŝlosilaj teknologioj de BCD-procezo

Tipaj aparatoj de BCD-procezo inkluzivas malalt-tensiajn CMOS, alt-tensiajn MOS-tubojn, LDMOS kun diversaj kolapsaj tensioj, vertikalajn NPN/PNP kaj Schottky-diodojn, ktp. Kelkaj procezoj ankaŭ integras aparatojn kiel JFET kaj EEPROM, rezultante en granda vario de aparatoj en BCD-procezo. Tial, krom konsideri la kongruecon de alt-tensiaj aparatoj kaj malalt-tensiaj aparatoj, duobla-klakaj procezoj kaj CMOS-procezoj, ktp. en la dezajno, oni devas ankaŭ konsideri taŭgan izoladteknologion.

En BCD-izoliga teknologio, multaj teknologioj kiel krucvoja izolado, mem-izolado kaj dielektrika izolado aperis unu post alia. Krucvoja izola teknologio celas fabriki la aparaton sur la N-tipa epitaksa tavolo de la P-tipa substrato kaj uzi la inversajn biasajn karakterizaĵojn de la PN-krucvojo por atingi izoladon, ĉar la PN-krucvojo havas tre altan reziston sub inversa biaso.

Mem-izolita teknologio estas esence PN-transira izolado, kiu dependas de la naturaj PN-transiraj karakterizaĵoj inter la fontaj kaj drenilaj regionoj de la aparato kaj la substrato por atingi izoladon. Kiam la MOS-tubo estas ŝaltita, la fonta regiono, drenila regiono kaj kanalo estas ĉirkaŭitaj de la malpleniga regiono, formante izoladon de la substrato. Kiam ĝi estas malŝaltita, la PN-transiro inter la drenila regiono kaj la substrato estas inverse polarigita, kaj la alta tensio de la fonta regiono estas izolita de la malpleniga regiono.

Dielektra izolado uzas izolajn mediojn kiel silician oksidon por atingi izoladon. Bazite sur dielektra izolado kaj krucvoja izolado, kvazaŭdielektra izolado estis evoluigita kombinante la avantaĝojn de ambaŭ. Per selektema adopto de la supre menciita izolada teknologio, oni povas atingi kongruecon inter alta tensio kaj malalta tensio.

Evoluiga direkto de BCD-procezo

La disvolviĝo de BCD-proceza teknologio ne similas al la norma CMOS-procezo, kiu ĉiam sekvis la leĝon de Moore por disvolviĝi en la direkto de pli malgranda linilarĝo kaj pli rapida rapideco. La BCD-procezo estas malglate diferencigita kaj disvolvita en tri direktoj: alta tensio, alta potenco kaj alta denseco.

1. Altatensia BCD-direkto

Alt-tensia BCD povas samtempe fabriki alt-fidindajn malalt-tensiajn stirajn cirkvitojn kaj ultra-alt-tensiajn DMOS-nivelajn cirkvitojn sur la sama ĉipo, kaj povas realigi la produktadon de 500-700V alt-tensiaj aparatoj. Tamen, ĝenerale, BCD ankoraŭ taŭgas por produktoj kun relative altaj postuloj por potencaj aparatoj, precipe BJT aŭ alt-kurentaj DMOS-aparatoj, kaj povas esti uzata por potenc-kontrolo en elektronika lumigado kaj industriaj aplikoj.

La nuna teknologio por fabrikado de alttensia BCD estas la RESURF-teknologio proponita de Appel kaj aliaj en 1979. La aparato estas farita uzante malpeze dopitan epitaksian tavolon por igi la surfacan elektran kampodistribuon pli plata, tiel plibonigante la surfacajn disrompajn karakterizaĵojn, tiel ke la disrompo okazas en la korpo anstataŭ la surfaco, tiel pliigante la disrompan tension de la aparato. Malpeza dopado estas alia metodo por pliigi la disrompan tension de BCD. Ĝi ĉefe uzas duoblan difuzan drenilon DDD (duobla Dopa Drenilo) kaj malpeze dopitan drenilon LDD (malpeze Dopa Drenilo). En la DMOS-drenila regiono, N-tipa driva regiono estas aldonita por ŝanĝi la originalan kontakton inter la N+ drenilo kaj la P-tipa substrato al kontakto inter la N- drenilo kaj la P-tipa substrato, tiel pliigante la disrompan tension.

2. Alt-potenca BCD-direkto

La tensio-intervalo de alt-potenca BCD estas 40-90V, kaj ĝi estas ĉefe uzata en aŭtomobila elektroniko, kiu postulas alt-kurentan stirkapablon, mezan tension kaj simplajn stircirkvitojn. Ĝiaj postulkarakterizaĵoj estas alt-kurentan stirkapablo, meza tensio, kaj la stircirkvito ofte estas relative simpla.

3. Alt-denseca BCD-direkto

Alt-denseca BCD, la tensio-intervalo estas 5-50V, kaj iuj aŭtomobilaj elektronikaĵoj atingos 70V. Pli kaj pli kompleksaj kaj diversaj funkcioj povas esti integritaj sur la sama peceto. Alt-denseca BCD adoptas kelkajn modulajn dezajnajn ideojn por atingi produktodiversigon, ĉefe uzata en aŭtomobilaj elektronikaj aplikoj.

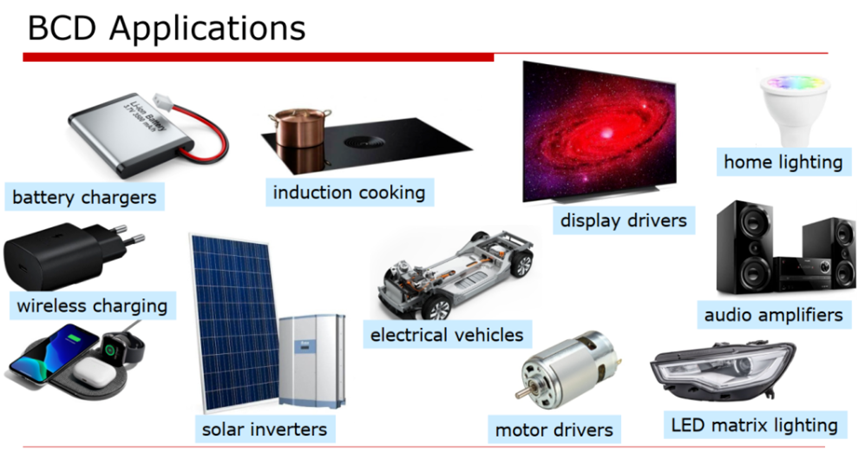

Ĉefaj aplikoj de BCD-procezo

La BCD-procezo estas vaste uzata en energiadministrado (potenco- kaj baterio-kontrolo), ekran-diskoj, aŭtomobila elektroniko, industria kontrolo, ktp. Potencadministra blato (PMIC) estas unu el la gravaj tipoj de analogaj blatoj. La kombinaĵo de la BCD-procezo kaj SOI-teknologio ankaŭ estas grava trajto de la disvolviĝo de la BCD-procezo.

VET-Ĉinio povas provizi grafitajn partojn, molrigidan felton, siliciajn karbidajn partojn, cvD-siliciajn karbidajn partojn, kaj sic/Tac-kovritajn partojn ene de 30 tagoj.

Se vi interesiĝas pri la supre menciitaj duonkonduktaĵaj produktoj, bonvolu ne heziti kontakti nin unuafoje.

Telefono: +86-1891 1596 392

WhatsApp: 86-18069021720

Retpoŝto:yeah@china-vet.com

Afiŝtempo: 18-a de septembro 2024